# (CELIOURNAL INSERS

THE AUTHORITATIVE JOURNAL FOR PROGRAMMABLE LOGIC USERS

### **Special Edition**

**Achieving Breakthrough Performance** at the Lowest Cost

EDITOR IN CHIEF

Carlis Collins editor@xilinx.com 408-879-4519

MIANAGING EDITOR

Forrest Couch forrest couch@xilinx.com 408-879-5270

ASSISTANT MANAGING EDITOR Charmaine Cooper Hussain

XCELL ONLINE EDITOR

Tom Pyles tom.pyles@xilinx.com 720-652-3883

ADVERTISING SALES

Dan Teie 1-800-493-5551

ART DIRECTOR

Scott Blair

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124-3400 Phone: 408-559-7778 FAX: 408-879-4780

© 2005 Xilinx, Inc. All rights reserved. XIUNX, the Xilinx Logo, and otherdesignated brands included herein are hademarks of Xilinx, Inc. PowerPC is a hademark of IBM, Inc. All other trademarks are the property of their respective owners.

The articles, information, and other materials included in this issue are provided solely for the convenience of our readers. Xilinx makes no warranties, express, implied, statutiony, or otherwise, and accepts no liability with respect to any such articles, information, or other materials or their use, and any use thereof is solely at the risk of the user. Any person ore nithy using such information in any way releases and waites any claim it might hove against Xilinx for any loss, damage, or expense caused thereby.

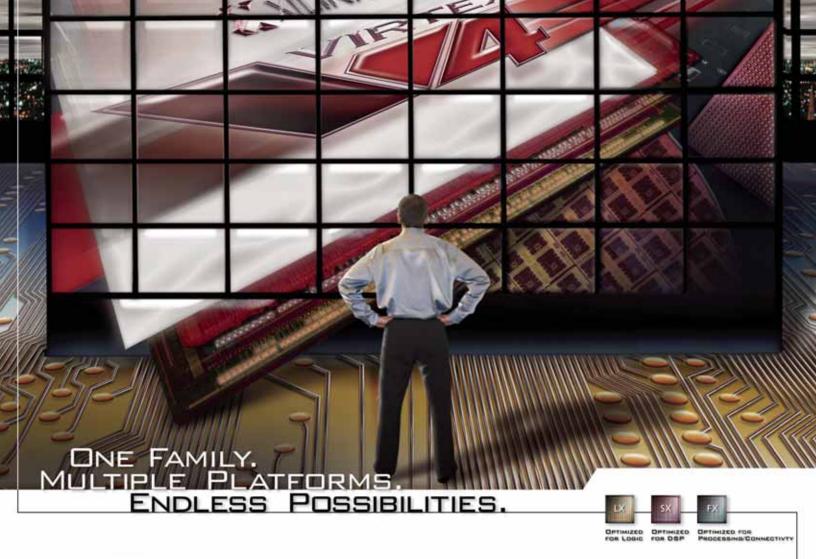

### Continuing Excellence

In case you haven't heard, Xilinx recently announced its new Virtex-4<sup>TM</sup> family of FPGAs. In this special edition of *Xcell Journal*, you'll find articles devoted exclusively to Virtex-4 business viewpoints, system design challenges, engineering solutions, and engineering references.

Our "View from the Top" article is by Erich Goetting, Xilinx Vice President and General Manager of the Advanced Products Division. Erich presents an overview of the new Virtex-4 family, and gives you a guided tour of some of the new Virtex-4 technologies, as well as the inspiration and rationale behind them. Other articles in the Business Viewpoint section discuss how these new Virtex-4 devices, based on 90 nm technology, have greatly expanded high-performance processing and system integration.

You'll also find technical articles written by Xilinx marketing, applications, and development staff, as well as our partners and customers, including:

- System Design Challenges articles emphasize the Virtex-4 family advantages and leadership themes. These technical articles outline design challenges and demonstrate how the Virtex-4 solution addresses these challenges.

- Engineering Solutions articles demonstrate some of the key capabilities of Virtex-4 FPGAs and how they are used in a design. These articles provide in-depth descriptions of Virtex-4 features, IP, and tools.

- The Engineering Reference section describes some of the Virtex-4 hardware development platforms and other design solutions, to help you determine which platform is best for your application and design task.

### It's Time to Re-Subscribe

This issue marks the 16th anniversary of our *Xcell Journal*. From its humble beginnings in the fourth quarter of 1988 as an eight-page, two-color newsletter, the journal has grown into an award-winning publication printed in five languages and distributed in 144 countries with a circulation of more than 60,000 readers.

Periodically, we must clean our mailing database. Beginning January 1, 2005, you must re-subscribe to continue receiving the *Xcell Journal* FREE. If you subscribed after January 1, 2005, you do not have to re-subscribe. If you subscribed before this date, please visit our site at *www.xilinx.com/xcell/subscribe* and take a minute to renew your FREE subscription and ensure its uninterrupted delivery.

I want to thank all of you, our readers, for your continued interest and support of the *Xcell Journal*. Please feel free to drop me a note at *xcell@xilinx.com* about your suggestions on how we may improve. I'd like to hear from you.

Forest Couch

Forrest Couch Managing Editor

This section discusses how the new Virtex-4 devices, based on 90 nm technology, have greatly expanded high-performance processing and system integration.

VIEW FROM THE TOP

## Introducing the New Virtex-4 FPGA Family 6

This section emphasizes the Virtex-4 family advantages and leadership themes. These articles outline design challenges and demonstrate how the Virtex-4 solution addresses these challenges.

This section demonstrates some of the key capabilities of Virtex-4 FPGAs and how they are used in a design. These articles provide in-depth descriptions of Virtex-4 features, IP, and tools.

This section describes some of the Virtex-4 hardware development platforms and other design solutions, to help you determine which platform is best for your application and design task.

### FIRST QUARTER 2005, ISSUE 52

### Xcell journal

| View from the Top                                                                             | 6   |

|-----------------------------------------------------------------------------------------------|-----|

| DISCINITOS VIEWDOINTS                                                                         |     |

| BUSINESS VIEWPOINTS  Will the Evaluation of Districts FDCAs Mean the End for ASICs and ASSDs2 | 10  |

| Will the Evolution of Platform FPGAs Mean the End for ASICs and ASSPs?                        |     |

| EasyPath FPGAs Beat ASIC Prices                                                               | 12  |

| CYCTEM DECICAL CHALLENGES                                                                     |     |

| SYSTEM DESIGN CHALLENGES The Virtey A Power Play                                              | 1/  |

| The Virtex-4 Power Play                                                                       |     |

| Virtex-4 Memory Interfaces                                                                    |     |

| Designing with the Virtex-4 XtremeDSP Slice                                                   |     |

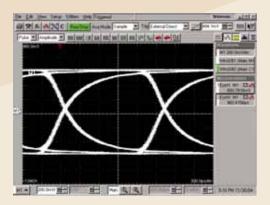

| Designing for Signal Integrity                                                                |     |

| Accelerated System Performance with APU-Enhanced Processing                                   |     |

| Solving the Signal Integrity Challenge                                                        |     |

| Using FPGAs in Wireless Base Station Designs                                                  |     |

| Implementing a Cable Modern Termination System                                                |     |

| Developing Next-Generation Telecommunication Networks                                         |     |

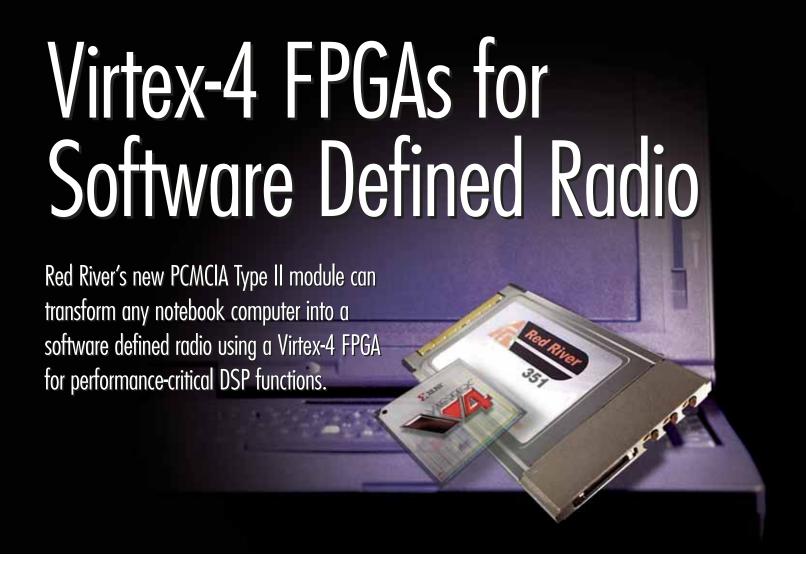

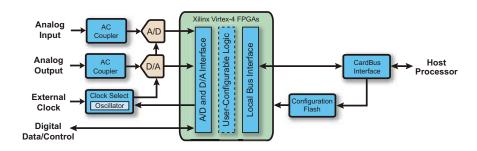

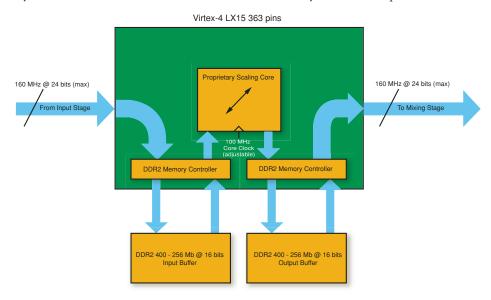

| Virtex-4 FPGAs for Software Defined Radio                                                     |     |

| Virtex-4 FPGAs in Rugged LCD Monitors                                                         |     |

|                                                                                               |     |

| ENGINEERING SOLUTIONS                                                                         |     |

| ISE 6.3 Software — Unleash the Power of Virtex-4 FPGAs                                        | 58  |

| FIFOs Made Easy                                                                               |     |

| Digital Clock Management                                                                      |     |

| Virtex-4 Clocking Resources                                                                   | 66  |

| Alpha Blending Two Data Streams Using a DSP48 Technique                                       |     |

| Dynamic Phase Alignment with ChipSync Technology                                              |     |

| Lock Your Design with the Virtex-4 Security Solution                                          |     |

| Dynamic Reconfiguration of Functional Blocks                                                  |     |

| Designing with Virtex-4 Embedded Tri-Mode Ethernet MAC                                        |     |

| Emerging Design Methodologies Elicit the Power of Virtex-4 FPGAs                              |     |

| Integrate EDK-Created Embedded Processor Subsystems                                           |     |

| Optimizing Virtex-4 High-Performance Designs                                                  |     |

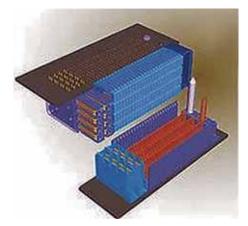

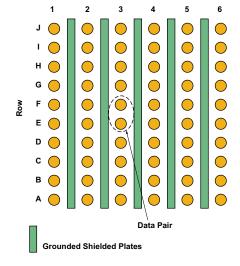

| Selecting Connectors for Multi-Gigabit Transceiver Designs                                    |     |

| Xilinx/Micron Partner to Provide High-Speed Memory Interfaces                                 |     |

| Harvesting the Flexibility of Virtex-4 Rocket10 Transceivers                                  |     |

| Optimize Memory Subsystem Performance with Network FCRAM                                      | 105 |

| GENERAL                                                                                       |     |

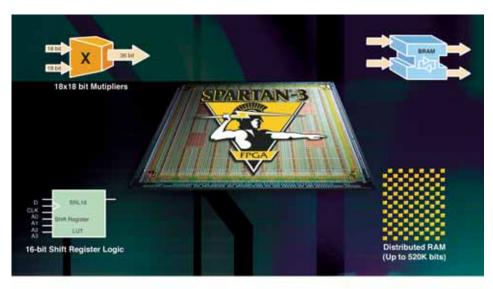

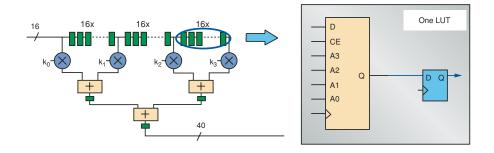

| Using Spartan-3 FPGAs to Implement High-Performance DSP                                       | 108 |

| osing Spatial 3 11 OAS to implement riigiri ettorniunce DSI                                   | 100 |

| ENGINEERING REFERENCES                                                                        |     |

| Virtex-4 ML401 Evaluation Platform                                                            | 112 |

| Virtex-4 FPGA Source-Synchronous Interfaces Design Kit                                        |     |

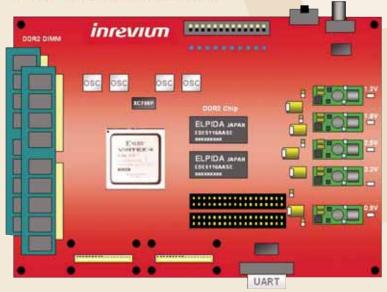

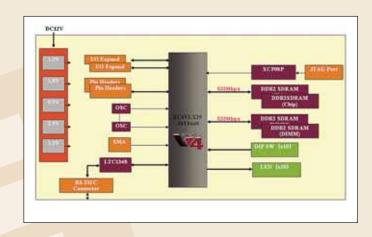

| Virtex-4 ML461 Advanced Memory Development System                                             |     |

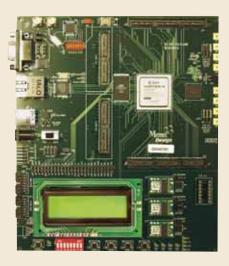

| Memec Virtex-4 Board Solutions                                                                |     |

| Avnet Virtex-4 Evaluation Kits                                                                |     |

| Nu Horizons Virtex-4 Development Platform                                                     |     |

| TED DDR2 Memory Evaluation Board                                                              |     |

|                                                                                               |     |

# Introducing the New Virtex-4 FPGA Family

The latest FPGAs from Xilinx set new records in capacity, capability, performance, power efficiency, and value.

by Erich Goetting

Vice President &

General Manager,

Advanced Products Division

Xilinx, Inc.

erich.goetting@xilinx.com

Welcome to the Xilinx® Virtex-4<sup>TM</sup> edition of the *Xcell Journal*. We've created this special issue to show you the new Virtex-4 FPGA family, and how its innovations enable the creation of next-generation systems that do more than ever thought possible only a few years ago.

In this article, I'll take you behind the scenes for a guided tour of some of the new technologies, as well as a bit of the inspiration and rationale behind them.

With more than 100 innovations, the Virtex-4 family represents a new milestone in the evolution of FPGA technology. After conducting extensive interviews with leading design engineers worldwide, we knew that they wanted the following things in an advanced next-generation FPGA family:

- Higher performance

- Higher logic density

- Lower power

- Lower cost

- More advanced capabilities

### At the heart of the Virtex-4 FPGA is our next-generation 90 nm triple-oxide 10-layer copper CMOS process technology.

It's relatively easy to deliver on one or two of these items – our challenge was to deliver all of them at the same time. We did this through a combination of innovative process and circuit design, process development, the ASMBL architectural approach, and the use of advanced embedded functions.

Development work on the Virtex-4 family (code-named "Whitney" after the highest mountain in the continental United States) began more than two years ago. It represents the creativity and dedication of hundreds of engineers, spanning integrated circuit design and layout, software and IP development, process development, testing and characterization, systems and applications engineering, technical documentation, and product marketing.

One of the most remarkable developments embodied in the new Virtex-4 FPGA family is the ASMBL architecture, which represents a fundamentally new way of constructing the FPGA floor plan and its interconnect to the package. First of all, ASMBL enables I/O pins, clock pins, and power and ground pins to be located anywhere on the silicon chip, not just along the periphery as with previous approaches. This in turn allows power and ground pins to be brought directly into the center of the silicon die, thereby significantly reducing on-chip IR drops that can occur with the largest FPGAs running at the highest frequencies.

Clock input pins are also located in the center of the die, which reduces clock latency. This is because clock networks need to have equal delay to all endpoints (that is, minimum skew), and thus the clock must emanate from the center. In periphery-connected clock input pins, the signal first traverses from the edge of the die to the center, and is then distributed to all regions. The Virtex-4 ASMBL design eliminates this traversal completely, and thus directly reduces the clock network propagation delay.

In addition to its electrical advantages, ASMBL provides another significant benefit in that it allows a more flexible – and thus more precise – allocation of on-chip resources.

That in turn has enabled us to offer Virtex-4 devices in three unique platforms, each with a different mix of on-chip resources:

- The LX platform, optimized for logic applications

- The SX platform, optimized for highend DSP applications

- The FX platform, optimized for embedded processing and high-speed serial applications

### A Look Inside the Virtex-4 FPGA

At the heart of the Virtex-4 FPGA is our next-generation 90 nm triple-oxide 10-layer copper CMOS process technology. While that's quite a lot of adjectives, every one of them is incredibly important. The first, 90 nm, refers to the "drawn" gate length of the smallest transistors. As transistors get smaller, they get faster, use less dynamic power, and enable higher complexity at lower price points. Chip designers think in terms of "transistor budgets," which are now in the billion transistor range.

### Triple-Oxide 90 nm CMOS Technology

Triple-oxide technology refers to the number of transistor oxide thicknesses available in the process. More oxide thicknesses allow more tuning of performance and power in the device circuitry, and enable Virtex-4 devices to deliver industry-leading performance while dramatically lowering power consumption.

One of our key inputs from many engineers was that performance and power were very important constraints in their systems designs, and that they needed both high performance and low power. With a dual-oxide 90 nm process, we would have had to choose performance or power. This wasn't good enough. By employing a triple-oxide 90 nm process, we achieved high performance and low power.

The 10-layer copper refers to the number of metal interconnect layers and their

material, which is copper rather than aluminum (the traditional material). More layers provide more routing in less space and shorter connection distances. Copper reduces resistance compared to aluminum, and thus speeds signal interconnect and reduces on-chip power-distribution IR drop. As clock rates go up and voltages go down, these considerations have become increasingly important, and have driven the industry-wide shift to copper interconnect.

The Virtex-4 logic fabric was completely re-engineered to fully take advantage of the 90 nm triple-oxide CMOS process, resulting in the highest performance fabric ever, with system clock rates in excess of 500 MHz (at three LUT levels). At the same time, static power was cut in half compared to 130 nm Virtex-II Pro<sup>TM</sup> devices, as was dynamic power.

Thus, while some industry pundits were proclaiming that the future of deep submicron CMOS devices was getting hotter and hotter, with chip temperatures destined to reach that of rocket nozzles and the surface of the sun, the Virtex-4 design's creative approach has turned that conventional wisdom on its head, resulting in overall power reductions of 50% compared to our previous 130 nm generation. In many applications, such as DSP functions, power levels are reduced even more – as much as 90%. No wonder design engineers say that Virtex-4 FPGAs are cool – they literally are.

### **High-Performance Clocking**

Clocks were rated as one of the most important and critical FPGA resources in our surveys of design engineers. Quantity, quality, connectivity, frequency, duty cycle, jitter, and skew all made a big difference.

To take clocking to the next level in Virtex-4 devices, all global clock resources were made fully differential, thereby reducing skew, jitter, and duty-cycle distortion. This marks the first implementation of differential clocking in a programmable logic device. Not only that, but the number of global clocks was increased to 32, for every

device, and internal connectivity options enhanced to allow any region to use any 8 clocks simultaneously.

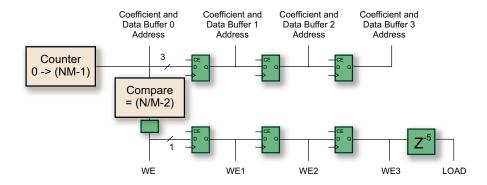

### 500 MHz Synchronous Memories and FIFOs

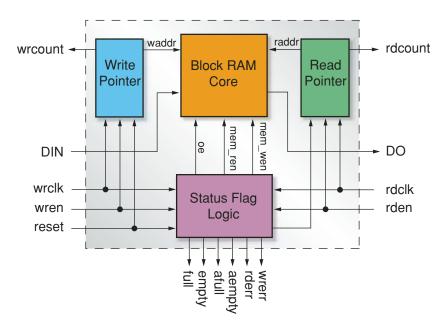

On-chip synchronous block RAM was enhanced to run at 500 MHz. Built-in support for first-in first-out (FIFO) memories was included directly in the block RAM unit, enabling the same 500 MHz operation for FIFOs (approximately a 2X speedup over fabric-based FIFOs), while eliminating the need for any additional logic cells or complex FIFO designs.

If you're designing systems requiring ECC (error checking and correcting) memory, Virtex-4 devices have built-in ECC support, with single-bit correct and double-bit detect. ECC is common in infrastructure equipment in networking, telecom, storage, servers, instrumentation, and aerospace applications, and provides the highest levels of data integrity. Like the integrated FIFO support, the integrated ECC eliminates the cost and delay of fabric-based solutions.

Speaking of on-chip memory, Virtex-4 devices continue to offer SelectRAM<sup>TM</sup> memory, whereby each LUT is transformed into a 16 x 1 RAM, ideally suited for building high-speed register files and local buffers.

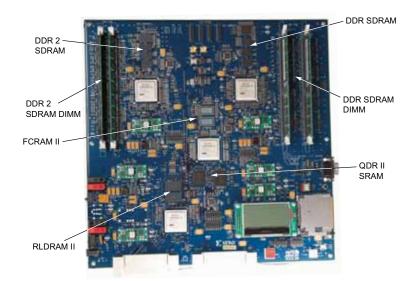

At the other end of the spectrum, interfaces to external memory devices such as DDR, DDR2, QDR-II, and RLDRAM-II are dramatically enhanced through our new ChipSync<sup>TM</sup> technology, which offers memory interface speeds at rates limited only by the speed of the external memory devices.

The new Virtex-4 ML461 Advanced Memory Development System contains fully functional and hardware-proven reference designs for all of today's most popular memory technologies. If you plan to use external memory, I highly recommend that you check this out.

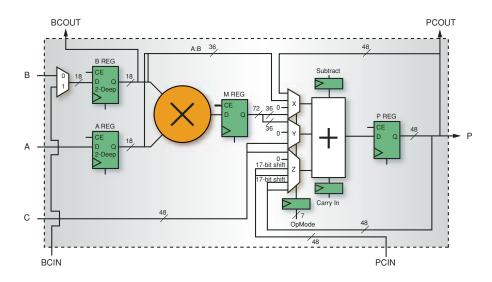

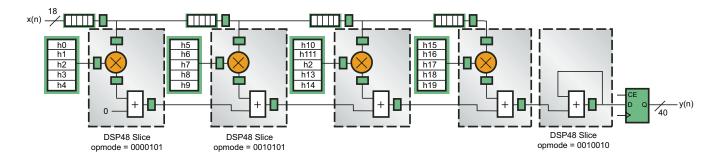

### DSP Performance of 256 TeraMAC/s

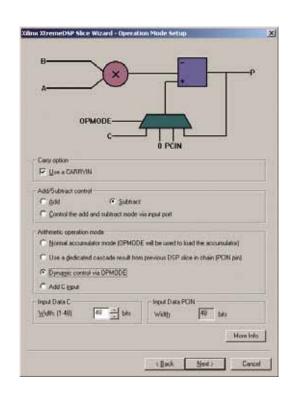

In the DSP domain, we incorporated some of the world's fastest multiply accumulate (MAC) technology. The XtremeDSP<sup>TM</sup> slice can perform an 18 x 18 signed multiply and 48-bit accumulate every 2 ns.

The Virtex-4 LX, FX, and SX platforms include the breakthrough XtremeDSP technology. With the new SX platform we did something completely new – we dramatically increased the ratio of DSP units to logic cells. Given the highly integrated nature of XtremeDSP slices, they need only small amounts of logic fabric to implement most common DSP functions, and thus increasing the ratio provides a significant increase in DSP compute power per unit silicon area. In fact, SX devices provide a 10X performance increase per unit cost over previous solutions.

Power is dramatically reduced as well, with more than a 10X reduction for multiply/add functions from previous FPGA solutions. The Virtex-4 SX55 contains 512 XtremeDSP slices, providing an aggregate DSP compute performance of 256 TeraMAC/s, making it one of the most powerful DSP devices ever manufactured.

The state-of-the-art XtremeDSP slice employs new "silicon algorithms" developed by a company called Arithmatica<sup>TM</sup>. Many different architectures exist for implementing multiplication, and the Arithmetica architecture is truly a breakthrough. We are excited to see it available for the first time to FPGA users. For more information, visit Arithmatica's website at www.arithmatica.com.

### The Evolution of Advanced I/O Technology

I/O continues to be a critical success factor for today's systems designers. During the last decade, we have seen four major changes in I/O. First was the shift away from 5V, the result of the need to scale voltages as we scaled the transistor. This in turn led to the plethora of I/O standards that we are all familiar with today: SSTL, HSTL, LVDS, and LVCMOS 1.5. The Virtex-4 SelectIO<sup>TM</sup> resource continues to lead the industry, supporting virtually every I/O standard in use today on every pin.

### XCITE On-Chip Termination

The second major change was the transition from lumped loads to transmission line loads – again the direct result of Moore's Law. As transistors got faster and clock rates increased, I/O edge rates

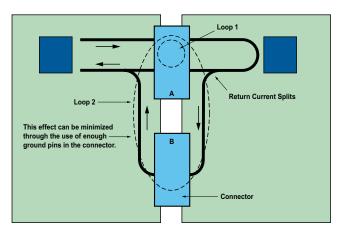

increased as well. But because the propagation speed of signals is a constant, dictated by the speed of light, we entered the realm in which a signal on one end of a wire was no longer the same as the signal on the other end of the same wire. This is what transmission lines are all about, and their appearance during the last few years has driven a sea change in all aspects of signal interconnect and I/O design.

To make sure that these signal "waves" don't start "splashing" uncontrollably, transmission lines need to be driven, built, and received using proper signal integrity approaches, the most critical of which is termination. Traditionally implemented with discrete resistors on the PCB, termination layouts can become exceedingly difficult around high-density pinouts like those used in FPGAs. This often dictates more PCB layers and thus more system cost.

Virtex-4 FPGAs include our third-generation of XCITE<sup>TM</sup> integrated digitally controlled termination technology. Offering a precisely controlled source impedance at the output drive pin, it is designed to enable the driving of transmission lines without external components, with maximum speed and signal integrity, and with straightforward PCB layout and layer stack-ups.

Likewise, on inputs, XCITE offers parallel termination for single-ended inputs and true differential termination for differential inputs. Termination occurs on the end of the transmission line at the die, not on the way there on the PCB, offering maximum signal integrity. Many customers report that the XCITE technology has saved them many PCB layers, increased PCB packing density, and saved them substantial dollars in their bill of materials.

### Source-Synchronous Interfaces

The third major change was the shift from system-synchronous to source-synchronous interfaces. Traditional system-synchronous interfaces work by distributing a single clock to all transmitters and receivers in the system, and transmitting data between source and destination within a single clock cycle. This makes the data rate inversely proportional to the sum of clock-

to-out, transmission line delay, and input setup time.

Typically, system synchronous interfaces top out at speeds in the range of 100 MHz. To go faster, source-synchronous interfaces transmit a clock along with the data, and the receiver uses this clock to capture the data. Using this technique, along with double-data-rate transmissions, enables parallel I/O data rates in excess of 1 Gbps.

The challenge of source-synchronous interfaces is that each interface generates a new clock domain at the receiver. On top of this, to operate at high speeds, the precise alignment of clock and data at the receiver is paramount. To address this new world of source-synchronous interfaces, Virtex-4 devices include the breakthrough ChipSync technology. ChipSync units lie between the SelectIO technology and the core FPGA fabric, are available on every I/O pin on the device, and serve to transmit and receive high-speed source-synchronous data and clocks, achieving speeds of 1 Gbps per pin pair.

On the receiver, precise digital delay lines work internally to align data signals to each other, and then to align these to the received clock. The captured data is synchronized and transferred to the selected FPGA core clock domain.

To operate at maximum data rates, the transmit and receive units include parallel-to-serial and serial-to-parallel conversion units, respectively. Using ChipSync technology is virtually automatic for most designs, as it is utilized automatically in the various Xilinx IP cores and reference designs.

Networking interfaces such as SPI-4.2 and HyperTransport<sup>TM</sup>, and memory interfaces such as DDR, DDR2 SDRAM, and QDR II SRAM, all employ the Virtex-4 ChipSync technology. And if you're designing your own source-synchronous interface, the ChipSync wizard gives you complete control and an easy-to-use GUI that lets you dial in exactly what you want to build.

### Multi-Gigabit Serial Interfaces

The fourth major change in I/O has been the rapid adoption of high-speed serial interfaces. For years, serial interfaces were limited to long-distance communications, such as those used in fiber-optic links in the SONET/SDH world and the Ethernet links like 100BASE-T.

A key breakthrough occurred in the late 1990s, in which high-speed serial transceivers (which traditionally had been designed using complex process technology such as GaAs [Gallium-Arsenide]) were for the first time created using advanced design techniques using standard CMOS. Once implemented in CMOS, these transceivers had lower cost and much lower power, and could even be integrated into complex CMOS chips.

Virtually overnight, gigabit serial technology changed from a rare, expensive, and power-hungry technology to a common, low-cost, and very power-efficient technology. This has been the economic and technical impetus behind the industry's "Serial Tsunami," in which interface after interface has shifted from parallel to gigabit serial links. Two common examples are visible in today's computer architectures, with the shift from parallel PCI to 2.5 Gbps serial PCI-Express<sup>TM</sup>, and the shift from the parallel ATA drive interface to the Serial ATA interface.

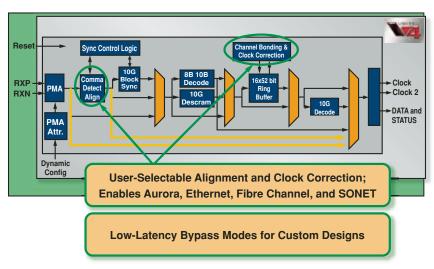

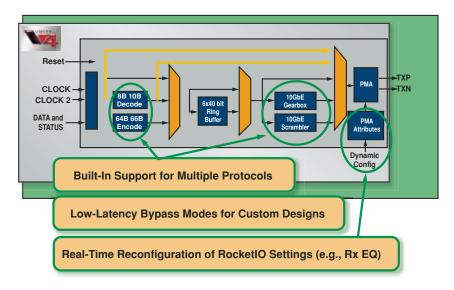

There are more than a dozen multi-gigabit serial interfaces in widespread use today, with more being introduced every year. The Virtex-4 FX family provides our third-generation RocketIO<sup>TM</sup> multi-gigabit serial transceiver technology. Spanning speeds from 622 Mbps to more than 11 Gbps, each Virtex-4 RocketIO transceiver is programmable and can implement a myriad of speeds and serial standards. Link-layer IP is available for such standards as PCI Express, Serial-ATA, FibreChannel, Gigabit Ethernet, and Aurora, to name a few.

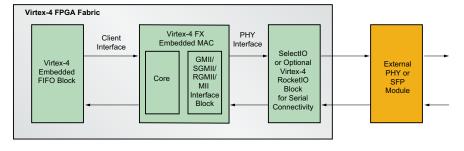

In addition, Virtex-4 FX devices each include multiple embedded tri-mode (or 10/100/1000) Ethernet MACs, making implementation of compliant Ethernet devices simpler and faster than ever.

### **Application-Specific Embedded Processing**

Virtex-4 embedded processing solutions include full support for both MicroBlaze<sup>TM</sup> 32-bit soft CPUs on all devices, and embedded PowerPC<sup>TM</sup> 32-bit RISC CPUs on all Virtex-4 FX devices. The versatile MicroBlaze soft CPU runs at clock rates of

up to 200 MHz on Virtex-4 devices, and delivers more than 140 DMIPS.

The number of CPUs in one device is limited only by your imagination, and of course by the available logic cells. The powerful PowerPC CPU runs at clock rates up to 450 MHz and delivers more than 680 DMIPS each. The first PowerPC processor available by any manufacturer on 90 nm, the PowerPC processor is incredibly power-efficient, using only 29 mw/DMIPS. This makes it among the lowest power microprocessors available from any manufacturer worldwide.

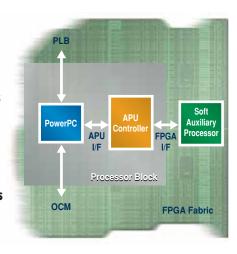

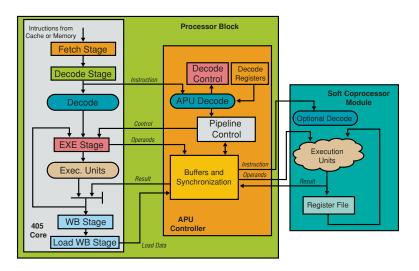

New Auxiliary Processing Unit (APU) technology connects the CPU to the FPGA fabric, enabling implementation of acceleration hardware for virtually any application. Once only the domain of high-budget ASIC and ASSP design teams, the Virtex-4 FPGA's architectural ability to combine application-specific hardware acceleration with high-performance RISC CPUs shatters traditional barriers of cost, time-to-market, and risk.

During the next few years, I expect to see more and more instances of application-specific acceleration, as it truly offers the ability to deliver very high performance at low cost and low power. A recent research program completed within Xilinx Research Labs, led by Dr. Kees Vissers, demonstrated a 20-fold speedup for an encryption/decryption (IPSEC) application over the base PowerPC processor. Using only 135 mW, it outperforms a 3.2 GHz Pentium<sup>TM</sup>-4, while at the same time reducing power by 99%. That, in my opinion, is what state-of-the-art embedded processing is all about.

### Conclusion

I hope that you've enjoyed reading a bit about the Virtex-4 Platform FPGA and the factors that drove its design. From the breakthrough ASMBL architecture and the triple-oxide 90 nm CMOS process technology, to the world's most capable embedded processing and multi-gigabit serial solutions, Virtex-4 devices offer an unparalleled set of enabling technologies for your next-generation systems designs. I look forward to seeing the creativity of the world's designers in tomorrow's products.

9

# Will the Evolution of Platform FPGAs Mean the End for ASICs and ASSPs? Today's multi-platform

Today's multi-platform

FPGAs shake up

ASIC/ASSP suppliers.

by Richard Sevcik

Executive Vice President, Programmable Logic Systems and Intellectual Property/Cores and Software Solutions Groups Xilinx. Inc.

publicrelations@xilinx.com

The debate over FPGAs as a viable alternative to ASICs and ASSPs has been ongoing for nearly a decade. Industry analysts iSupply, Gartner Dataquest<sup>TM</sup>, and others have documented the trend in decreasing ASIC design starts and the increase in FPGA design starts.

Next-generation platform FPGA devices based on 90 nm have greatly expanded high-performance processing and system integration options. They continue to push ASIC design starts lower as additional application solutions are defined.

With the beginning of the new millennium, the debate continued with the introduction of Xilinx® Virtex-II<sup>TM</sup> and Virtex-II Pro<sup>TM</sup> devices – the industry's first platform FPGAs. These highperformance devices, with their flexible device integration capability, programmable I/O, and significantly lower overall design cost, helped to usher in and establish SoC design methodology and quickly assumed innumerable ASIC SoC designs.

The addition of high-performance RISC CPUs, block RAM, multi-gigabit high-speed serial I/Os, dedicated DSP functions, and other system enhancements introduced technological advances that further solidified the rise of platform FPGAs over their ASIC SoC counterparts. However, to get high-performance DSP, processing, or connectivity features for a specific applications domain, designers were typically forced to purchase the largest, costliest devices. The larger parts had the biggest helpings of advanced features, while the smaller parts had reduced portions of the same.

Today, a new breed of domain-optimized, multi-platform FPGAs from Xilinx – the Virtex-4<sup>TM</sup> family – promises multi-dimensional application scaling based on required features and cost goals. By combining the economic benefits of an innovative columnar architectural approach with advances in process technology (90 nm/300 mm), Xilinx is poised to move beyond the \$5.1 billion programmable logic market to capture additional share in the \$84 billion ASIC and ASSP markets (Source: Gartner Dataquest 2007).

### Just the Right Mix

Based on the revolutionary Advanced Silicon Modular Block (ASMBL) columnar architectural approach, Xilinx can now cost-effectively develop multiple FPGA platforms, each with different combinations of feature sets. Thus, a specific platform can be optimized specifically for a certain domain of applications – such as logic, DSP, connectivity, and embedded processing – to meet application requirements previously delivered only by ASICs, ASSPs, and similar devices, while remaining programmable at heart.

Not only does the designer or design team have a choice in selecting the ideal platform, they also have a choice in choosing the device size with just the right feature mix to best achieve needed capability and performance at the lowest possible cost.

This unique flexibility and ability to create optimal application domain subsystems sets even higher standards for FPGAs. Devices that are both hardware- and

software-programmable enable more flexible implementation options than either ASIC or ASSP devices. Reinvestigating, changing, or enhancing system architecture at any time in the development process provides the ultimate tool kit to meet application requirements.

Designers can use this same capability to evolve hardware in the field to meet new

technology is used throughout the world. No two people use the same technology, systems, or software, nor do they subscribe to or want the same content.

Higher costs and longer design times for ASICs and ASSPs relegate their primary uses to proven lower-risk, very-high-volume applications. The rapid and significant increase in ASIC development costs clearly

requirements or avoid expensive hardware upgrades. This flexibility becomes paramount given today's many emerging and competing standards.

### The "Total Cost" Advantage

FPGAs have demonstrated a clear and consistent trend in reducing cost and making FPGA technology more suitable for a wider range of applications. The combination of 90 nm silicon fabrication technology with 300 mm wafers results in a cumulative effect: increasing the number die-per-wafer five times over previous devices. Increasing the die-per-wafer together with architectural integration enables substantially lower system costs.

A key and often overlooked component in favor of programmable logic's economic advantage is clearly demonstrated in how gives the advantage to platform FPGAs in today's leading-edge applications. The overall cost benefit of zero NRE pushes the high-volume ASIC or ASSP crossover point upwards, locking in FPGAs like never before.

### Conclusion

Domain-optimized multi-platform FPGAs are revolutionary in their ability to accelerate the deployment of FPGA technology into many more application areas. The combined leverages of reduced risk, dramatically shorter design cycles, and zero NRE will soon move all but the highest volume applications away from cell-based ASIC implementation toward more flexible, forgiving architectures like today's domain-optimized FPGAs. For more information, visit www.xilinx.com/virtex4/.

by Gokul Krishnan Sr. Marketing Manager, Market Specific Products Group Xilinx, Inc. gokul.krishnan@xilinx.com

Balaji Thirumalai Sr. Marketing Manager, Worldwide Marketing Xilinx, Inc. balaii.thirumalai@xilinx.com

The risk of deploying ASIC solutions has worsened in magnitude with the move to smaller process geometries. As design complexity increases, customers are looking for a viable solution that offers low design, unit, and total costs, high-level system integration, design flexibility, easy-to-use design tools, a rich selection of IP, and fastest time to market.

Customers are increasingly turning to other alternatives to avoid the pitfalls of ASICs – high NRE and re-spin expenses, slow turnaround times, complex design environments, and hidden conversion, verification, and development costs. In this article, we'll analyze two such alternatives: Xilinx® EasyPath<sup>TM</sup> FPGAs and structured ASICs.

Structured ASIC product offerings tend to be similar to FPGAs in that they have predefined combinations of gates, memory, and I/Os. However, their architectures tend to trade off flexibility in favor of reduced area to achieve their cost targets. The reality remains that a vast majority of designs intended for ASICs are originally prototyped in an FPGA, yet there are still problems with FPGA-to-structured-ASIC conversions. EasyPath FPGAs offer the best migration path to high-volume production at the lowest cost possible.

### EasyPath FPGAs

EasyPath FPGAs are the industry's only customer-specific and flexible solution for volume production priced lower than structured ASICs.

EasyPath FPGAs are identical to our standard FPGA offerings but use patented testing techniques and customer-specific test patterns to significantly improve FPGA yields. You can reap the benefits of these improved yields in the form of lower costs, because Xilinx only tests those parts of an

FPGA that are actually used in your design.

With EasyPath FPGAs, you can realize a 30-80% reduction in prices when you move to high volume, as compared to standard FPGAs. EasyPath FPGAs are available across six platforms, four different product families, and 28 different devices over a range of gate and memory counts.

EasyPath FPGAs are identical to their standard FPGA counterparts, effectively eliminating any conversion work. Once you have frozen your design, Xilinx can deliver EasyPath parts in high volume in eight weeks. This compares favorably against structured ASIC companies, which typically take 12-14 weeks from prototype signoff to production.

### Structured ASICs

Structured ASICs are a variant of the gate arrays of yesteryear, but they use a "sea of modules" approach as opposed to a "sea of gates" approach. The architecture of each module varies depending on the vendor, but in general is some combination of NAND gates, inverters, flip-flops, and muxes.

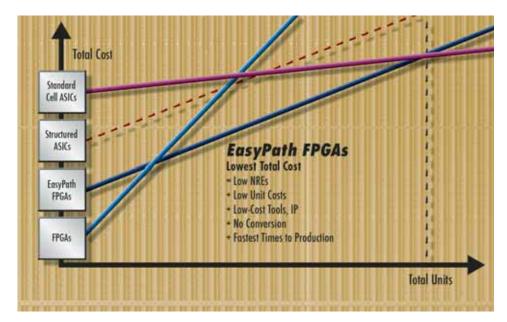

Figure 1 – EasyPath FPGAs offer the lowest total cost solution.

Structured ASICs promise cost savings primarily as a result of customizing fewer mask layers per design, unlike standard cell ASICs that use all-custom metal layers. Structured ASICs use only the top few (typically two to four) metal layers; the base modules are all buried in the lower layers, with their ports coming up to the programmable layers. During the fabrication phase, the connections between various ports are made to realize the requisite logic.

### The Lowest Total Cost Solution

Figure 1 shows the comparative economics of standard cell ASICs, structured ASICs, FPGAs, and EasyPath FPGAs. FPGAs have traditionally offered a zero-NRE solution, which has led to their broad adoption. Standard cell ASICs have a high NRE and a relatively low unit cost, but with the overhead discussed earlier. Structured ASICs promise to lower the NRE at a unit cost that is higher than that of standard cell ASICs, but lower than that of standard FPGAs.

With next-generation EasyPath FPGAs, you can now enjoy unit prices as well as NREs that are lower than structured ASICs. The combination of the industry's lowest NRE charges (starting at \$75K); low cost design tools and IP; prices below structured ASICs; fastest times to production; and no hidden conversion charges show how EasyPath

FPGAs are the industry's lowest total cost solution for volume production.

### **Unmatched Choice of Platforms**

Structured ASIC vendors can roughly be grouped into two camps based on their ability to address IP-centric designs. On the one hand are those that have a wide portfolio of IP; on the other are companies that typically can only address generic designs. With the recent announcement of next-generation EasyPath FPGAs from Xilinx, both of these segments can be addressed economically and efficiently.

Xilinx now offers four families and six platforms, with 28 devices from which to choose. This comes with all the benefits of the FPGA ecosystem that Xilinx customers are already used to – hard IP such as the IBM<sup>TM</sup> PowerPC<sup>TM</sup>, MGTs, and XtremeDSP<sup>TM</sup> blocks, as well as 600+ proven soft IP cores and low-cost design tools.

Some structured ASIC vendors focus exclusively on generic designs or logic-heavy designs. This class of design tends to be very price competitive. Xilinx is now able to offer a more compelling solution than any structured ASIC vendor with its Spartan-3<sup>TM</sup> EasyPath FPGAs, which are priced below these structured ASICs.

For designs that require a lot of IP and system integration such as PowerPC processors, DSP, high-speed I/O, or Ethernet

MACs, translation to a structured ASIC vendor often requires a re-validation of the IP on the vendor's silicon platform of choice. With Xilinx Virtex-4<sup>TM</sup> EasyPath solutions, you get the same wide range of validated IP as with standard FPGAs. There is no additional fee required to migrate the IP to a volume solution.

The bottom line is that whether it is a generic design or an IP-centric design, EasyPath FPGAs offer very competitive and cost-effective solutions for high-volume migration when compared to structured ASICs, all from a single trusted supplier. Migration to structured ASICs, on the other hand, can pose a number of challenges.

### **Conversion-Free Methodology**

The vast majority of IC design starts begin with FPGA prototyping, followed by a conversion to a volume solution. This carries the inherent risk of redesigning and reverifying the design in the target architecture, along with the related costs of re-spins, conversions, and a host of other design issues. The conversion from FPGA to structured ASIC is not seamless; rather, it is fraught with risks.

One issue faced by structured ASIC companies revolves around the mapping of memories from an FPGA to a structured ASIC. FPGAs generally tend to have columnar memory architectures and offer an efficient means to form larger memory structures when required. On the other hand, the use of distributed memory blocks in some structured ASIC architectures can pose problems when large contiguous blocks are required by the design.

The need to join together blocks that are physically separated to form a larger block that is logically monolithic can increase routing congestion. This can not only potentially deteriorate the access times of those memory structures but also leave fewer routing resources available for logic, thus impacting design performance.

With EasyPath FPGAs, there is no conversion. EasyPath FPGAs are exactly the same as the standard FPGAs on which a design is prototyped – the only difference is that the latter are completely programma-

13

ble, while the former are not. As a result, memory mapping and performance achieved in an EasyPath FPGA is identical to that achieved in a standard FPGA.

Another problem that some structured ASIC companies face has to do with pad limitations. It is fairly well known that as process nodes shrink, more and more designs become pad-limited in ASICs. To get an adequate number of pads, structured ASIC vendors sometimes have to grow their die size and increase the effective cost to end customers. This problem is compounded by the fact that structured ASIC I/Os tend not to be as flexible as FPGA I/Os.

To keep I/O structures small and less area-intensive, structured ASIC vendors

have to make some difficult choices about what standards they want to address and how. In cases where designs require large buses of input and output I/Os (for example, SSTL2 buses for SDRAM, or HSTL buses for certain telecom protocols), the limitations in the design of I/O structures can make it difficult to achieve pin compatibility in the FPGA-to-ASIC conversion. The end result is that customers have to either re-spin their board or migrate to a larger device - both unpalatable options. None of these are issues with EasyPath FPGAs because of the one-toone mapping between them and standard FPGAs.

Apart from memory and I/Os, there is a whole other host of issues, including difficulties with IP translation and testing, when moving from FPGAs to structured ASICs. FPGA cost reduction plans that involve converting to structured ASICs in order to get a smaller die are likely to trigger design changes and schedule risks.

The EasyPath solution, on the other hand, is neither an ASIC conversion nor a mask-programmed FPGA. No conversion or silicon differences are involved, so there are no long lead times, no timing or pinout changes, no need for product qualification, no lost feature support, and no risk of a design failure. In addition to eliminating any hidden design or qualification expenses and the risks of ASIC conversions, EasyPath FPGAs are delivered in eight weeks in production volume, allowing you the benefits of faster time to market or more time to perfect your designs

### **Unprecedented Flexibility**

One of the major advantages of FPGAs over ASICs is the flexibility to make design changes in case of a specification change or a design error. Traditionally, customers have had to forgo this advantage as they move from FPGAs to an

EasyPath Structured Selection Criteria ASICs\* **FPGAs** Time to Prototype Samples 4-8 weeks 0 weeks **Total Time to Volume Production** 12-15 weeks 8 weeks Vendor NRE/Mask Costs \$75K \$100K-\$200K **Design Costs for Conversion** \$250K-\$300K \$0 Additional Cost of Tools \$100-\$200K \$0 for Conversion **Unit Costs** Low Low Risk High Low Flexibility to Make Changes Inflexible Flexible In-System **Design Conversion from** Additional Engineering **Conversion Free** Prototype to Production \*Xilinx market analysis

Table 1 – EasyPath FPGAs versus structured ASICs

inflexible custom solution like standard cell or structured ASICs. Now, with EasyPath FPGAs, Xilinx offers two flexibility features that allow you to enjoy some of the FPGA advantages when you go to volume production at prices below structured ASICs.

Spartan-3 and Virtex-4 EasyPath FPGAs enable you to buy a custom device that supports two applications — one for diagnostic testing and one for the actual application. EasyPath FPGAs can now be tested for two designs, or two variations of the same design. This means that you can

now enjoy greater flexibility while also saving on BOM and inventory costs. For example, you can use one bitstream to perform system diagnostics on the entire system and then load the second application-specific bitstream. This reduces associated manufacturing system costs.

Xilinx offers EasyPath FPGA devices with LUTs and I/Os tested for drive strengths and slew rates, allowing revisions like engineering change orders at the LUT or I/O level. In many instances, even after the customer design is fully functional and certified, flexibility with I/O drive strengths and slew rates is critical.

For instance, a line card in a router might need to have the drive strength (and slew rate) adjusted a notch or two depend-

ing on what load it sees. EasyPath customers can choose to have a range of drive strengths available to them for certain I/Os. The unique flexibility is implemented on an asneeded basis. This eliminates any re-spin and conversion-related engineering effort, delay, and expenses associated with ASICs and structured ASICs.

### Conclusion

EasyPath FPGAs from Xilinx offer a seamless one-for-one, no-conversion volume reduction solution across an industry-leading portfolio of product families. The comparison between EasyPath FPGAs and

structured ASICs shown in Table 1 illustrates why EasyPath is a much superior solution. Unlike structured ASICs, EasyPath customers can get to production volumes much faster and now can do so at lower prices as well.

For more information about the next-generation EasyPath FPGAs, please visit www.xilinx.com/easypath/, where you can get information on the platform support, flexibility features, and use an online cost calculator to find out why EasyPath FPGAs are the lowest total cost solution in the industry.

Learn how the latest Xilinx technology can help you design cost effective solutions faster.

Gain hands-on experience to speed up your next development cycle.

What Are You Waiting For? Register now for the event nearest you.

Visit www.memec.com/xfest-2005

ASIA ~ CANADA ~ EUROPE ~ JAPAN ~ UNITED STATES

Copyright 2004 Memec, LLC. All rights reserved. Logos are owned by their proprietors and used by Memec with permission. All company and product names may be trademarks of their respective companies.

# The Virtex-4 Power Play

The latest Xilinx FPGA offers revolutionary power innovations.

by Matt Klein

Sr. Staff Engineer, Applications Engineering,

Advanced Products Division

Xilinx, Inc.

matt.klein@xilinx.com

Device power consumption is a primary issue in the semiconductor industry – as process technologies get smaller and faster, they normally consume more power, putting power concerns and performance at odds. The new Virtex-4<sup>TM</sup> FPGA family from Xilinx® employs innovative architectural features and clever IC design techniques that dramatically reduce power consumption, without compromising performance. This bucks expected trends nor-

mally associated with the reduced feature sizes of 90 nm process technology.

In this article, we'll explore how Xilinx IC designers achieved remarkable power efficiency in the high-performance Virtex-4 FPGA.

### **Components of Power Consumption**

There are two main components to power consumption: static and dynamic. Static or quiescent power is mainly dominated by transistor leakage current. When this current is listed in data sheets, it is listed as  $I_{\rm CCINTQ}$  and is the current drawn through the  $V_{\rm CCINT}$  supply powering the FPGA core.

Dynamic or active power has components from both the switching power of the core of the FPGA and the I/O being switched. The

dynamic power consumption is determined by the node capacitance, supply voltage, and switching frequency and governed by the basic formula  $P=CV^2f$ .

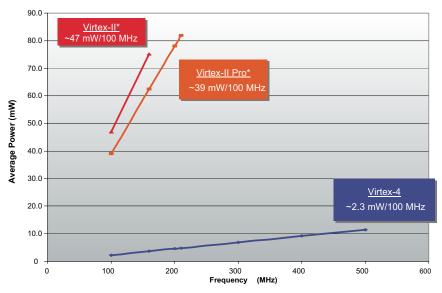

Both static and dynamic power have been significantly reduced in Virtex-4 devices, even when compared to Virtex-II Pro<sup>TM</sup> devices.

### **Dramatic Power Reduction**

The Virtex-4 product family has reduced power consumption in several key areas. The power-per-CLB has been cut in half, with static power reduced by 40% and dynamic power reduced by 50% when compared to the 130 nm Virtex-II Pro FPGA and other 90 nm FPGAs. Furthermore, certain hard-logic silicon functions in the Virtex-4 FPGA reduce power consumption by 80-95%, a whopping factor when compared to the same functions implemented in configurable logic blocks and programmable interconnect routing.

Additionally, comprehensive power planning tools are available to help you get an idea, up front, of power consumption for your Xilinx FPGA under its operating conditions.

### Reduced Power Consumption Benefits

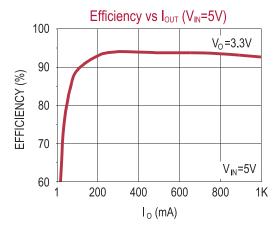

Reduced power consumption benefits cut across a few areas of product design in reduced thermal concerns as well as eased power supply design (see Figure 1).

- Reduced thermal concerns When you reduce power consumption in a device or system, you use smaller heat sinks, or no heat sinks at all in some cases. You also have simpler thermal system design from the point of view of reducing airflows and fan size needs.

- Easier power supply design You can also use smaller supply circuitry and reduce the number of components in the power supply. Using less PCB space allows you to reduce the cost of the power system. Plus, by not having your device consume as much power, you can achieve higher reliability by lowering the temperature of the FPGA die.

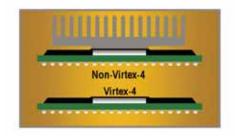

Figure 1 – Virtex-4 devices reduce thermal concerns and simplify power supply design.

### Static Power Trends in 90 nm Technology

The reduction in transistor size in 90 nm technology has several effects on power consumption. The biggest potential problem is in the area of static power.

### Scaling Trends for Static Power

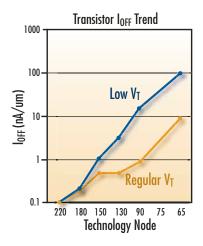

As we mentioned earlier, static power is dominated by transistor leakage current. Unfortunately, channel leakage increases as transistor size decreases. This is especially true for low  $V_{\rm T}$  transistors where  $V_{\rm T}$  refers to voltage threshold between the gate and drain.

Low  $V_T$  transistors are the fastest transistors – the ones with the shortest turn-on and propagation delay – that IC designers use inside the FPGA when the highest speed performance is needed. Regular  $V_T$  transistors are also used when less performance is acceptable, but this only helps so much with leakage.

Figure 2 shows that leakage goes up dramatically when moving from 130 nm to 90 nm technology. The Virtex-II Pro device uses 130 nm process technology, whereas the new Virtex-4 device uses 90 nm process technology.

### Triple-Oxide — The Savior of Static Power

Triple-oxide simply means that we use a third thickness of oxide in making some of the transistors in the FPGA (two oxide thicknesses are used in devices like the Virtex-II Pro FPGA). Most transistors in the past had a thin oxide layer. Within those transistors could be low V<sub>T</sub>, regular V<sub>T</sub>, NMOS, or PMOS transistors. Thick-oxide transistors are mostly used for I/O drivers and a few other functions.

Oxide deposition thickness is a very stable and controllable process in the semiconductor industry because it depends on temperature, concentration, and exposure time. Figures 3a and 3b show the Virtex-4 transistor with the middle oxide thickness used in the triple-oxide process. You may notice that the oxide thickness is still very, very thin, but this thicker oxide transistor has much lower leakage than the standard thin-oxide low V<sub>T</sub> and regular V<sub>T</sub> transistors used in Virtex-II Pro FPGAs and in various parts of Virtex-4 FPGAs.

Figure 2 – Transistor leakage trends due to process scaling

### Why Doesn't Everyone Use Triple-Oxide? If triple-oxide is such a great process, why don't other companies like Intel<sup>TM</sup> or IBM<sup>TM</sup> use it in their own ASICs?

They probably would if it benefited them. The reason they don't is that all of their transistors need to run at speed; hence, they must use the low V<sub>T</sub> leakier transistors for everything. FPGAs can have many different transistor types, which can be selected for function, power, or performance.

FPGAs can use different transistor types for different functions, and Xilinx designers have accomplished this balance.

### Optimizing Performance and Leakage

Our IC designers have many things that they can do to adjust the mix to optimize for certain factors. The Virtex-4 FPGA is the first Platform FPGA designed for high speed and low power.

Low  $V_T$  transistors are used only where necessary for maximum speed, while the middle thickness of oxide from the triple-oxide process may be used for less aggressive performance with very low leakage. You may use different sizes and types of transistors for performance and function. Combinations are also possible, such as small and medium-sized low  $V_T$  fast transistors and small and medium-sized middle oxide thickness transistors. It is not a one-size-fits-all procedure.

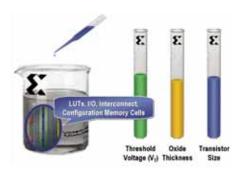

Xilinx IC designers were given a directive to reduce power, among other things, in the Virtex-4 platform while maintaining the highest system performance. These transistors are used across the various FPGA functions of LUTs, I/O, interconnect, and configuration memory cells. Even within a given FPGA function, all transistors don't need to be the same, and that is up to the Xilinx IC designers (see Figure 4).

The surprising result of this balancing is that the overall static current in Virtex-4 devices with 90 nm process is reduced by 40% when compared to Virtex-II Pro devices with 130 nm process. Table 1 shows a chart of the weighted average changes to the transistors in the Virtex-4 die compared to Virtex-II Pro die, which allows you to arrive at the reduced transistor leakage in the Virtex-4 FPGA.

Figure 3a, 3b – Middle oxide thickness Virtex-4 transistor used in triple-oxide process and with highlighted portions of the transistors

Figure 4 – Optimal transistor mix for minimizing leakage and maximizing performance

### **Dynamic Power Reduction**

Static power reduction, while dramatic, is not the only power winner that you can take advantage of. Dynamic power is also reduced by 50% when compared to Virtex-II Pro FPGAs.

The dynamic power in the FPGA is governed by the following equation:

$P_{Dynamic} = FPGA_{Core}(CV^2f) + FPGA_{I/O}(CV^2f)$

The Virtex-4 family of FPGAs has the following:

- Reduced FPGA core dynamic power

- Internal operating voltage is the dominant factor

- Secondary scaling by frequency (f) and node capacitance (C)

- Constant FPGA I/O dynamic power

- Unchanged voltage swing (V<sub>I/O</sub>), toggle rate (f), and pin/pad capacitance (C) for a given I/O standard

So you can see that we may be able to have an effect on dynamic power inside the device, but that dynamic power consumed by I/O switching remains unchanged.

When we go from the 130 nm process of the Virtex-II Pro FPGA to the 90 nm process of the Virtex-4 FPGA, the internal supply voltage changes from 1.5V to 1.2V. This reduces the dynamic power consumption for every internal transistor by  $36\% \left(1-\frac{[1.2]}{[1.5]}\right)^2$  of that in the Virtex-II Pro FPGA.

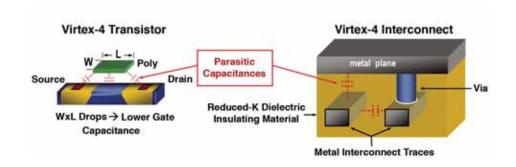

Additionally, the FPGA internal composite capacitance is reduced in the Virtex-4 FPGA. This internal capacitance comprises transistor parasitic capacitances and trace-to-metal and trace-to-trace capacitances for the interconnecting metal traces. Figure 5 shows the capacitance involved relative to their structures.

As mentioned earlier, dynamic power is related to the bulk capacitance and internal voltage levels being switched,  $P = CV^2f$ . All things being equal, having a lower internal capacitance for the interconnects would be a benefit for dynamic power and reduced resistor-capacitor delay, but other factors contribute to interconnect capacitance, such as distance above the metal plane, interconnect width, and interconnect length.

Additionally, other parasitic capacitances such as gate-to-drain and gate-to-source are also part of the equation. Total capacitance for a path is based on a complex combination of parasitic capacitance

Figure 5 – Internal FPGA capacitance comprises parasitic transistor and interconnect capacitances

Does low-K reduce power? Low-K refers to the dielectric insulating material between the metal traces in the FPGA. Lower K dielectric insulating layers do reduce internal capacitances per unit trace length, but "low-K" is a relative term. Xilinx has reduced-K-insulating materials, and in the past has used low-K itself; we may do so again in the future.

| in the transistors; the architecture of the | ne |

|---------------------------------------------|----|

| interconnect paths and actual pat           | h  |

| lengths; and the number of hops through     | gh |

| interconnect switches. Xilinx has reduce    | d  |

| the overall capacitance for those compo     | )- |

| nents in the Virtex-4 FPGA                  |    |

The overall effect is mostly due to reduced gate capacitance and lowers capacitance by 20% for Virtex-4 FPGAs when compared to Virtex-II Pro FPGAs. Table 2 shows a dynamic power reduction of 50% for the Virtex-4 FPGA when compared to the Virtex-II Pro FPGA. We have a 23% reduction in dynamic power when running at a 50% higher frequency.

Because the Virtex-4 FPGA is a much higher performance device than the Virtex-II Pro FPGA, you may need to operate it at higher clock speeds to meet newer demanding performance targets that could never be achieved in previous systems.

| Parameters                                               | Virtex-II Pro | Virtex-4 | Change |

|----------------------------------------------------------|---------------|----------|--------|

| Channel Width Ratio                                      |               | 0.64     | -36%   |

| Channel Length Ratio                                     | 1.00          | 0.71     | -29%   |

| Leakage Current per Unit Width Ratio                     |               | 1.14     | +14%   |

| Leakage Current per Transistor                           |               | 0.74     | -26%   |

| V <sub>CCINT</sub> Ratio                                 |               | 0.80     | -20%   |

| Static Power per Transistor Ration<br>(ILEAKAGE* VCCINT) |               | 0.59     | -41%   |

Table 1 – Overall weighted average transistor leakage and parameter comparisons for 90 nm Virtex-4 transistors relative to 130 nm Virtex-II Pro transistors

| Parameters                | Virtex-II Pro | Virtex-4 | Change |

|---------------------------|---------------|----------|--------|

| V <sub>CCINT</sub>        | 1.5           | 1.2      | -20%   |

| C <sub>TOTAL</sub> (rel.) | 1.0           | 0.8      | -20%   |

| f <sub>MAX</sub> (rel.)   | 1.0           | 1.5      | +50%   |

| Power at Same Frequency   | 2.25          | 1.15     | -49%   |

| Power at f <sub>MAX</sub> | 2.25          | 1.73     | -23%   |

Table 2 – Chart showing changes in internal FPGA in Virtex-4 devices compared to Virtex-II Pro devices and the effect on dynamic power

| Parameters            | Virtex-II Pro | Virtex-4    | Logic Slice<br>Reduction | Logic Slice<br>Power Reduction |

|-----------------------|---------------|-------------|--------------------------|--------------------------------|

| QDR II SRAM Interface | 550 slices    | 125 slices  | 77%                      | 89%                            |

| SPI-4.2 Core          | 5000 slices   | 3900 slices | 22%                      | 61%                            |

Logic slice power reduction =

$$100^* \left(1 - 0.5 \frac{\text{Virtex-4 slice count}}{\text{Virtex-II Pro slice count}}\right)\%$$

Note: The factor of 0.5 above comes from the fact that Virtex-4 power per slice is 1/2 of the Virtex-II Pro power per slice because of the 50% dynamic power reduction in Virtex-4 devices compared to Virtex-II Pro devices.

Table 3 – QDR II SDRAM and SPI-4.2 core benefit in reduced power consumption from significant logic cell reduction due to new Virtex-4 ChipSync block

### **Embedded Blocks**

Another major area of improvement in power consumption is in the area of embedded functions. This has always been a strength in Xilinx FPGAs, but it is more so in the Virtex-4 FPGA, even when compared to the feature-rich Virtex-II Pro FPGA.

In Virtex-4 FPGAs you can take further advantage of both static and dynamic power reduction by using the embedded functions, which are built as hard-logic functions.

When embedded functions are implemented as hard-logic functions instead of in configurable logic blocks and programmable interconnects, there is a lot less static and dynamic power consumed. This is because far fewer transistors are used for hard, fixed logic than for programmable logic. Additionally, there are no transistors needed to make connections for interconnects in the embedded functions, because there are no programmable interconnects.

Xilinx has carefully studied some of the functions that engineers like you have struggled with and that we have also found tedious to implement within the FPGA programmable logic. The new embedded functions lower power by 80-95% compared to their configurable logic blocks and routed counterparts in programmable silicon.

### **Comprehensive Power Planning Tools**

Another useful thing in planning power is that Xilinx data sheets show you both typical and maximum power consumption numbers. Maximum numbers are for worst-case process, temperature, and voltage, but many designers are very happy to work with typical numbers, depending on their application and the number of parts being used in one system.

One additional very useful thing that you can take advantage of in planning for power consumption in Xilinx FPGAs are power planning tools. Xilinx web power tools are available for estimating power early in the design cycle. Also, as part of the Xilinx design flow, XPower looks in more detail at a mapped or routed design. Both can be found, along with power application notes, by searching the Xilinx website for the phrase "Xilinx Power Tools."

### **Conclusion**

Xilinx has made profound improvements in both static and dynamic power in the Virtex-4 90 nm family of FPGAs when compared to Virtex-II Pro FPGAs – and (we believe) in comparison to our competitors. We have done this through a multi-pronged, purposeful approach in the areas of reduced leakage current, reduced dynamic power consumption, and embedded functions, without compromising performance. These, along with comprehensive power planning tools, make the Virtex-4 device an excellent choice for a high-performance FPGA system.

For more information about power consumption in Virtex-4 and other Xilinx FPGAs, visit <a href="https://www.xilinx.com/products/design\_resources/design\_tool/grouping/power\_tools.htm">www.xilinx.com/products/design\_resources/design\_tool/grouping/power\_tools.htm</a>.

### Virtex-4 Embedded Functions and Reduction of Dynamic Power

- PowerPC 50% power reduction compared to Virtex-II Pro PowerPC

- 10:1 power reduction over FPGA fabric-built version

- DSP XtremeDSP<sup>TM</sup> slice greatly reduces logic cells, which previously needed many filtering functions

- 20:1 power reduction over Virtex-II Pro separated multiply/accumulate functions

- SSIO New ChipSync<sup>TM</sup> block reduces logic cell count for SSIO (source synchronous I/O) designs

- Significant logic cell savings for various memory and networking interface designs leads to reduction in overall power up to 9:1 for selected designs (see Table 3)

- Embedded Ethernet MAC(s) No need to use logic and interconnect for MAC function, which saves

>3,000 logic cells for the Xilinx implementation

- FIFO SmartRAM<sup>TM</sup> memory includes built-in FIFO controllers, which can save hundreds of logic cells per FIFO and greatly simplify design as well

### 凸

# Deliver Efficient SPI-4.2 Solutions with Virtex-4 FPGAs Virtex-4 devices offer an ideal platform for source-synchronous

Virtex-4 devices ofter an ideal platform for source-synchronous designs like the widely adopted SPI-4.2 interface.

by Chris Ebeling

Principal Engineer

Xilinx, Inc.

chris.ebeling@xilinx.com

Krista Marks

Sr. Manager, IP Solutions Division

Xilinx, Inc.

krista.marks@xilinx.com

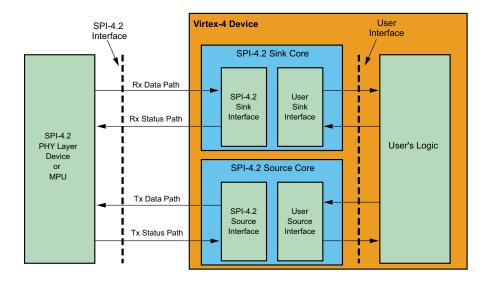

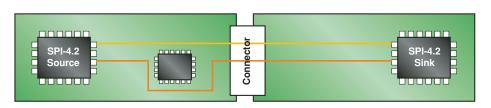

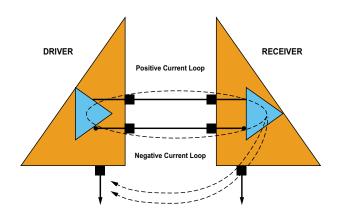

SPI-4.2 (System Packet Interface Level 4 Phase 2) is the Optical Internetworking Forum's recommended interface for the interconnection of devices for aggregate bandwidths of OC-192 (ATM and POS) and 10 Gbps (Ethernet), as illustrated in Figure 1.

In the last few years, this interface has become the de-facto standard on all leading 10 Gbps framer ASSPs and has been implemented directly on many next-generation network processors. SPI-4.2 has been broadly adopted because of its efficient interface, which offers high bandwidth with a low pin count and seamless handling of typical system requirements such as flow control, error insertion/detection, synchronization, and bus re-alignment.

The Xilinx® Virtex-4<sup>TM</sup> architecture provides an ideal platform for implementing SPI-4.2. The Xilinx SPI-4.2 LogiCORE<sup>TM</sup> IP targeting Virtex-4 devices provides a solution with one-third less resources, dramatic power savings, 1+Gbps LVDS double-data-rate (DDR) I/O, and complete pin assignment flexibility.

### **SPI-4.2 LogiCORE IP**

Xilinx has improved on its Virtex-II<sup>TM</sup> and Virtex-II Pro<sup>TM</sup> SPI-4.2 solution, already one of the smallest in the industry, and made it 30% smaller by leveraging new ChipSync<sup>TM</sup> technology in the Virtex-4 FPGA. ChipSync technology is supported on every pin of the Virtex-4 device family; thus the new SPI-4.2 LogiCORE IP can be targeted to any device pin-out. This allows you to select I/O pins that best fit your system and PCB requirements.

In addition, for those applications requiring multiple SPI-4.2 interfaces, the Virtex-4 FPGA's logic density, high pin count, and extensive clocking resources will support four or more full-duplex cores in a single device. Regardless of the performance your application requires,

Virtex-4 devices fully support the entire SPI-4.2 operating range, with high-speed LVDS support of data rates greater than 1 Gbps per pin.

### ChipSync Technology

Xilinx introduced ChipSync technology in Virtex-4 FPGAs to enhance I/O capability when used for source-synchronous applications like SPI-4.2. ChipSync features are supported in every Virtex-4 I/O pin and include:

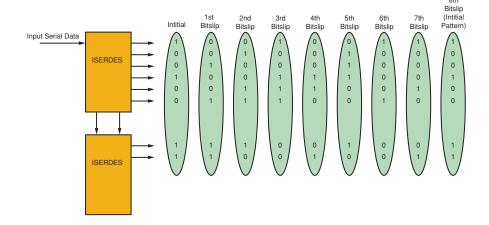

- New serial and de-serial (OSERDES and ISERDES) features. This enables logic built in the fabric to interface to the I/O at a fraction of the source-synchronous clock rate. The ISERDES also includes a Bitslip function. Bitslip allows you to shift the starting bit of deserialized data to achieve proper word alignment when linking multiple pins together (bus deskew).

- A new input delay (IDELAY) feature. This allows you to precisely adjust the input delay of each bit of a bus independently, in 78 ps increments. This provides a mechanism for tuning the interface timing to the system environment.

First Quarter 2005

20 Xcell Journal

Figure 1 - Typical SPI-4.2 application

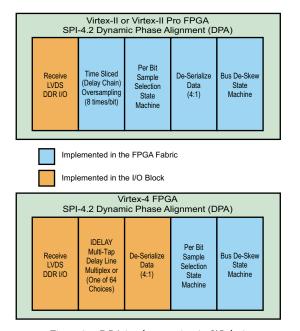

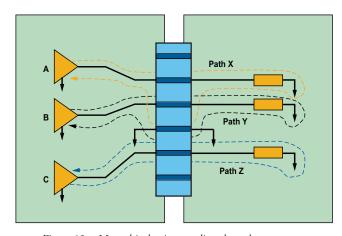

Figure 2 – DPA implementation in I/O logic for Virtex-II devices versus Virtex-4 devices

Additional DDR registers are now fully integrated into the input (ILOGIC) and output (OLOGIC) pins, simplifying the interface between the FPGA fabric and I/O blocks and supporting data transfer to and from the I/O logic on a single clock edge.

### SPI-4.2 and ChipSync Technology

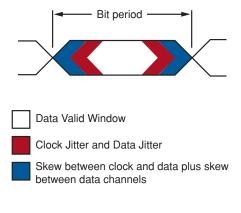

The SPI-4.2 interface has a DDR source-synchronous data bus that comprises 18 LVDS pairs (16 data bits, 1 control bit, and 1 clock). The SPI-4.2 source-synchronous clock varies from 311 MHz to 500 MHz.

For example, a typical OC-192 framer will require an aggregate bandwidth of 10 Gbps, which for a 16-bit dual data rate bus would require a data clock of at least 311 MHz, with 350 MHz a typical clock rate. The Xilinx SPI-4.2 LogiCORE IP easily meets your application requirements, regardless of performance, and with Virtex-4 ChipSync technology delivers a solution that is smaller and more flexible then prior FPGA implementations.

The SPI-4.2 core uses ChipSync technology to serialize egress data and de-serialize ingress data to a four-word (bus cycle) SPI-4.2 data stream at a lower clock rate. Operation of the core logic at a lower internal clock rate

allows you to implement high-frequency SPI-4.2 interfaces in the slowest speed grade Virtex-4 device.

The ISERDES and OSERDES functions allow the core logic to time multiplex and de-multiplex these four words to and from the I/O logic without using any CLB logic resources. The core logic need only operate at half the source-synchronous DDR clock rate. For example, a SPI-4.2 interface with a 500 MHz DDR reference clock would only require an FPGA fabric clock of 250 MHz – easily achievable in the Virtex-4 architecture.

As the frequency of the source-synchronous clock increases, data recovery at the receiving (sink) device becomes more challenging. The SPI-4.2 protocol provides a calibration data, or training pattern, that permits a receiving device to adjust its data sampling to the system interface timing. The process of tuning the interface to its particular timing is referred to as dynamic phase alignment (DPA).

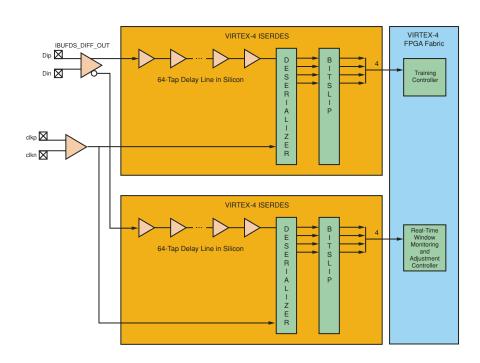

Before Virtex-4 devices, Xilinx DPA solutions worked by over-sampling the input data and choosing the best sample from the group. This required valuable FPGA resources and careful control of the input data path in the FPGA fabric, restricting the SPI-4.2 interface pin placement. In Virtex-4 FPGAs, the IDELAY feature present in every I/O is ideally suited to perform this function, as shown in Figure 2. (See "Dynamic Phase Alignment with ChipSync Technology in Virtex-4 FPGAs," also in this issue of the *Xcell Journal*).

The IDELAY features have two primary benefits for the SPI-4.2 core in Virtex-4 FPGAs:

- Integrating the IDELAY feature into the input pin (ILOGIC) reduces the FPGA resources required for DPA to less than 350 slices.

- The IDELAY function's ability to adjust the data sampling point enables DPA to be implemented in the I/O except for a small control state machine, which is implemented in the fabric. The state machine portion is fully synchronous and does not require a complex macro. Thus, there are no restrictions on SPI-4.2 pin assignments.

### **Clocking Resources**

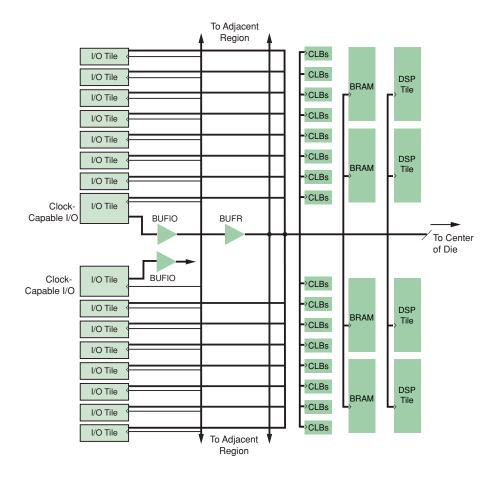

Virtex-4 FPGAs provide an unprecedented number of clock resources for implementing multiple SPI-4.2 interfaces in a single device. With the Virtex-II and Virtex-II Pro architectures, implementing more than two SPI-4.2 interfaces posed a clock management challenge. The abundance and flexibility of clock distribution in the Virtex-4 family solves this challenge, supporting as many SPI-4.2 interfaces as the device logic and I/O will allow.

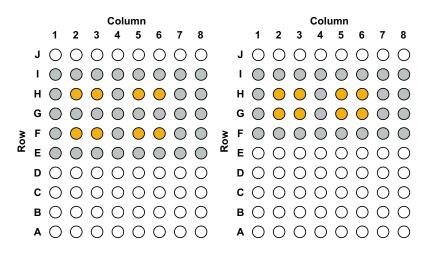

In Virtex-4 devices, all devices have 32 global clock resources. No restrictions exist on global clock distribution other than a maximum of eight global clocks per clock region. All clock regions have access to any 8 of the 32 total global buffers, regardless of the requirements of other clock regions.

In addition to the eight global clocks, each region in the device has two regional clock buffers. The regional clock resources are ideal for interface clocking, like the source-synchronous clock scheme used by SPI-4.2. Note that even the smallest Virtex-4 device has a total of 48 available clock resources, each designed for low-skew clock distribution and clock power management. The SPI-4.2 LogiCORE IP can be configured to use either global or regional clock resources.

In Virtex-4 FPGAs, the global clock trees and associated buffers are implemented differentially, for best duty-cycle fidelity and greater common-mode noise rejection. With Virtex-II and Virtex-II Pro devices, if SPI-4.2 interface operates above 350 MHz, you must route the high-speed reference clock using two clock buffers to minimize duty-cycle distortion at the DDR registers.

Figure 3 – Illustration of four SPI-4.2 LogiCORE IP implemented on a Virtex-4 XC4VLX60 device

interfaces in the larger devices (Figure 3). The Virtex-4 clocking capability opens up a whole new class of SPI-4.2 applications, and provides an ideal platform for applications such as multiplexing and de-multiplexing, bridges, and switches.

|                                                       | VIRTEX-II         | VIRTEX-II PRO     | VIRTEX-4        |

|-------------------------------------------------------|-------------------|-------------------|-----------------|

| Power: Static Alignment<br>@ 700 Mbps per LVDS Pair   | 1.9W              | 1.75W             | 1.55W           |

| Power: Dynamic Alignment<br>Performance per LVDS Pair | 2.6W<br>@800 Mbps | 2.8W<br>@944 Mbps | 2.0W<br>@1 Gbps |

| Speed Grades Supporting<br>800 Mbps per LVDS Pair     | -6                | -6, -7            | -10, -11, -12   |

Table 1 – SPI-4.2 power estimates for Virtex-II, Virtex-II Pro, and Virtex-4 FPGAs

Because each global clock tree in Virtex-4 FPGAs is implemented differentially, only one clock buffer is required.

Not only does the Virtex-4 architecture have considerably more clock resources, but because they are distributed differentially, the SPI-4.2 LogiCORE IP requires fewer of them. These high-performance clock resources support as many as four SPI-4.2 interfaces in a mid-range device (LX40/LX60) and more than four SPI-4.2

### **Higher Performance at Lower Power**

Virtex-4 silicon is manufactured with a triple-oxide process that reduces static power consumption by 40%. This will have a positive impact for all designs, including the SPI-4.2 interface, where the power savings are dramatic, as readily illustrated and summarized in Table 1.

With Virtex-4 devices, SPI-4.2 uses significantly less power than its Virtex-II and Virtex-II Pro predecessors, both because of

the enhanced 90 nm semiconductor process and because the LogiCORE IP uses 30% less fabric resources. At the same time, Virtex-4 FPGAs support 30% higher internal performance for SPI-4.2, with a maximum frequency of 250 MHz in the lowest speed grade (compared to 175 MHz in the lowest speed grade of Virtex-II and Virtex-II Pro devices). In addition, Virtex-4 FPGAs support 1+ Gbps LVDS for every I/O on the device.

This means that not only can you place multiple SPI-4.2 interfaces anywhere on the device, but for each implemented interface you get an aggregate bandwidth as high as 16+ Gbps. Designs that do not require this level of performance (such as more typical framer interfaces running at 10-12 Gbps) automatically get additional performance overhead that ensures ease of design integration and timing closure.

### **Conclusion**

The Xilinx SPI-4.2 LogiCORE IP, coupled with Virtex-4 features, provides a highly efficient SPI-4.2 solution. We developed ChipSync technology that supports every I/O pin specifically for source-synchronous interfaces like SPI-4.2.

This technology enables you to design the most efficient SPI-4.2 solution, which uses significantly less resources (35% less), allows fully flexible device pin assignments (you choose the pinout), and supports extremely high interface speeds (1+ Gbps LVDS DDR I/O).

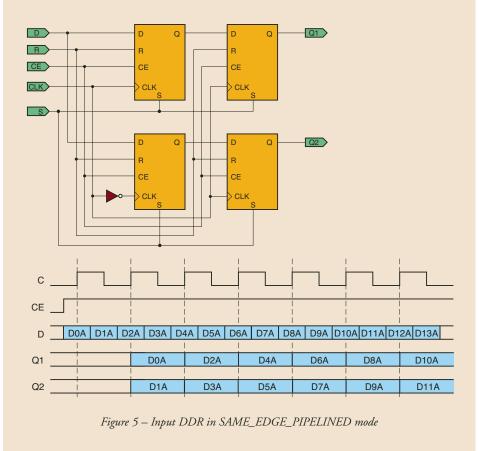

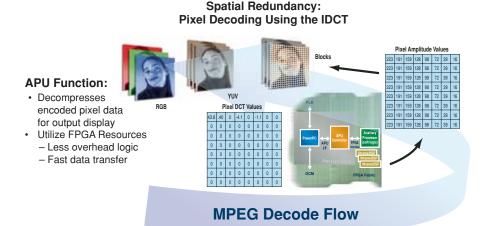

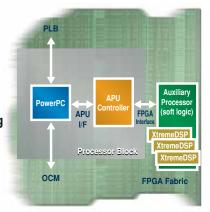

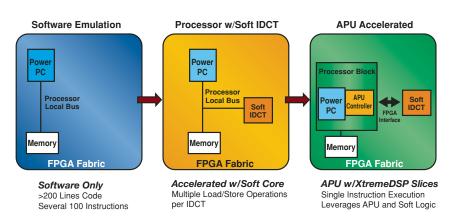

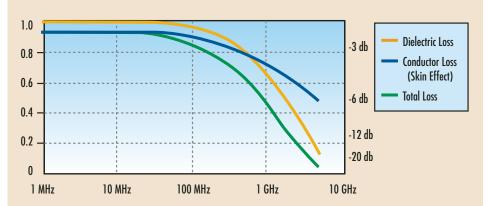

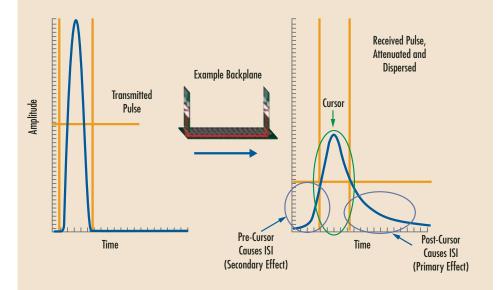

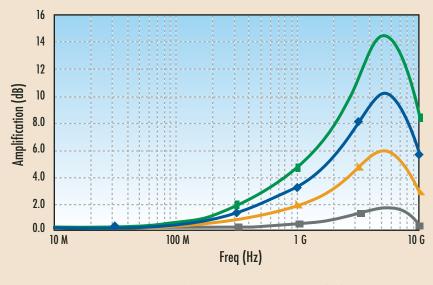

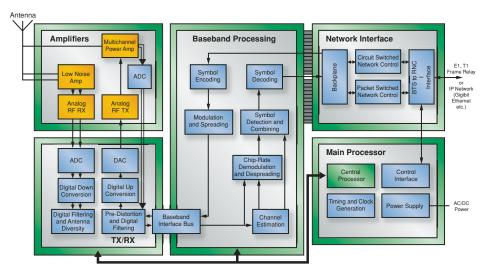

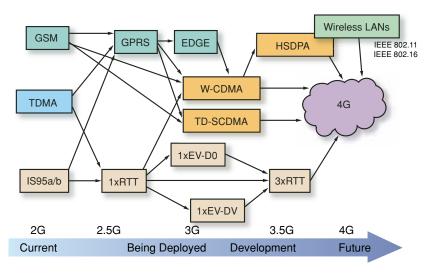

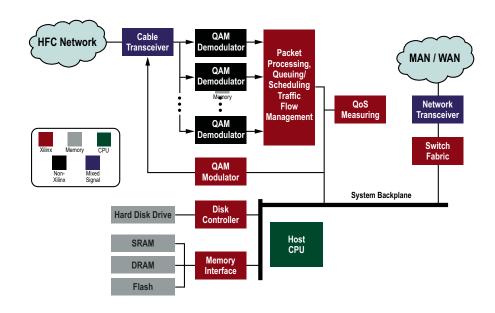

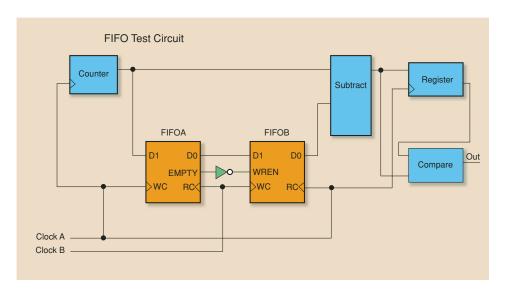

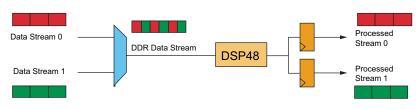

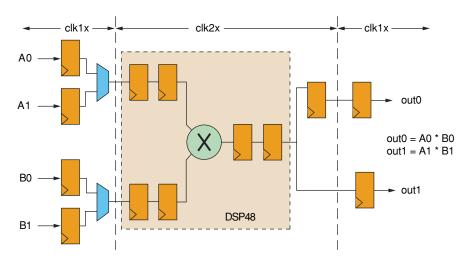

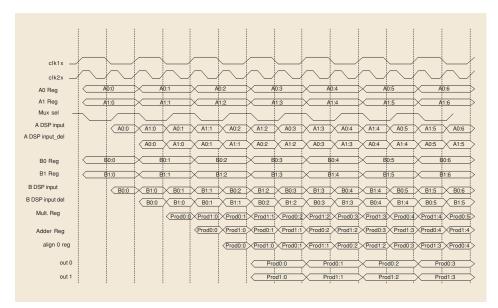

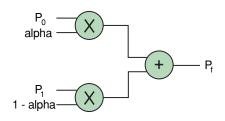

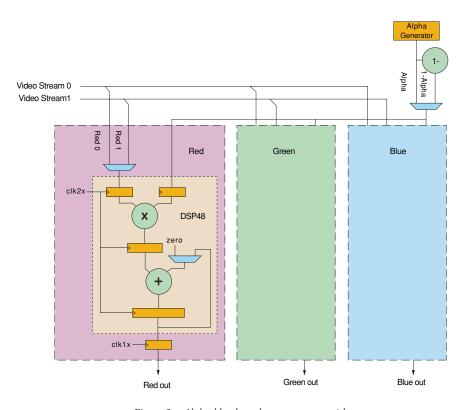

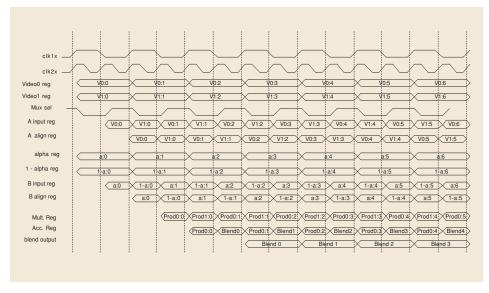

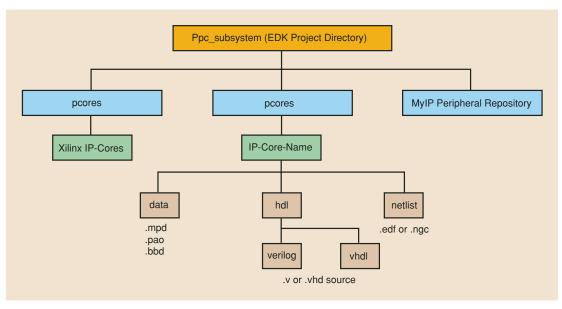

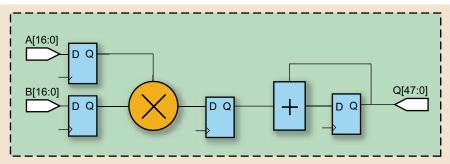

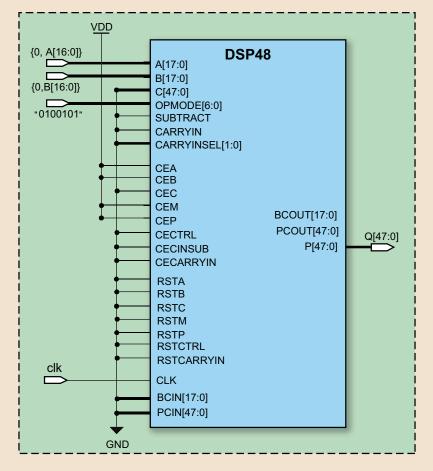

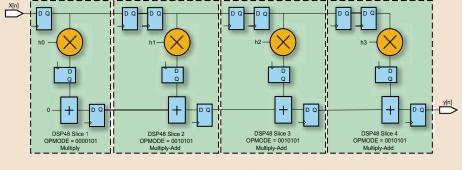

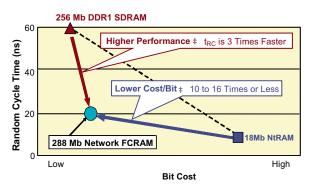

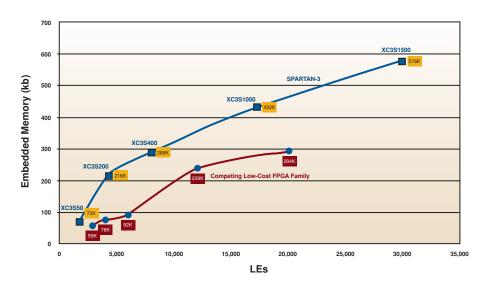

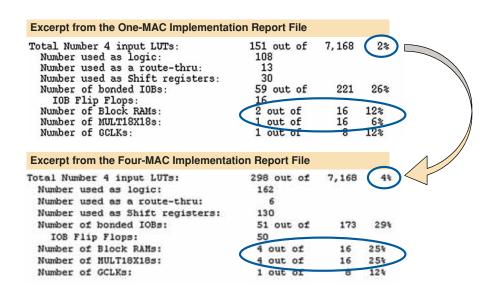

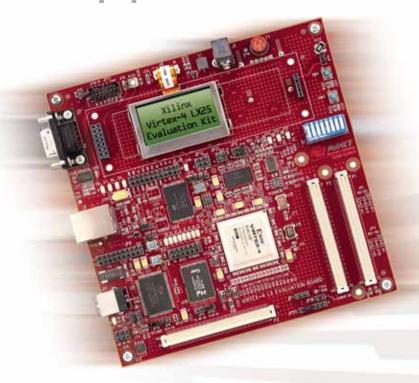

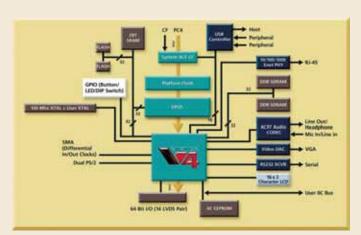

The higher performance is even more compelling because Virtex-4 FPGAs deliver it with lower power and significantly higher internal operating rates. The wealth of Virtex-4 clocking resources, combined with full pin assignment flexibility, opens up the possibility for new applications with multiple SPI-4.2 interfaces.