### Reduce Your System Power Consumption with Altera FPGAs

### Agenda

- Benefits of lower power in systems

- Stratix<sup>®</sup> III power technology

- Cyclone<sup>®</sup> III power

- Quartus<sup>®</sup> II power optimization and estimation tools

- Summary

# **Benefits of Lower Power**

- Stay within a fixed power budget

- Chassis limits (heat, space, current)

- Battery life considerations

- Outside power budget  $\rightarrow$  not an option

- Reduce system cost

- Fewer/smaller heat sinks and fans

- Smaller power supplies

- Increase reliability

- No fans  $\rightarrow$  no moving parts

- Lower system temperature

- Reduce design time and effort to meet power and thermal constraints

- Reduce ongoing operating costs

© 2007 Altera Corporation—Public

Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation

3

# **Altera Power Strategy at 65 nm and Beyond**

- Innovative architecture and advanced process technologies

- Best-in-class FPGA power modeling

- Lowest power solution in the industry

### **Power Components and Terminology**

- Core static power

- Power consumed even when there are no clocks active; power due to leakage currents

- Static power is function of device selected and junction temperature

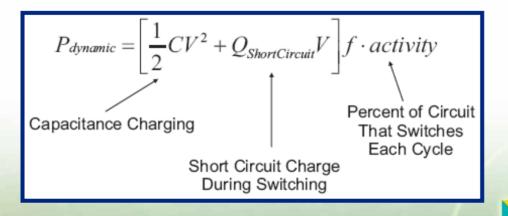

- Dynamic power

- I/O power

- Charging and discharging external load capacitance connected to device pins, I/O drivers, and external termination network (if present)

- Block power

- Power for individual device resources such as the logic elements (LEs), phase-locked loops (PLLs), or memory blocks

- Total power = core static power + dynamic power (I/O + block)

# **Stratix III Power Technology**

## **Meeting the Power Challenge**

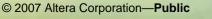

### Stratix III FPGAs Cut Power by 50% vs. 90 nm

© 2007 Altera Corporation—Public

Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation

7

### **Lowest Power FPGA in the Industry**

| Stratix III FPGA Power<br>Reduction Technique                    | Lower Static<br>Power | Lower<br>Dynamic<br>Power |

|------------------------------------------------------------------|-----------------------|---------------------------|

| Silicon Process Optimizations                                    | ✓                     | $\checkmark$              |

| Selectable Core Voltage<br>(0.9 V or 1.1 V)                      | ✓                     | $\checkmark$              |

| Programmable Power Technology                                    | ✓                     | $\checkmark$              |

| Power Optimized DDR Memory Interface                             | ✓                     | $\checkmark$              |

| Quartus II Software PowerPlay<br>Power Analysis and Optimization | ✓                     | $\checkmark$              |

© 2007 Altera Corporation—Public

Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation

8

### Leading Edge Process Technology Increased Performance, Reduced Power

- Advanced 65-nm process

- 15% capacitance reduction  $\rightarrow$  reduces dynamic power 15%

- Lower voltage  $\rightarrow$  reduces dynamic power another 16%

- Multiple-gate oxide thicknesses (triple oxide)

- Trade-off static power vs. speed per transistor

- Multiple-threshold voltages

- Trade-off static power vs. speed per transistor

- Low-k inter-metal dielectric

- Reduces dynamic power, increases performance

- Strained silicon

- Increased performance

- Copper interconnect

- Increased performance, reduced IR drop

© 2007 Altera Corporation—Public

# **Selectable Core Voltage**

### **Selectable Core Voltage**

### Customer selects the FPGA core voltage

- 1.1 V for maximum performance

- 0.9 V for minimum power

### I/O and PLL voltages unaffected

- Still get maximum I/O interface speed

- Crucial, since I/O bandwidth limits many systems

| Nominal<br>Voltage | Min.<br>Regulator<br>V <sub>оυт</sub> | Max.<br>Regulator<br>V <sub>OUT</sub> | Slow Timing<br>Model | Fast Timing<br>Model | Power Model |

|--------------------|---------------------------------------|---------------------------------------|----------------------|----------------------|-------------|

| 1.1 V              | 1.05 V                                | 1.15 V                                | ✓                    | ✓                    | ✓           |

| 0.9 V              | 0.86 V                                | 0.94 V                                | ✓                    | × /                  | ✓           |

© 2007 Altera Corporation—Public

### **Power and Timing Impact**

| Core Voltage         | Dynamic Power<br>Reduction From<br>Stratix II FPGAs | Static Power<br>Reduction From<br>Stratix II FPGAs | Performance Gain<br>Over Stratix II<br>FPGAs |

|----------------------|-----------------------------------------------------|----------------------------------------------------|----------------------------------------------|

| 1.1 V <sup>(1)</sup> | 33%                                                 | 52%                                                | 35%                                          |

| 0.9 V <sup>(2)</sup> | 55%                                                 | 64%                                                | 8%                                           |

Notes:

- (1) Fastest vs. fastest speed grade comparison

- (2) Slowest vs. slowest speed grade comparison

### More Choice to Meet Your Power and Performance Budgets

© 2007 Altera Corporation—Public

### 60% Lower Static Power (85°C)

Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation

13

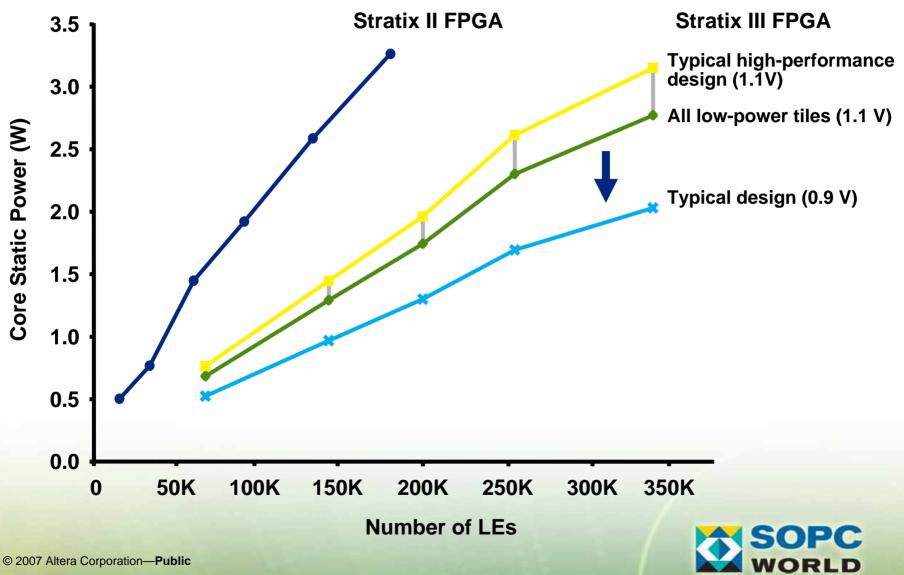

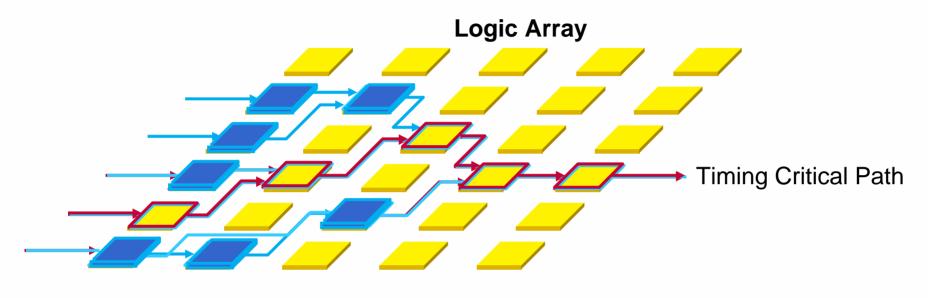

### **Design-Specific Power Optimization**

Only a small fraction of logic is performance critical

Slack Histogram

Slack %

© 2007 Altera Corporation—Public

Logic Array **Timing Critical Path**

High-Speed Logic

© 2007 Altera Corporation—Public Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation 16

© 2007 Altera Corporation—**Public** Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation

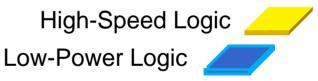

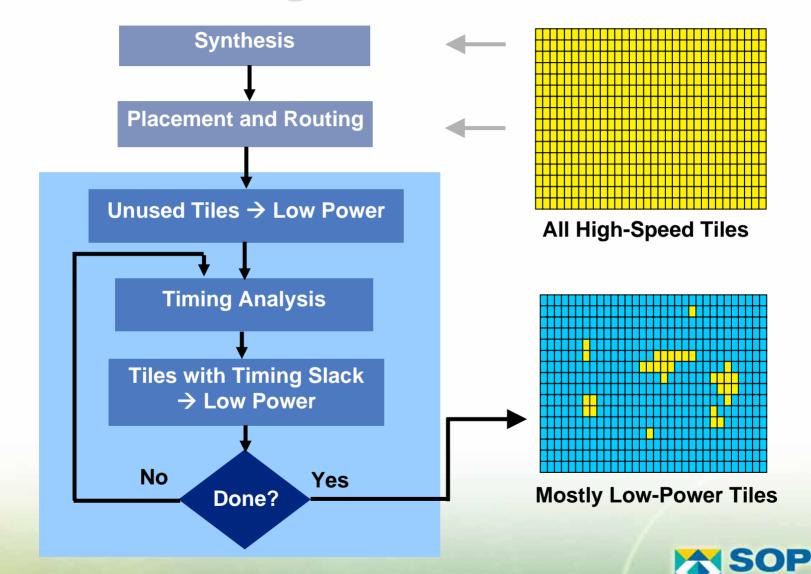

\* Power mapping fully automated by Quartus II software based on timing constraints

High-Speed Logic

Low-Power Logic

### Unused Low-Power Logic

### High Performance Where You Need It, Lowest Power Everywhere Else

© 2007 Altera Corporation—Public

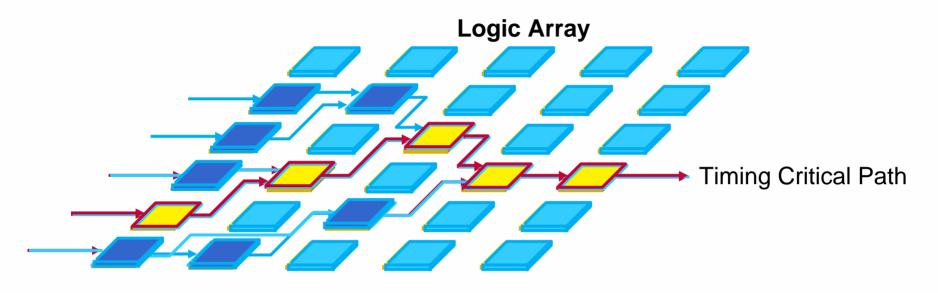

# **High-Resolution Power Control**

Stratix III FPGA (EP3SL340) has **8,050 tiles** for very highresolution power/performance optimization

Only a small percentage of highspeed tiles required to maintain design performance

### Speed of the Fastest LABs, Power of the Slowest

© 2007 Altera Corporation—Public

### **Stratix III: Highest Performance**

Note: Benchmarking data is based on comparing an Altera device to an equivalent Xilinx device using Quartus II V7.2 and ISE 9.2iSP1 software

#### © 2007 Altera Corporation—Public

Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera

Quartus 7.2 will be available in October of 2007

20

# **Using Programmable Power**

- Circuit board requirements: none!

- Stratix III FPGAs create low-power tiles using on-chip circuitry

- No extra power supplies, no extra board components

- Design changes: none!

- Quartus II software automatically uses high-speed tiles where needed for timing

- All unused tiles set to low power

- All tiles with timing margin set to low power

- Failed timing constraints: all tiles not on critical paths set to low power

© 2007 Altera Corporation—**Public** Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation 21

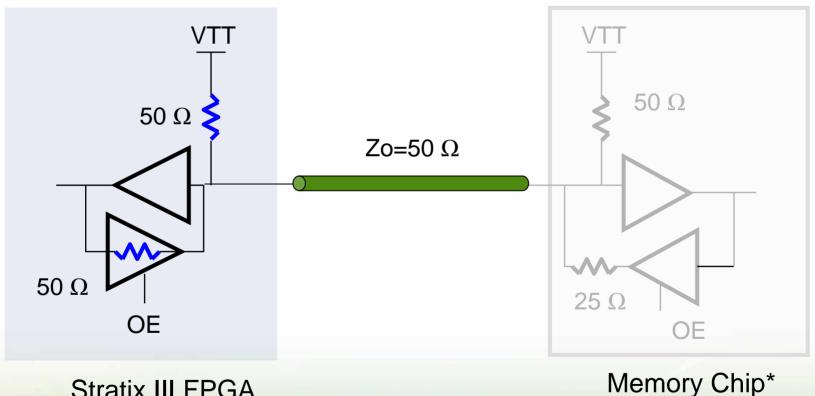

### Power-Optimized DDR Memory Interface

# **Stratix III On-Chip Termination (OCT)**

Both parallel (Rt=50 $\Omega$ ) and series (Rs=50 $\Omega$ ) termination

### Stratix III FPGA

#### (\*) DDR 1/2/3, RLDRAMII, QDR II/II+ support

© 2007 Altera Corporation—Public

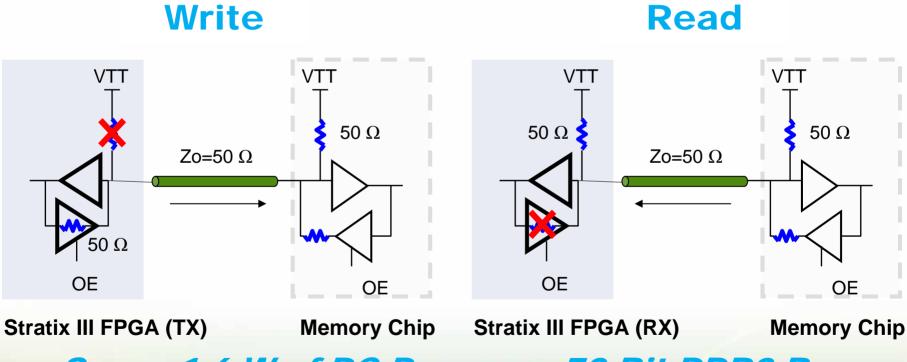

# **Stratix III FPGA Dynamic OCT**

- Write: Rs on, Rt off  $\rightarrow$  Matching line impedance

- Read: Rs off, Rt on → Terminating far end

### Saves 1.6 W of DC Power on 72-Bit DDR2 Bus

© 2007 Altera Corporation—Public

# **Benefits of Dynamic OCT**

- 1. Power significantly reduced vs. traditional parallel OCT

Saves 1.6 W of DC power on 72-bit DDR2 bus

- 2. Proper line termination and impedance matching on bidirectional busses

- Enhanced signal integrity

- 3. No need for on-board termination resistors

# **Stratix III FPGAs Support DDR3**

- Stratix III FPGA: the only FPGA that supports DDR3

- DDR3 consumes 30% lower power than DDR2

- DDR2: 1.8 V

- DDR3: 1.5 V

- Example system:

- 72-pin, 200-MHz memory interface, with on-chip termination

- Conventional FPGA DDR2 power: 3.9 W

- Stratix III (dynamic OCT) DDR2 power: 2.3W

- Stratix III (dynamic OCT) DDR3 power: 1.6W

- Total savings of 2.3 W

© 2007 Altera Corporation—Public

26

# **Cyclone III Power Advantages**

© 2007 Altera Corporation—Public

# **Cyclone III Silicon Design Strategy**

- Maintain performance while reducing power

- Utilize latest process technology and features available for low-power design

| Process or Technology             | Benefit                                                                                                              |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Multi-threshold transistors       | Balance need for performance and low power consumption                                                               |

| Variable gate-length transistors  | Balance need for performance and low power consumption                                                               |

| TSMC 65-nm low-power (LP) process | Reduced FPGA power consumption using<br>the same low-power process technology<br>employed for mobile phone chip sets |

© 2007 Altera Corporation—Public

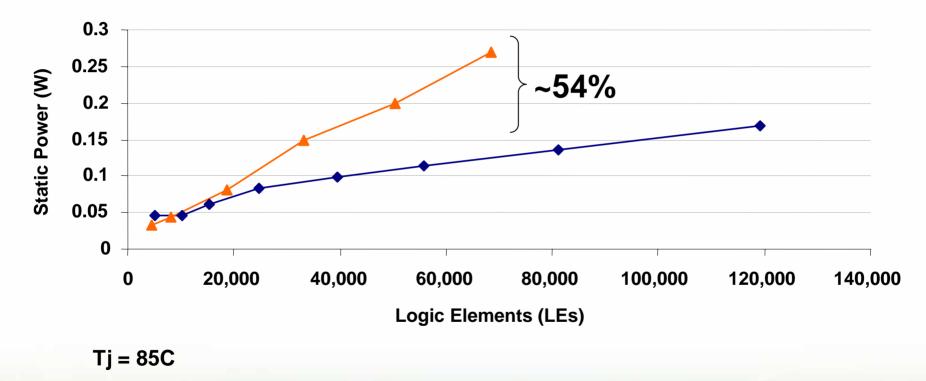

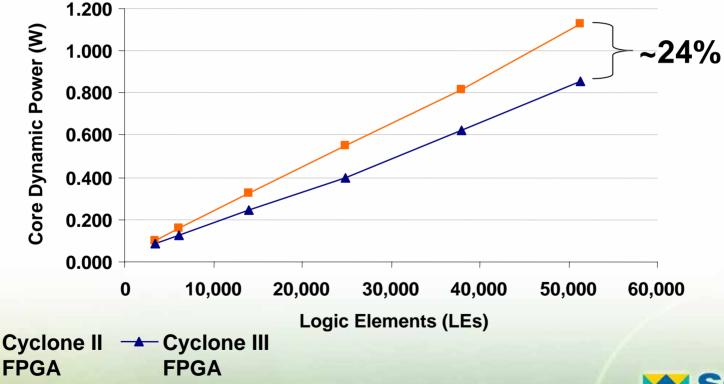

# **Cyclone III Power Consumption Advantage**

| Power Component      | Cyclone III Devices Power Reduction Over<br>Cyclone II Devices <sup>(1)</sup> |  |

|----------------------|-------------------------------------------------------------------------------|--|

| Typical Static Power | Up to 54%                                                                     |  |

| Core Dynamic Power   | Up to 24%                                                                     |  |

| I/O Power            | Comparable                                                                    |  |

Notes:

(1) Based on Cyclone III EPE v7.0 beta and Cyclone II EPE v.6.1

© 2007 Altera Corporation—**Public** Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation 30

# **Core Static Power Comparison (85C Tj)**

Cyclone III FPGA benefits grow as Tj and density increase

Cyclone II - Cyclone III FPGA FPGA

© 2007 Altera Corporation—Public

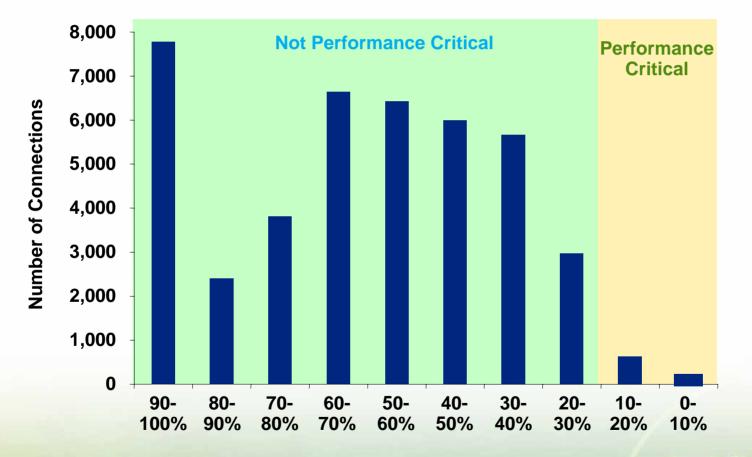

# **Core Dynamic Power**

- Does not vary with temperature

- Function of frequency, number of circuits switching, and capacitance

- All of the Cyclone III device blocks consume less dynamic power than Cyclone II device blocks except for the PLL blocks

© 2007 Altera Corporation—Public

### Quartus II Power Optimization and Estimation Tools

### **Automatic Programmable Power**

© 2007 Altera Corporation—Public

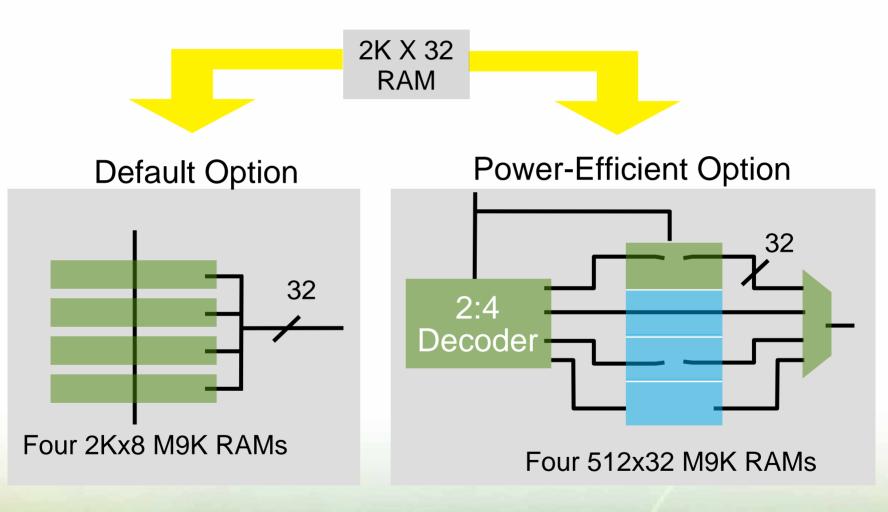

## **Example: Power-Optimized RAM Mapping**

© 2007 Altera Corporation—Public

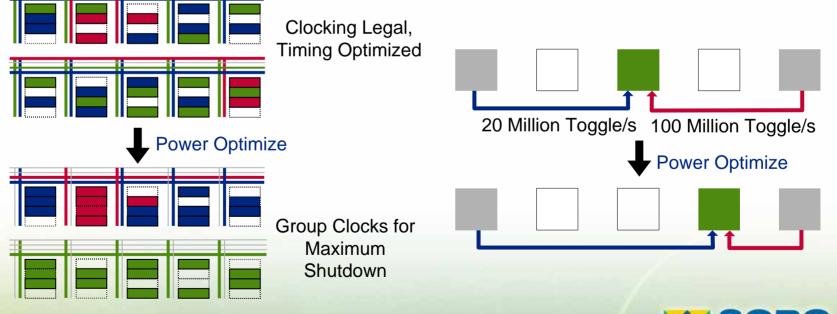

# **Logic and Clock Power Optimization**

### Clock power reduction

- Stratix III hardware can shut down clock at 3 levels of tree

- Automatic placement to reduce clock power

- Power-driven placement and routing

- Minimize capacitance of high-toggling signals

- Without violating timing constraints

© 2007 Altera Corporation—Public

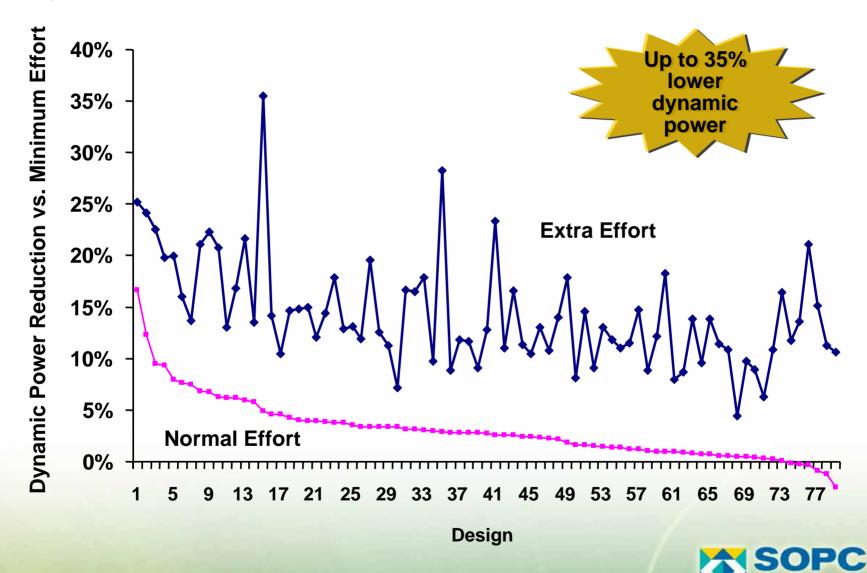

### **Dynamic Power Optimization**

ORLD

© 2007 Altera Corporation—Public

Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation

37

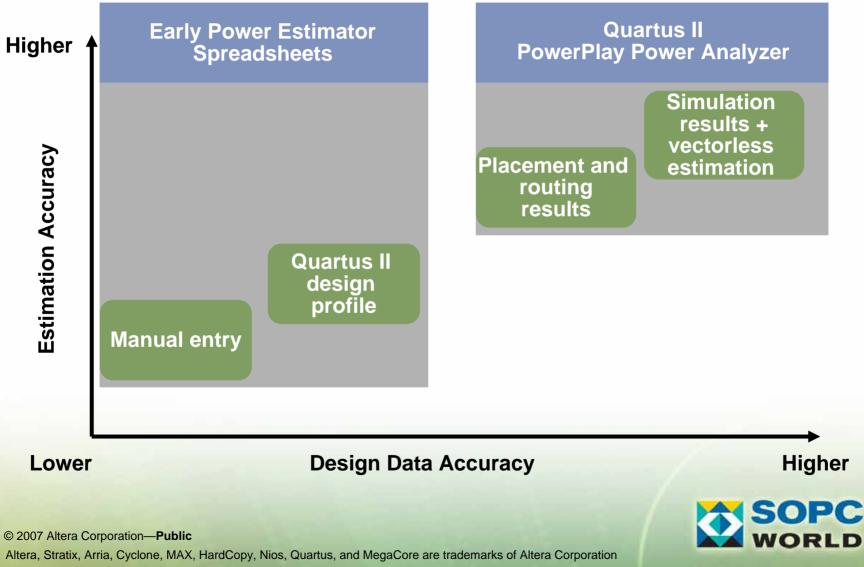

### **Design Data Accuracy vs. Estimation Accuracy**

38

### **Early Power Estimator Spreadsheets**

- Enter in design data manually if design files are not available

- Quartus II software automatically generates design data inputs

- Supports quick "what-if" analysis

- Download from Altera<sup>®</sup> website

| Input                           | Early Power Estimator -> Reports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of Registers             | By Resource                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ransition Rates                 | By Resource<br>By Resource<br>By Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| locks and Frequency             | Ingut Parameters Supply Current (A)  Supply Power (B)  Device   Tokens  Tokens |

| O and Memory                    | Thermal Analysis  Thermal Analysis  Thermal Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SP and PLLs                     | Of Registed      Dime Tested integr.      All Th.      Good      Dime Tested integr.      O Control        10      Castion 01, (COR)      6.00      800      Station 10, (COR)      5.00        10      Castion 01, (COR)      6.00      91, Statid      3.00      3.00        10      Castion 01, (COR)      6.00      91, Statid      3.00      3.00        10      Castion 01, (COR)      6.00      91, Castion 10, and (COR)      6.01        10      Castion 01, (COR)      6.00      91, Castion 10, and (COR)      6.01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Temp, Air Flow, Heat<br>Sinking | TE Class Colls P1 600 0, Standard Addition<br>Class Colls Banany 520 S., Machines Repúblic TE 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

### **Estimate Power Before Design Files Available**

© 2007 Altera Corporation—Public

### **Quartus II Power Analyzer**

- Provides highest estimation accuracy by taking advantage of Quartus II software design data and simulation stimuli

- Vectorless estimation technology improves accuracy by plugging in holes not covered by test bench stimuli

| Input                   | > Power Analyzer>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Reports                |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Number of Registers     | ✓ PowerPlay Power Analyzer Tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | By Resource            |

| Transition Rates        | Input Be<br>IF Use input file to initialize toggle sates and static probabilities during power analysis<br>I and the same sate of the sate of | By Supply              |

| Clocks and Frequency    | Signal activity file: filtrel aaf  VCD file:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Бу Зарріу              |

| I/O and Memory          | Output file        Image: Write out signal activities used during power analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Thermal Analysis       |

| -                       | Output file nome: filte_out.saf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |

| DSP and PLLs            | Default toggle rates for unspecified signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Design Hierarchy Power |

| Temp, Airflow, Heat     | Default toggle rate used for input I/D signals: 50.0 %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                        |

| Sinking                 | C Use default value: 125 x v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Confidence Metrics     |

| Simulation Results      | 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Signal Activity Data   |

| Place-and-Route Results | 00.00.00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                        |

| Node Activity           | V Start Stop Report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                        |

### Available in All Versions of Quartus II Software

© 2007 Altera Corporation—Public

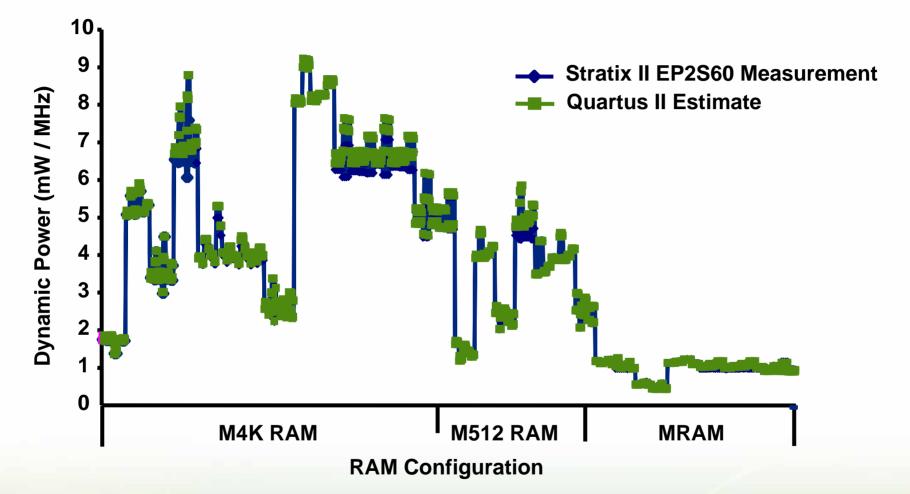

## **How Good Are Estimation Results?**

### Altera's rigorous modeling methodology

- Use detailed circuit HSPICE models

- Logic element, routing, I/Os, clocks

- Around 9000 simulation elements

- All models tested and calibrated against FPGA

- Customer designs tested as final check of quality

### Quality of user inputs and assumptions affects estimation accuracy

- Are the toggle rate assumptions accurate?

- Are the simulations reflective of real-world stimuli?

- How far off is LE count from the final design?

© 2007 Altera Corporation—Public

41

### **Model Correlation Example: RAM**

8700+ Designs Covering All FPGA Elements

© 2007 Altera Corporation—Public

# **Altera 65-nm Power Advantage**

- Innovative architecture and advanced process technologies

- Programmable Power Technology and selectable core voltage

- Stratix III FPGA consumes less than half the total power of Stratix II FPGA

- Cyclone III FPGA consumes less than half the static power of Cyclone II FPGA

- Best-in-class FPGA power modeling

- Allows power optimization

- Accurate power estimator

- Lowest power solution in the industry

- Stratix III FPGA consumes 45% lower power than Virtex-5

- Cyclone III FPGA consumes up to 80% lower power than Spartan-3

© 2007 Altera Corporation—Public

# Thank You!