Deliver Femtocell Basestations

Quickly and Cost Effectively with

Altera HardCopy Structured ASICs

# **Agenda**

- Femtocell overview

- Benefits and challenges

- Enabling low-cost, low-risk, fast time-to-market femtocell designs

- HardCopy<sup>®</sup> structured ASIC product overview

- Femtocell design using HardCopy structured ASICs

- Supporting intellectual property (IP) and reference designs

- Summary

## **A Complete Solutions Portfolio**

Intellectual Property (IP)

Design software

Development kits

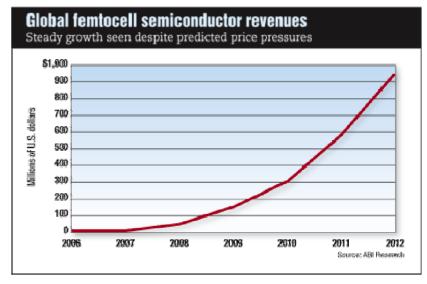

## **Altera's Wireless Market Focus**

#### **Mobile Infrastructure**

- BTS/NodeB/AP

- BSC/RNC

- aGW

- SGSN, GGSN, MGW

- RRH

#### **Broadband Wireless** Access

- WiMAX basestations and CPE

- Broadband microwave

Etherne

- Femtocell access point

- Pico BTS

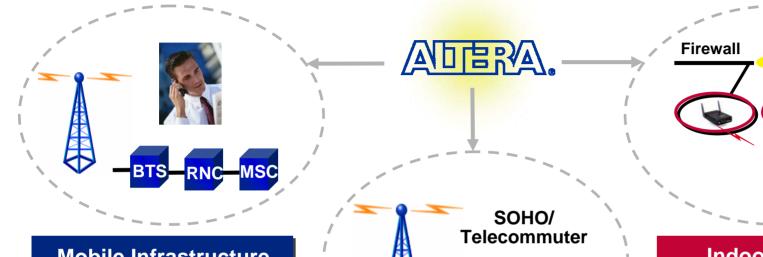

### **Femtocell Overview**

- Femtocell benefits for mobile operators

- Extend service coverage inside the home

- Capture wireline minutes

- Offload traffic off the macro network

- Decrease backhaul costs

- Stimulate 3G services uptake, ensure higher ARPU

- Lower customer churn

- Defend against VoIP erosion

- Provide FMC services → bundling

- Practical and attractive option for a fixed mobile convergence offering

- Reuse existing 3G handsets

(no need for dual-mode WiFi/3G handsets)

Source: ABI Research

# Challenges to Building a Femtocell

#### Technical:

- Small form factor for home use

- Thermal engineering

- Power is not an issue (plug into wall), but heat generation is

- High performance within cost budget

- Challenging network architecture

- RF interference and power control

- Network synchronization

- Core network integration

#### Business:

- Emerging market

- Uncertainty of adoption rate (how fast will it take off?)

- Equipment costs (device pricing)

- WiFi-like cost... \$100 target pricing for residential customer

- <\$50 BOM in late 2008</p>

- Fast product launches and short development cycles

- Suppliers race to capture contracts with carriers

# Addressing the Femtocell Design Challenges using HardCopy Structured ASIC Technology

# The only FPGA company with structured ASICs

- Low price points

- High performance

- Low power

# The only structured ASIC company with FPGAs

- Small up-front investment

- Fast turnaround time

- Guaranteed success

# HardCopy II Structured ASICs—Built for Low Cost

- \$15 for 1M ASIC gates

- 50%+ core power reduction from Stratix<sup>®</sup> II FPGA prototype

- Over 350-MHz system performance

- Up to 2.2M ASIC gates

Structured ASIC With Unique FPGA-Based Design Methodology

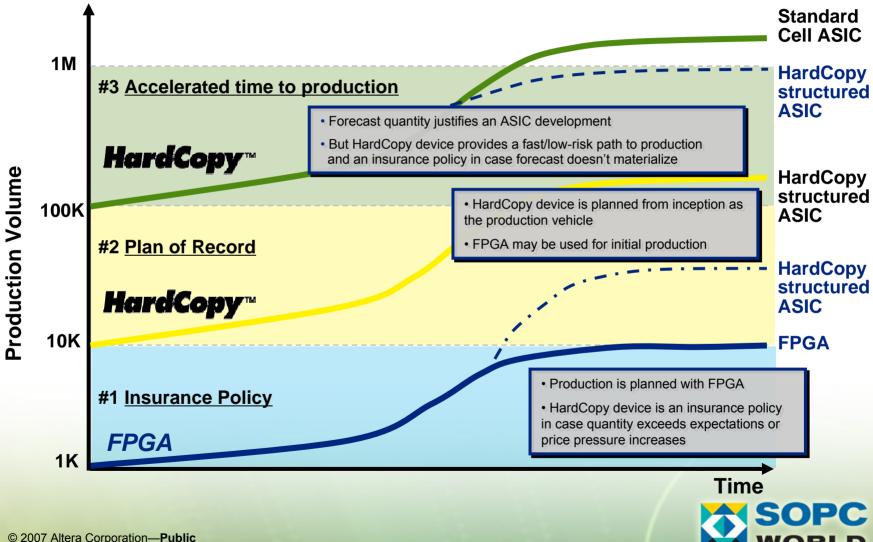

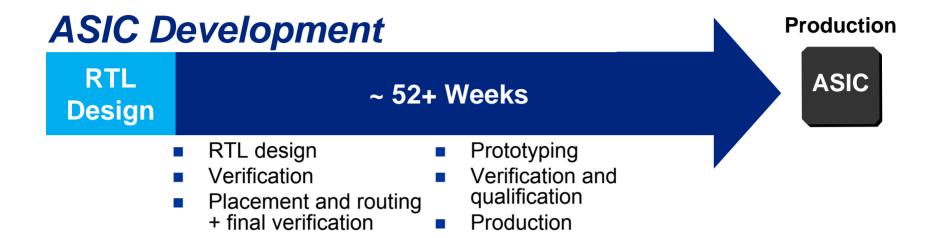

## **HardCopy Usage Models**

### **Fastest Time-to-Market**

#### HardCopy Development

## **HardCopy Series Benefits**

#### Silicon

- 50% faster than FPGA

- Up to 70% lower core power than the FPGA

- 60% to 85% smaller die

#### **Packaging**

- Pin-to-pin compatibility with FPGA

- Low-cost production packaging

- No printed circuit board respins

#### Software

- Unified FPGA and HardCopy design environment

- Power and performance management tools

- Inexpensive and easy to use

#### **Turnkey Migration**

- No test vectors

- No backend simulation or logic verification

## Proven Methodology Minimizes Risk

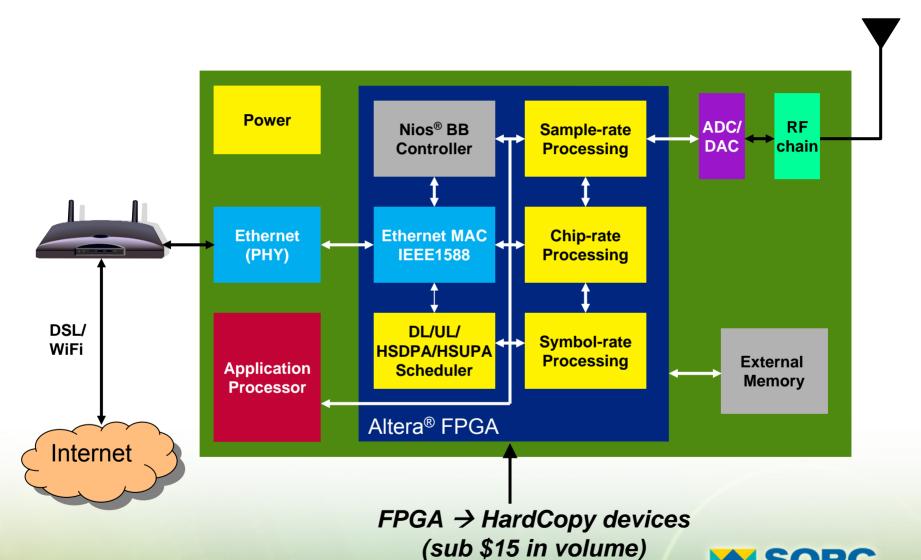

## Femtocell Architecture Example –WCDMA/HSxPA

© 2007 Altera Corporation—Public

## System Partitioning – 3GPP WCDMA/HSxPA

#### FPGA/HardCopy structured ASIC

- DUC, DDC, AGC, power meter

- (De)-scrambling/spreading/modulation, including HSxPA

- FEC: convolutional and turbo, including HSxPA

- Rate matching

- Physical channel mapping

- Rake/searcher/MRC/channel estimation

- DL/UL scheduling including HSxPA

- IPSec enscryption accelerators/crypto-engines

- Network timing synchronization (IEEE1588, NTP)

#### Application processor

- OAM

- Frame protocol termination

- Control-plane processing

- IMS/SIP signalling and protocol handling

- MAC/RLC/RRC/MSC/xGSN: collapsed stack processing

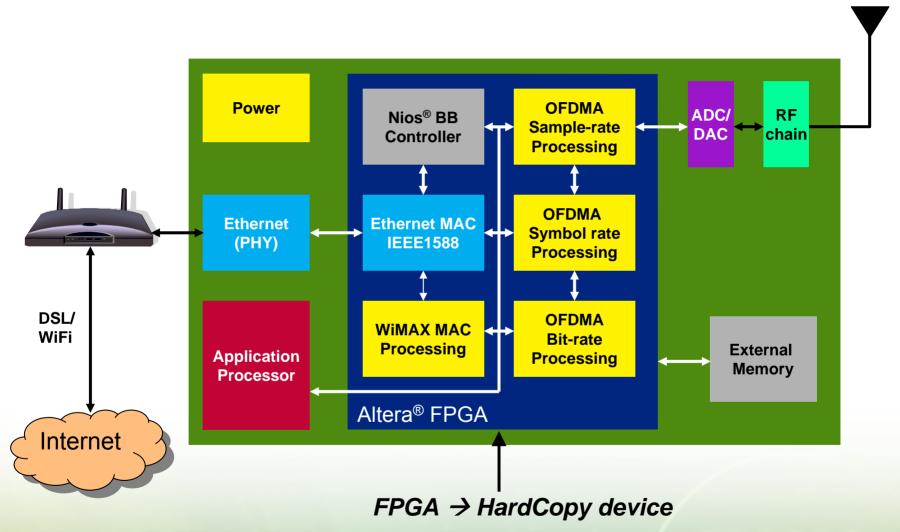

## Femtocell Architecture Example – Wimax 802.16e

# System Partitioning – Wimax 802.16e

#### FPGA/HardCopy structured ASIC

- DUC, DDC, AGC, power meter

- Ranging

- Channel estimation, channel equalization

- OFDMA engine

- Pilot insertion/extraction

- Subchannelization/extraction

- FFT/IFFT/CP

- Symbol (de)-mapper

- FEC

- IPSec enscryption accelerators/crypto-engines

- Lower MAC

- Network timing synchronization (IEEE1588, NTP)

#### Application processor

- OAM

- Host processing

- Access controller

- IMS/SIP signalling and protocol handling (VoIP SIM/IMS)

- TCP/UDP

- Upper MAC/scheduler

# Significant CDMA and OFDMA IP Expertise

| Standard          | Altera IP and reference designs                                | Partner IP and reference designs                                                |

|-------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------|

| 3GPP<br>Release 6 | <ul> <li>HSDPA and HSUPA channel coding coprocessor</li> </ul> | <ul><li>HSDPA and HSUPA turbo encoder and decoder</li></ul>                     |

|                   | <ul> <li>WCDMA DUC and DDC for macro,<br/>Pico BTS</li> </ul>  | <ul><li>Connectivity: CPRI 2.0,<br/>OBSAI RP3-01</li></ul>                      |

|                   |                                                                | <ul><li>Radio card: crest factor reduction,<br/>digital predistortion</li></ul> |

| WiMAX             | ■ Reed-Solomon encoder/decoder                                 | ■ Turbo convolutional code                                                      |

|                   | ■ Viterbi decoder                                              | ■ Turbo product code                                                            |

|                   | ■ CORDIC                                                       | ■ Complete 802.16e PHY and MAC                                                  |

|                   | ■ FFT/IFFT compiler                                            | ■ CPRI 2.0                                                                      |

|                   | Scalable OFDMA engine                                          | ■ OBSAI RP3-01                                                                  |

|                   | Channel estimation                                             |                                                                                 |

|                   | ■ Channel equalization                                         |                                                                                 |

|                   | ■ OFDMA ranging                                                |                                                                                 |

|                   | Symbol mapper/demapper                                         |                                                                                 |

|                   | <ul><li>Single and multi antenna</li><li>DUC and DDC</li></ul> |                                                                                 |

|                   | ■ PAPR reduction, i.e CFR                                      |                                                                                 |

# Other IP Offerings: Altera and Ecosystem

| IP type                        | IP description                                                       | Offered by        |

|--------------------------------|----------------------------------------------------------------------|-------------------|

|                                | Nios II embedded processor                                           | Altera            |

| Processor                      | Network stack: TCP/IP NicheStack Network Stack, Nios II edition      | Altera/InterNiche |

|                                | OS: MicroC/OS RTOS                                                   | Micrium           |

|                                | DDR2 memory controller (up to 266 MHz integrated PHY and controller) | Altera            |

| Memory controller              | DDR2 high performance controller (up to 333 MHz)                     | Altera            |

| Ethernet MAC                   | Low LE count Triple Speed Ethernet MAC (configurable to only 10/100) | Altera            |

| Ethernet WAC                   | 10/100 1000 1588 Ethernet MAC                                        | MorethanIP        |

| <b>-</b> 11.                   | FIR Filter Compiler                                                  | Altera            |

| Filtering                      | FIR Filter Compiler                                                  | Altera            |

| Modulation/                    | IFFT/FFT                                                             | Altera            |

| Demodulation                   | Numerical Control Oscillator                                         | Altera            |

|                                | Reed-Solomon Encoder/Decoder                                         | Altera            |

| Error detection and correction | Viterbi Low Speed Serial Compiler                                    | Altera            |

|                                | Viterbi High Speed Parallel Compiler                                 | Altera            |

|                                | AES cryptoprocessor                                                  | CAST, Inc         |

| Encryption/Decryption          | DES cryptoprocessor                                                  | CAST, Inc         |

|                                | Secure hash algorithm cryptoprocessor                                | CAST, Inc         |

| Network synchronization and    | Hybrid timing generator                                              | AimValley         |

| circuit emulation              | Circuit emulation with CESoPSN or SAToP                              | AimValley         |

# **Summary**

- Femto market is nascent

- Market uncertainty = risk

- ASIC is high risk

- Price expectation demands low-cost solutions

- HardCopy technology is a strong contender

- Low-risk, seamless migration from FPGA to low-cost structured ASIC

- Allows quick turnaround for multiple product variants

- Reduce risk and capture a place in the femtocell market

# Thank You!