**1** Overview of 3D-RAM and Its Functional Blocks

## **Overview of 3D-RAM and Its Functional Blocks**

## Introduction

One of the traditional bottlenecks of 3D graphics hardware has been the rate at which pixels can be rendered into a frame buffer using conventional DRAM or VRAM. The 3D-RAM emerged from a complete rethinking of frame buffer technology and produces an order of magnitude increase in rendering performance. The essence of the 3D-RAM architecture is: (1) an optimized array architecture that minimizes the average memory cycle time when rendering and (2) a selective on-chip logic that converts the interface with the rendering controller from a read-modified-write mode to a write-mostly mode. In addition to the performance boost, the new architecture also significantly reduces the system chip count. In 1994 Mitsubishi pioneered the introduction of the first member of the 3D-RAM family of products. This databook specifies all the features and operations of the third generation product of the 3D-RAM family to further elevate the performance of the 3D-RAM based 3D graphics systems. All references to 3D-RAM means the product M5M410092B, unless otherwise specifically designated.

The factors responsible for the dramatic overall performance improvement include:

- New Memory Architecture

- 10-Mbits DRAM array supporting 1280 x 1024 x 8 frame buffer

- Four independent, interleaved DRAM banks

- 2048-bit SRAM Pixel Buffer as the cache between DRAM and ALU

- Built-in tile-oriented memory addressing for rendering and scan line-oriented memory addressing for video refresh

- 256-bit global bus connecting DRAM banks and Pixel Buffer

- Flexible dual Video Buffer supporting 76-Hz CRT refresh

- Write Mostly Interface

- On-chip ALU

- Four ROP units supporting 16 raster operations on byte data

- Four Blend units blending the old pixel value with new information

- On-chip hardware acceleration for all OpenGL blending modes(*NEW*)

- On-chip hardware acceleration for all OpenGL stencil modes (<u>NEW</u>)

- One 32-bit Match Comparator and one 32-bit Magnitude Comparator

- Concurrent operations of DRAM, Pixel Buffer, ALU and Video Buffer

- 32-bit synchronous high-bandwidth data bus with rendering controller

- Blending operations in both (8, 8, 8, 8) and (4 4, 4, 4) color modes (<u>NEW</u>)

- One additional PASS\_IN pin for flexible

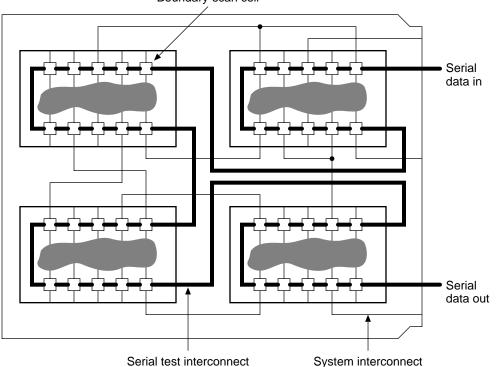

## Frame Buffer Design Example

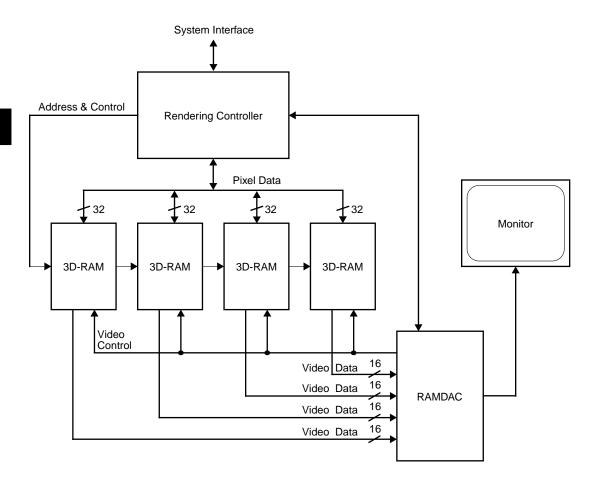

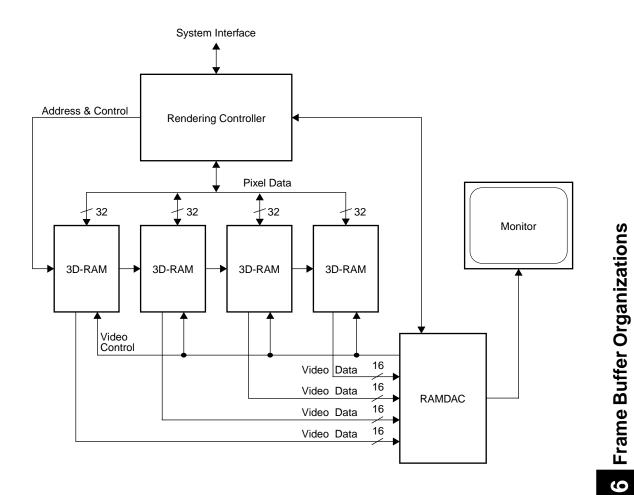

Figure 1.1 is a simple frame buffer design example showing a 1280 x 1024 x 32 single buffered configuration. The rendering controller writes pixel data across the 128-bit bus to the four 3D-RAMs. The controller commands most of the 3D-RAM operations, including ALU functions, Pixel Buffer addressing, and DRAM operations. The controller can also command video display by setting up the RAMDAC and requesting video transfers from 3D-RAMs.

With the 128-bit pixel data bus shown in Figure 1.1, four pixels can be moved across the bus in one cycle. There are two ways to organize the 3D-RAMs: (1) Each 3D-RAM holds one of the

8-bit color components—R, G, B, or a—for all 1280 x 1024 pixels; (2) Each 3D-RAM holds all 32 bits of a pixel value for 320 x 1024 pixels, allowing fast scrolling in the vertical direction and interleaving four 3D-RAMs in the horizontal direction.

If the width of the data bus from the rendering

controller to 3D-RAM is reduced to 64 bits, then two pixels are transferred in one cycle. Similarly, a 32-bit data bus can transfer only one pixel at a time.

Chapter 6 provides more examples of frame buffer organizations using 3D-RAMs, such as  $1280 \times 1024 \times 8$ ,  $320 \times 1024 \times 32$ , etc.

Figure 1.1 1280 x 1024 x 32 frame buffer consisting of four 3D-RAMs, shown together with a rendering controller and a RAMDAC

## Preliminary Rev. 0.95 3D-RAM (M5M410092B)

## Simplified 3D-RAM Block Diagram

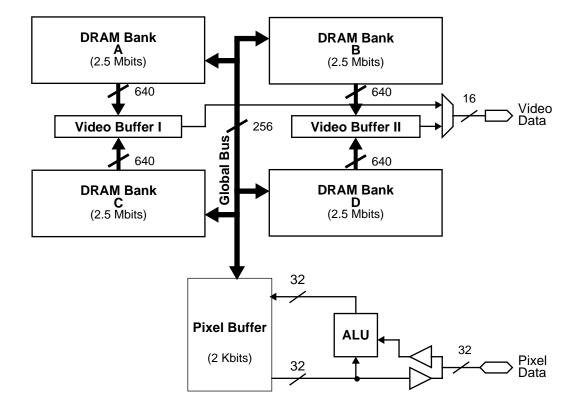

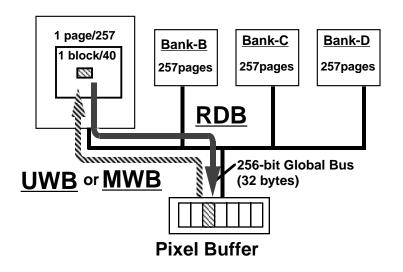

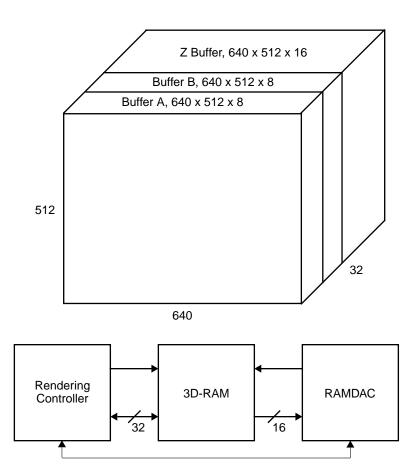

The 3D-RAM block diagram is shown in Figure 1.2. The DRAM array is partitioned into four independent banks of 2.5 Mbits each. Together, these four banks can support a screen resolution of  $1280 \times 1024 \times 8$ . The independent banks can be interleaved to facilitate almost uninterrupted frame buffer update and, at the same time, can transfer pixel data to the dual Video Buffer for screen refresh. Data from the DRAM banks is transferred over the 256-bit Global Bus to the triple-ported Pixel Buffer. The Pixel Buffer consists of eight blocks, each of which is 256 bits and is updated in a single transfer on the Global Bus. Hence, the memory size of the Pixel Buffer is 2 Kbits. The ALU uses two of the Pixel Buffer ports to read and write data in the same clock cycle. Each Video Buffer is 80 x 8 bits and is loaded in a single DRAM operation. One Video Buffer can be loaded while the other is sending out video data.

Figure 1.2 Simplified 3D-RAM block diagram

## **3D-RAM Functional Blocks**

The 3D-RAM has five major functional blocks in: DRAM banks, Video Buffers, Pixel Buffer, Global Bus, and Pixel ALU. The following sections provide a quick overview of each of these functional blocks. Chapter 3 describes details of the Pixel ALU operations, Chapter 4 presents specifics of the DRAM operations, and Chapter 5 provides examples of parallelism between the Pixel ALU operations and the DRAM operations. Now, to give readers a better grasp of these functional blocks, we first describe the memory units on which these functional blocks operate.

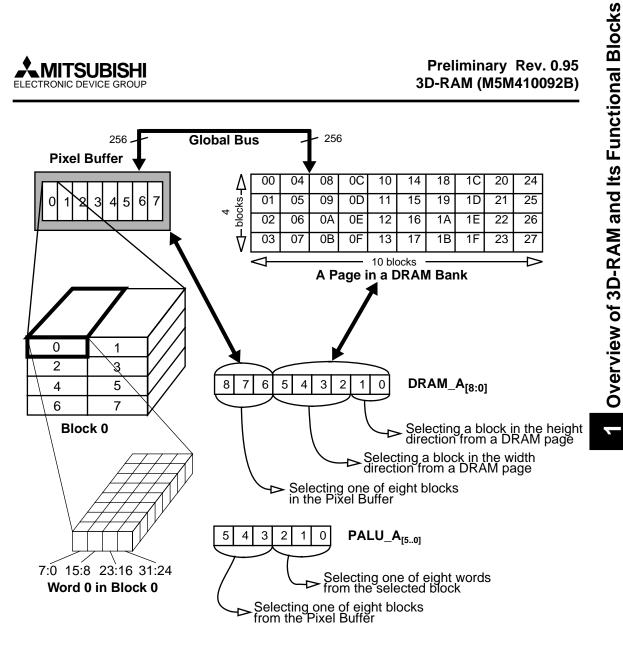

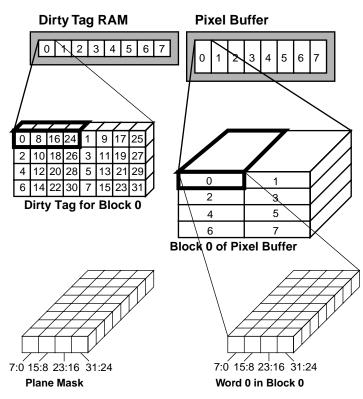

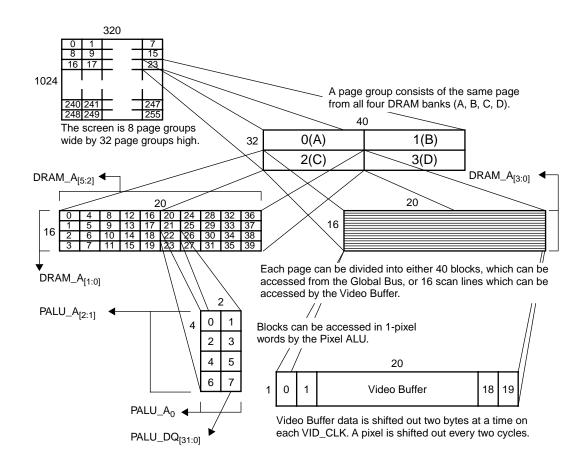

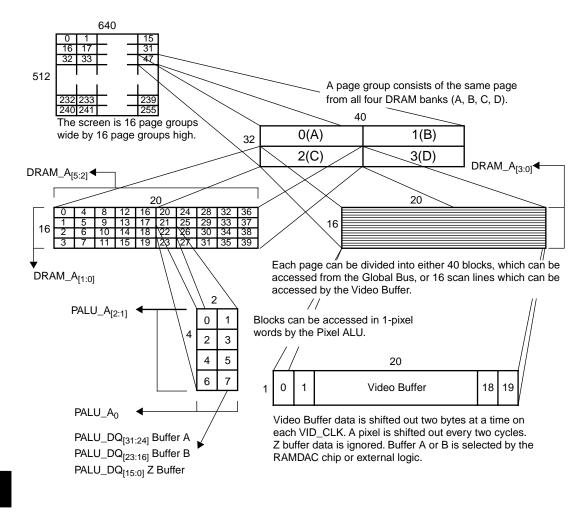

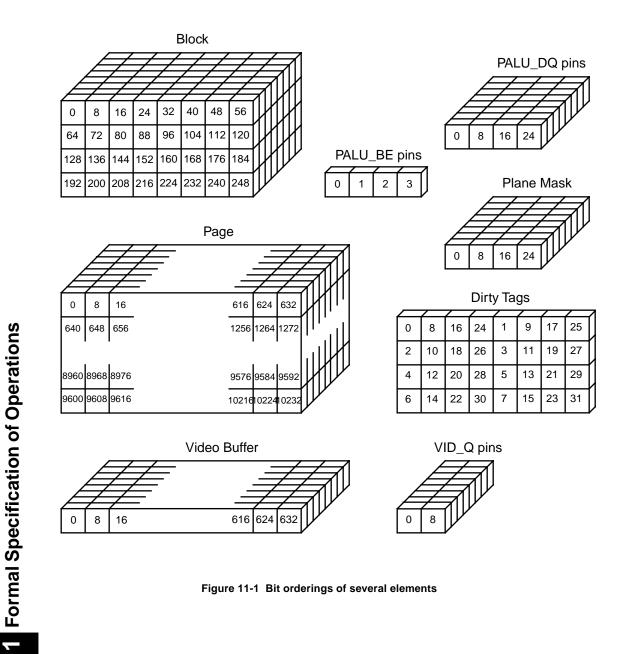

## Block, Page, and Page Group

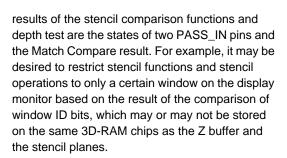

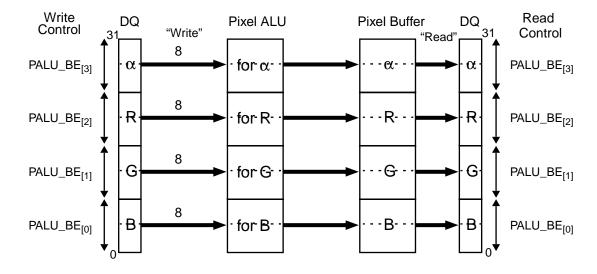

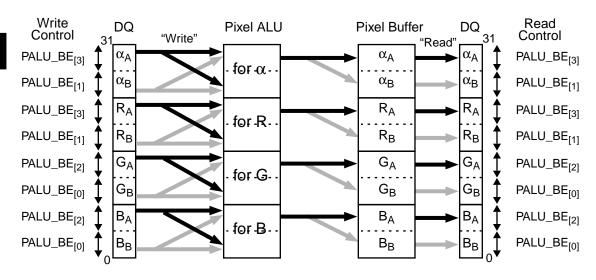

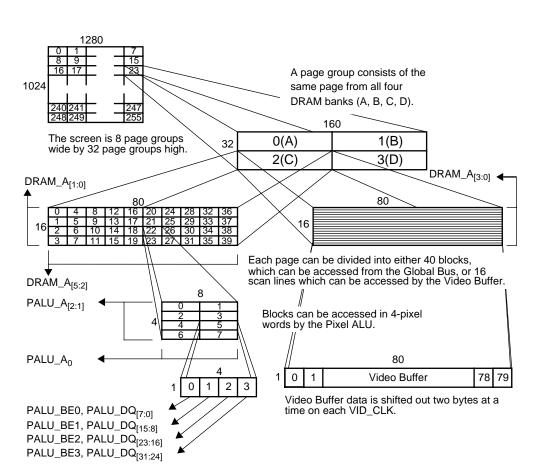

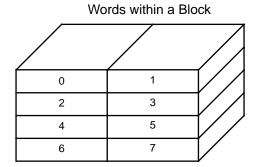

A word has 32 bits and is the unit of data operations within the Pixel ALU and between the Pixel ALU and Pixel Buffer. When the Pixel ALU accesses the Pixel Buffer, not only a block address needs to be specified but also a word has to be identified. Since there are eight blocks in the Pixel Buffer and eight words in a block, the upper three bits of the input pins PALU\_A designate the block, and the lower three bits select the word. The data in a word is directly mapped to PALU\_DQ<sub>[31:0]</sub> in corresponding order. That is, bit 0 of the word is mapped to PALU\_DQ0, bit 1 to PALU\_DQ1, and so on.

Although an ALU write operation operates on one word at a time, each of the four bytes in a word may be individually masked. The mapping is also direct and linear: byte 0 is PALU\_DQ<sub>[7:0]</sub>, byte 1 PALU\_DQ<sub>[15:8]</sub>, byte 2 PALU\_DQ<sub>[23:16]</sub>, and byte 3 PALU\_DQ<sub>[31:24]</sub>.

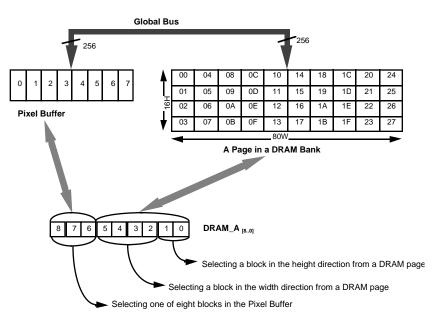

A block has 256 bits and is the unit of memory operations between a DRAM bank and the Pixel Buffer over the Global Bus. The input pins DRAM\_A selects a block from the Pixel Buffer and a block from a page of a DRAM bank. The DRAM operations on block data are Unmasked Write Block (UWB), Masked Write Block (MWB), and Read Block (RDB). These operations are described in detail on page 44, "Description of DRAM Operations."

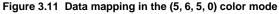

A page in a DRAM bank is organized into 10 x 4 blocks. Since a block has 256 bits, a page has 10,240 bits. There are four DRAM banks in a 3D-RAM chip, the pages of the same page address from all four DRAM banks compose a page group. Therefore, a page group has 20 x 8 blocks.

Note in Figure 1.3, the block and page are purposely drawn as rectangular shapes. The user may relate these to a tiled frame buffer memory organization. For example, if the display resolution is 1280 x 1024 x 8, then a (32-bit) word contains four pixels. Since a block may be viewed as having 2 x 4 words, it contains 8 x 4 pixels. A page is organized into 10 x 4 blocks, so it contains 80 x 16 pixels, and a page group holds 160 x 32 pixels. Finally, a screen is composed of 8 x 32 page groups. The advantage of such a frame buffer memory organization is the minimization of page miss penalty. 3D objects frequently occupy portions of multiple scan lines. Since in this case a page contains 80 x 16 pixels instead of 10,240 x 1 pixels, page miss is reduced. When an object extends beyond a page boundary, bank interleaving allows hidden precharge and uninterrupted memory access. Details of the various frame buffer memory organizations using 3D-RAMs are discussed in Chapter 6.

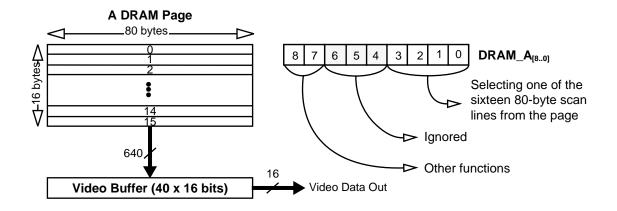

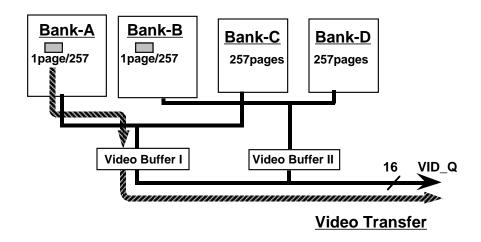

On the other hand, to support screen refresh, the Video Buffer must output pixel data one scan line at a time. The internal organization of a page also allows data to be transferred from a page to the Video Buffer, one of the sixteen scan lines of 80 bytes long each at a time. See the section "Video Buffers" on page 7 for a summary and the section "Video Transfer (VDX)" on page 46 for full details.

## Preliminary Rev. 0.95 3D-RAM (M5M410092B)

Figure 1.3 Relations and addressing scheme of blocks and words in the Pixel Buffer and in the **DRAM** page

7

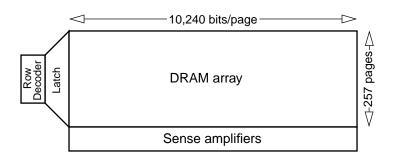

## DRAM Banks and Basic DRAM Operations

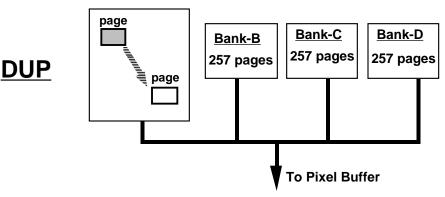

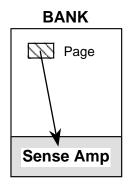

The 3D-RAM contains four independent DRAM banks which can be interleaved to facilitate hidden precharge or access in one bank while screen refresh is being performed in another bank. Each DRAM bank has 256 pages with 10,240 bits per page for a total storage of 2,621,440 bits. An additional 257th page can be accessed for special functions or used to hold off-screen data. A row decoder takes 9-bit page address signals to generate 257 word lines, one for each page. The word lines select which page is connected to the sense amplifiers. The sense amplifiers read and write the page selected by the row decoder. Because the sense amplifiers retain data after the read/write operations, they function like a directmapped level-two pixel cache. (The Pixel Buffer, which is discussed on page 7, functions as a level-one pixel cache in a frame buffer with 3D-RAMs.)

During an Access Page (ACP) operation, the row decoder selects a page by activating its word line. Activating the word line of a particular page transfers the bit charges of that page to the sense amplifiers. The sense amplifiers amplify the charges. After the sensing and amplification are completed, the sense amplifiers are ready to interface the Global Bus or Video Buffer. In a way,

ACP may be viewed as a "write cache" operation on the sense amplifiers as a level-two pixel cache. Because the activated word line remains connected to the sense amplifiers after the ACP operation until the subsequent Precharge Bank operation, when a block of the sense amplifiers is updated by a block write operation (UMB or MWB), the corresponding block in the DRAM array is also updated. Therefore, the sense amplifiers function as a "write-through" cache, and no write back to the DRAM array is necessary. Alternatively, the data in the sense amplifiers can be written to any page in the same bank at this time, simply by selecting a word line without first equalizing the sense amplifiers. This function is called Duplicate Page (DUP). A typical application of this function is copying from the 257th page to one of the 256 normal pages-all 10,240 bits at a time-for fast area fill.

When the sense amplifiers in a DRAM bank completes the read/write operations with the Global Bus or Video Buffer, a Precharge Bank (PRE) operation usually follows. A Precharge Bank cycle simply deactivates the selected word line corresponding to the current page and equalizes the sense amplifiers. The PRE operation may be viewed as the close of a page access or as the preparation for the subsequent page access. The DRAM bank must be precharged prior to accessing a new page.

Figure 1.4 DRAM bank consisting of row decoder, address latch, DRAM array, and sense amplifiers

## **Pixel Buffer**

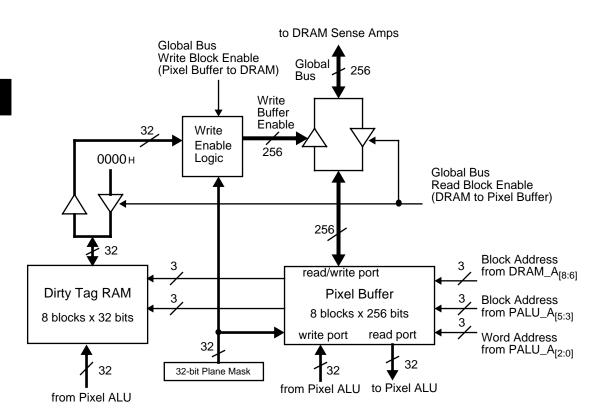

The Pixel Buffer is a 2048-bit SRAM organized into eight 256-bit blocks, as seen in Figure 1.3, and functions as a level-one write-back pixel cache. It has a 256-bit read/write port, a 32-bit read port, and a 32-bit write port. Referring to Figure 1.6, the 256-bit read/write port is connected to the Global Bus via a Write Buffer, and the two 32-bit ports are connected to the Pixel ALU and the pixel data pins. All three ports can be used simultaneously as long as the same memory cell is not accessed. If the two 32-bit ports access the same cell, the write operation will be successful but the read data will be undefined.

A 1-bit Dirty Tag bit is assigned to each byte data in the Pixel Buffer. Therefore, each block in the Pixel Buffer is associated with a 32-bit Dirty Tag in the dual-port Dirty Tag RAM. When a block is transferred from the sense amplifiers to the Pixel Buffer through the 256-bit port, the corresponding 32-bit Dirty Tag is cleared. When a block is transferred from the Pixel Buffer to a DRAM bank, the Dirty Tag determines which bytes are actually written. This feature can save as much as 50% of the power consumed by a 256-bit block write operation without the Dirty Tag.

The cache set associativity is determined external to the 3D-RAM, thereby permitting optimal cache design tailored to the particular graphics system.

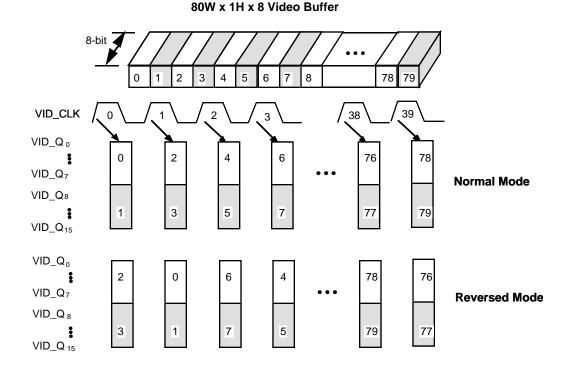

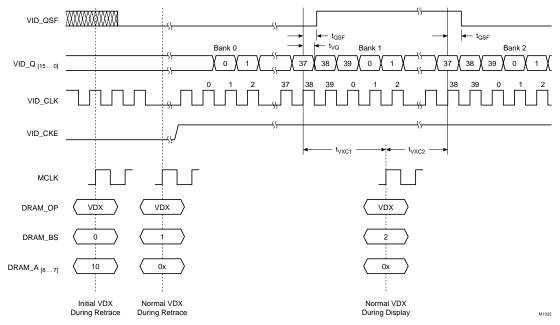

## Video Buffers

Each video buffer receives 640-bit data at a time from one of the two DRAM banks connected to it. (The reader is reminded of the 3D-RAM block diagram in Figure 1.2.) sixteen bits of data are shifted out onto the video data pins every video clock cycle at 14-ns rate. It takes 40 video clocks to shift all data out of a video buffer. The video counter counts modulo 40 and toggles the buffer select line when the count wraps around to 0. These two video buffers can be alternated to provide a seamless stream of video data.

Figure 1.5 Video transfer from a DRAM page to the Video Buffer

## Preliminary Rev. 0.95 3D-RAM (M5M410092B)

## **Global Bus**

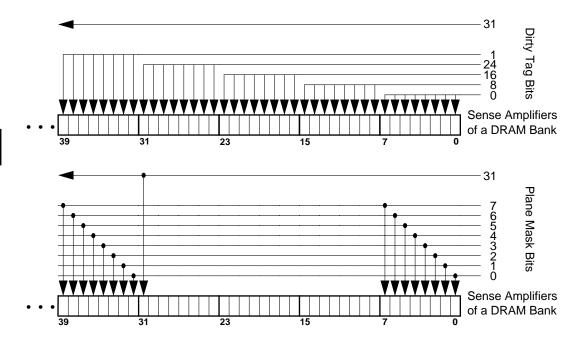

The Global Bus connects the Pixel Buffer to the sense amplifiers of all four DRAM banks. The Global Bus consists of 256 data lines. Referring to Figure 1.6, during a transfer from the Pixel Buffer to DRAM, the 256 bits are conditionally written depending on the 32-bit Dirty Tag and the 32-bit Plane Mask. When a data block is transferred from the Pixel Buffer to the sense amplifiers, the Dirty Tag and Plane Mask control which bits of the sense amplifiers are changed via the Write Buffer. Note that all read/write operations are viewed from the perspective of the rendering controller. In other words, a read operation across the Global Bus always means a read by the Pixel ALU; that is, data is transferred from a DRAM bank into the Pixel Buffer. Similarly, a write operation across the Global Bus means data is updated from the Pixel Buffer to a DRAM bank. This is also specifically noted in Figure 1.6 by the signals Global Bus Write Block Enable and Global Bus Read Block Enable.

Figure 1.6 Tri-port Pixel Buffer, Global Bus and dual-port Dirty Tag RAM

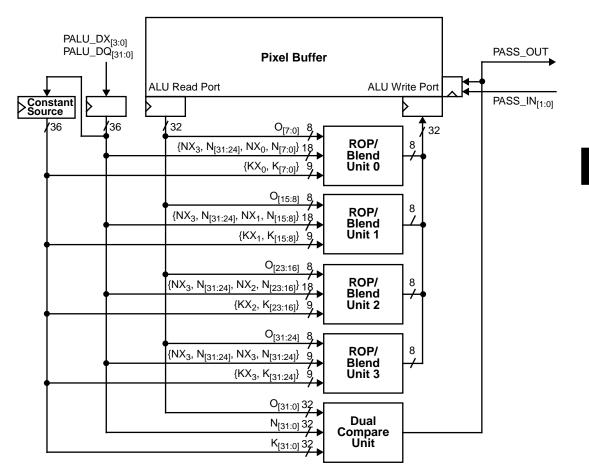

## **Pixel ALU Basics**

The Pixel ALU consists of four 8-bit ROP/Blend units, which may be independently programed to perform either a raster operation or a blending function, one 32-bit Match Compare unit, and one 32-bit Magnitude Compare unit. The two Compare units are also commonly referred to as the Dual Compare units. The motivation for including the Pixel ALU on chip is to convert the interface from a read-modify-write interface to a write-mostly interface. This logic integration with memory arrays greatly improves rendering throughput by avoiding time consuming reads and direction changes on the data bus.

## Preliminary Rev. 0.95 3D-RAM (M5M410092B)

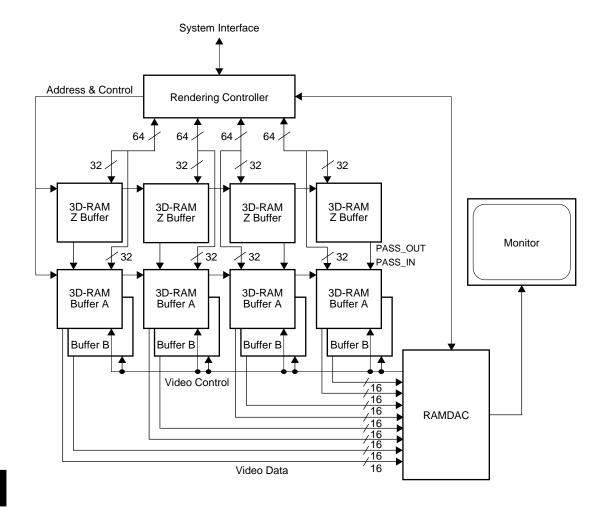

The ROP/Blend units and the Dual Compare units are highly pipelined. Page 11 contains a brief discussion of the ALU pipeline. The output of a ROP/Blend unit is conditionally written to the Pixel Buffer, depending on the comparison results from the on-chip Dual Compare units and from the Dual Compare units of the preceding 3D-RAM chips. For example, for a 1280 x 1024 x 32 doublebuffered graphics system with 32-bit Z buffer, there are effectively 96 bits per pixel. In this case, eight 3D-RAMs are used as color chips and four as Z chips. The Pixel ALUs of the Z chips perform magnitude comparisons and feed the comparison results via their PASS\_OUT pins to the

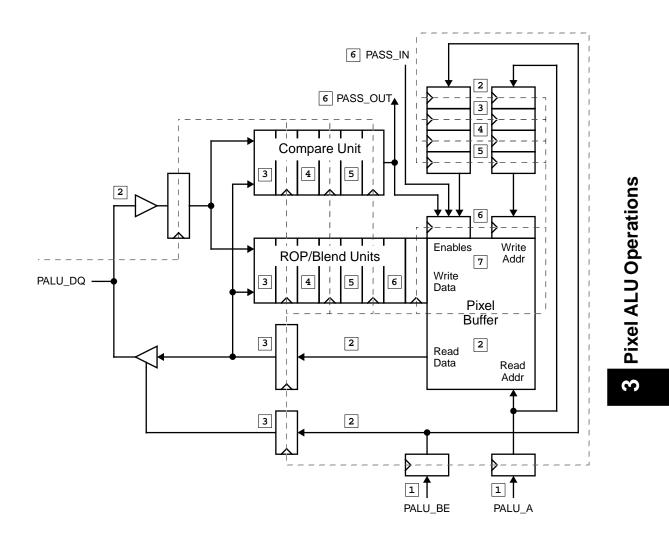

Figure 1.7 Pixel ALU (Pipeline stages are not shown.)

corresponding color chips. It is important to note that due to the pipelining, the color chips do not wait for the magnitude comparison results from the Z chips; rather, the results of the ROP/ blending operations and comparison operations on the color chips, and the results of the magnitude comparison on the Z chips all are presented to the Pixel Buffer of the color chips in the same clock cycle. In this sense, the rendering controller can accomplish a pixel blending operation with Z compare and window ID compare all in a single clock cycle. Furthermore, because of the pipelining and the tri-ported architecture of the Pixel Buffer, the read and write operations may be performed on the Pixel Buffer of the 3D-RAM during the same clock cycle.

#### **ROP/Blend Units**

The ROP/Blend units can be configured as either a ROP unit or a Blend unit by setting a register bit. Each ROP unit can perform all 16 standard ROP functions. These functions are listed in Chapter 3. One of the operands of the ROP functions is the old data from the Pixel Buffer, and the other operand may be either the data from the primary I/ O pins or the data from an internal register (called the Constant register). For the blending operation, the general equation is as follows:

Write data to Pixel Buffer

- = New Term + (Old Data x Old Fraction)

- (New Data x New Fraction) +

(Old Data x Old Fraction)

The 3D-RAM Blend units accomplish what is called destination blending in a single MCLK cycle, that is, the addition and the second multiplication in the above equation. In this case, the rendering controller must perform the multiplication of New Data with New Fraction (i.e., the source blending) and present the result as the New Term to 3D-RAM. In addition, 3D-RAM can also accomplish the full blending by taking two MCLK cycles, with a loop back mechanism.

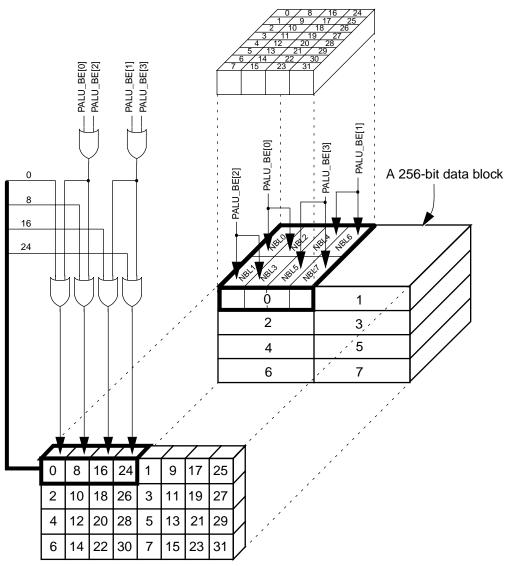

#### **Dual Compare Unit**

Physically, the Dual Compare units consist of one 32-bit Match Compare unit and one 32-bit Magnitude Compare unit. Both Match Compare and Magnitude Compare are done in parallel. One of the sources is always the old data from the Pixel Buffer. The other source is independently selectable between the data from the PALU\_DQ pins and the data from the Constant source register. There are also two mask registers, namely Match Mask and Magnitude Mask, that define which bits of the 32-bit words will be compared and which will be "don't care."

One application of the Match Compare unit is Window ID comparison, and the Magnitude Compare unit is typically used in the depth comparison of a Z-buffer algorithm for hidden surface removal. When these Compare units are used together, the system can achieve hidden surface removal for only a specific window on the display in one cycle. Furthermore, since the data to be written into the Pixel Buffer always comes through the ROP/Blend units, a system with 3D-RAM can achieve a pixel update with a raster or blending operation specifically on only the new objects in the selected window that are closer to the viewer than the existing objects in the frame buffer.

The results of both Match Compare and Magnitude Compare operations are logically ANDed together to generate the PASS\_OUT pin. The PASS\_IN signal (fed from another 3D-RAM chip) and the internally generated PASS\_OUT signal are then logically ANDed together to produce a Write Enable signal to the Pixel Buffer. Thus, the PASS\_IN and PASS\_OUT pins offer hardware support for display resolutions where multiple 3D-RAM chips are required, such as in the cases of 1280x 1024 x 32 (single color buffer plus Z buffer) and 1280 x 1024 x 96 (double color buffer plus Z buffer).

#### Pipelining

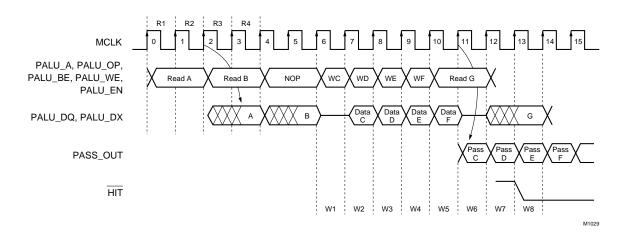

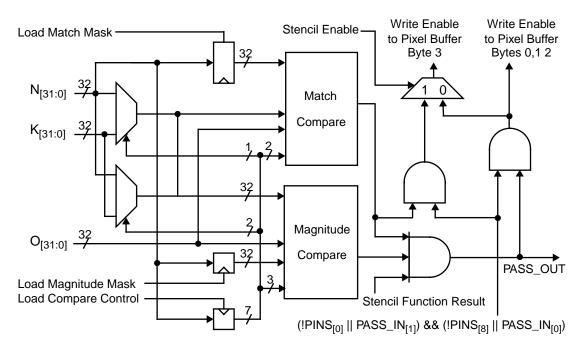

The 3D-RAM Pixel ALU pipeline is designed so that read and write operations can be performed with minimal delay. This is achieved by having all operations conform to a uniform 7-stage pipeline.

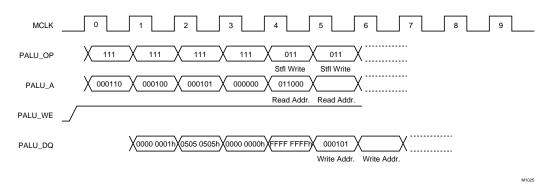

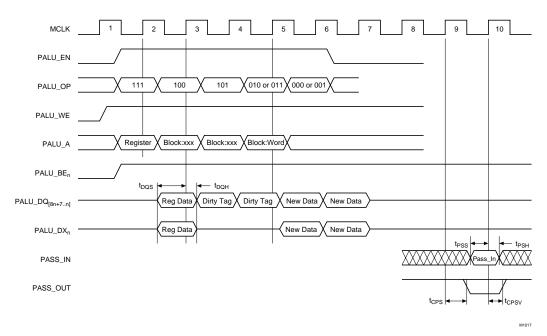

Figure 1.8 is an example that illustrates the efficiency afforded by the pipeline flow of Pixel ALU read/write operations. A pipeline stage begins with a rising edge of MCLK and ends before the next rising edge of MCLK. (As a matter, in the 3D-RAM all references to MCLK are relative to the rising edge except for some boundary scan test operations.) For clarity, separate stage counts are provided for the first read and first write operations and are labeled as R1 through R4 and W1 through W7, respectively. The Read A operation is asserted for two cycles; Read A is first presented in Stage R1 and latched into the 3D-RAM by Clock 1 in Stage R2. Data A is piped out by Clock 2 in Stage R3 and becomes stable for sampling in Stage R4. Between Read B and WC (Write C), two single-cycle NOPs are inserted

## Preliminary Rev. 0.95 3D-RAM (M5M410092B)

to guarantee an idle cycle for the data bus to turn around. On the other hand, a read operation can immediately follow a write operation, as shown by Read G following WF. To allow maximum bandwidth for the rendering controller, a write operation may be started everything cycle. In this example, we start with the WC operation. The address and write instruction are presented in Stage W1 and latched into the 3D-RAM by Clock 7 in Stage W2; Data C and WD are presented in Stage W2 and latched into the 3D-RAM by Clock 8 in Stage W3. Then, after three cycles for internal processing, the valid PASS\_OUT Pass C is piped out by Clock 11 in Stage W6. The actual updating of the Pixel Buffer takes place in Stage W7. Thus, n consecutive write operations take only 7 + n - 1 = n + 6 cycles to complete, including all internal activities. It is important to point out that the effective write cycle time from the perspective of the rendering controller interface is only n + 1 cycles for n consecutive write operations, as shown by WC through WF.

Figure 1.8 Example of Pixel Port read/write operations that satisfy the pipeline flow

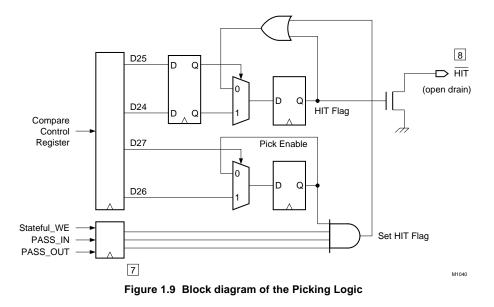

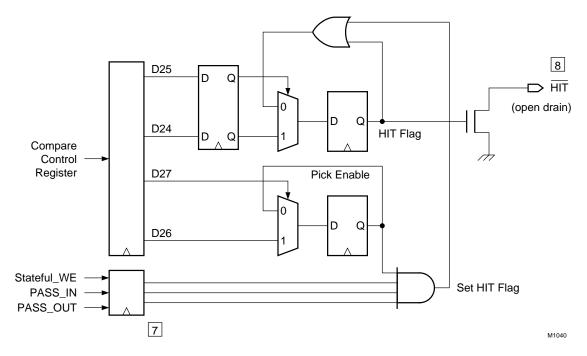

#### The Picking Logic

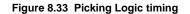

From the user's view point, a common experience of the picking function in 2D computer graphics may be using the mouse and the associated cursor to select an icon on the display screen, resulting in the selected icon highlighted in a different color. This is a basic function in interactive computer graphics, and 3D-RAM provides the Picking Logic and the HIT pin to support this picking function for selection of objects in a 3D scene.

A picking function may involve redrawing the objects into the frame buffer and returning a list of objects that intersect with some predefined selection volume. When the user uses multiple 3D-RAMs in a frame buffer design to determine if a pixel data is successfully written by any Stateful Write operation (see "Pixel Data Operations" on page 40) during the redraw process, the comparison result on the PASS\_OUT pin from each chip must be logically ANDed. If this logical operation is left to off-chip glue logic between the 3D-RAM frame buffer and the rendering controller, excessive delay is unavoidable in this critical timing path. If the rendering controller is to perform this logical operation, extra pins must be provided by both the 3D-RAM and the rendering

Preliminary Rev. 0.95 3D-RAM (M5M410092B)

controller, while delay is still significant. The Picking Logic brings the glue logic on chip and provides an open-drain HIT pin to interface with the rendering controller.

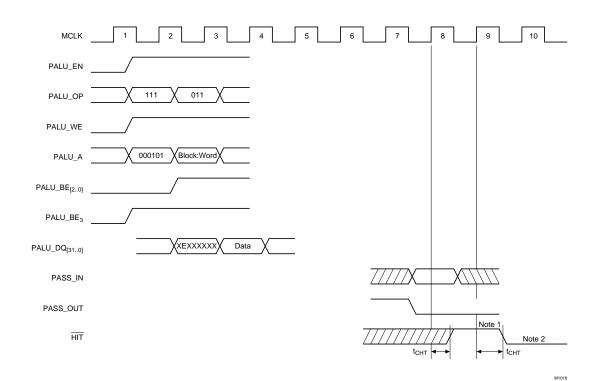

A block diagram of the Picking Logic is shown in Figure 1.9. Initially, the Picking Logic should be enabled and the HIT flag should be cleared, which is done by writing to byte 3 of the Compare Control Register. The HIT pin will be set to high (i.e., not driven low by 3D-RAM) after seven cycles (corresponding to the Pipeline Stage 8). In the figure below, this is indicated by the number 8 in the square box above the HIT pin label. This design of the pipeline flow for the HIT flag and the HIT pin prevents an incorrect HIT value from the Stateful Data Write operations before the Picking Logic is enabled. A sequence of Stateful Data Write operations may be issued immediately after the register writing. A low value on the HIT pin means that at least one of the Stateful Data Writes passed the on-chip and off-chip comparison tests and the pixel data was written to the Pixel Buffer. If the HIT pin is high, none of the Stateful Data Writes passed and no pixel is updated. See Figure 8.6, "Picking Logic Timing," for an illustration of the operations described in this section.

2 Pin Descriptions and Pinouts

## **Pin Descriptions and Pinouts**

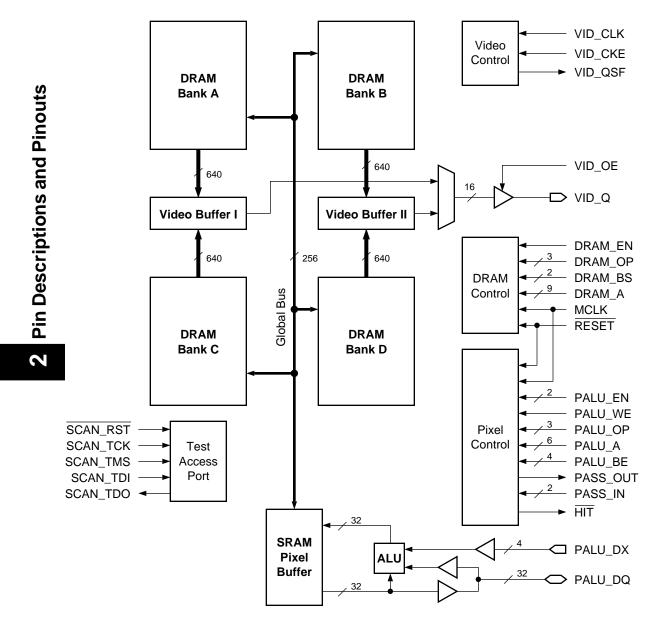

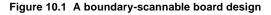

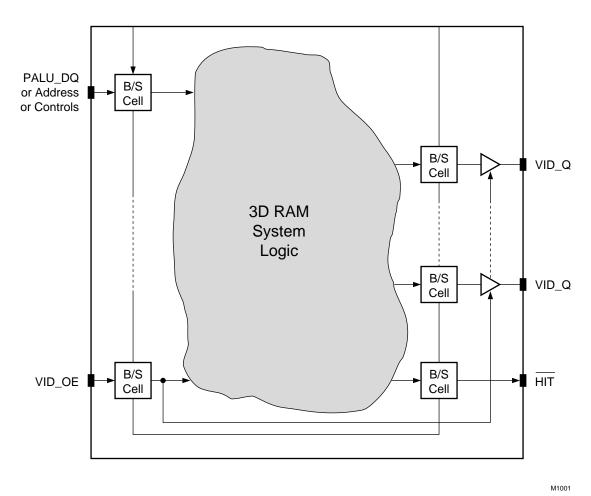

This chapter describes the 3D-RAM pins. Unless otherwise specified, all signals comply with the Low Voltage TTL (LVTTL) standard. The functional block diagram in Figure 2.1 shows all I/O signals on the external pins. The master clock MCLK synchronizes all operations of the Pixel ALU Control and DRAM Covntrol. The Video Control specifies the video interface. The Test Access Port is used for the JTAG (Joint Test Action Group) boundary scan. The following sections describe each signal in detail.

## **Common Pins**

These signals are common to several sections of the 3D-RAM.

| Signal<br>Name | Pin<br>Count | I/O | Description  |

|----------------|--------------|-----|--------------|

| MCLK           | 1            | I   | Master clock |

| RESET          | 1            | I   | Reset        |

| Total          | 2            |     |              |

| Table 2.1 | Common | control | signals |

|-----------|--------|---------|---------|

|-----------|--------|---------|---------|

#### MCLK

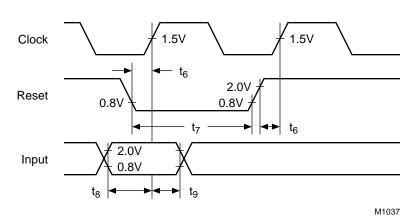

The master clock MCLK is used for timing synchronization of internal circuitry. All external timing parameters, except video output operation and boundary scan, are specified with respect to the MCLK rising edge.

#### RESET

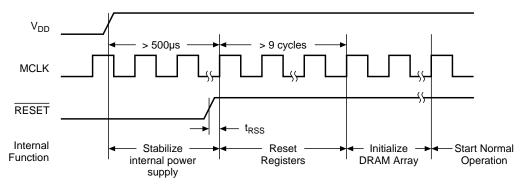

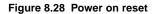

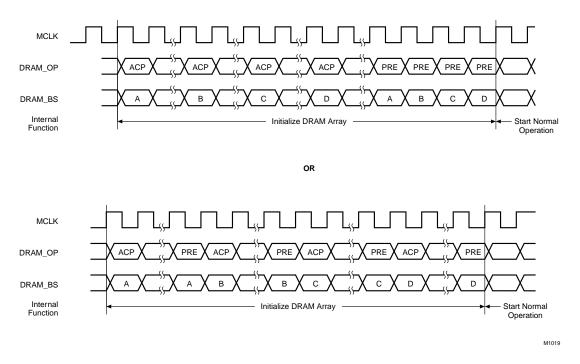

The RESET is an active low asynchronous signal used for power up and restart initialization. During power-up, the RESET signal should be held low for at least 500us after stable VDD, so that the internal power supply can be stabilized. After the RESET signal goes high, nine idle cycles must elapse before the internal registers can be reset to default values. The power-up reset procedure is illustrated in Figure 8.1. When the RESET signal is asserted low during normal operations, a restart reset sequence begins. The restart reset includes resetting registers in nine idle cycles and initializing DRAM array as in the power-up reset. The restart reset sequence is shown in Figure 8.3. In DRAM array initialization, the Access Page (ACP) operation should be performed on one page for every DRAM bank, followed by the Precharge Bank (PRE) operation for every bank. Figure 8.3 shows two approaches to initializing the DRAM array.

M1028

Figure 2.1 3D-RAM functional block diagram with external pins

**Pin Descriptions and Pinouts**

2

## Pixel ALU Interface

These signals control the Pixel ALU and Pixel Buffer.

| Table 2.2 | Pixel ALU | control | signals |

|-----------|-----------|---------|---------|

|-----------|-----------|---------|---------|

| Signal Name | Pin Count | I/O | Description                                           |

|-------------|-----------|-----|-------------------------------------------------------|

| PALU_EN     | 2         | I   | Enable Pixel ALU operation starting next cycle        |

| PALU_WE     | 1         | I   | Pixel ALU write enable                                |

| PALU_OP     | 3         | I   | Pixel ALU opcode                                      |

| PALU_A      | 6         | I   | Read/Write address                                    |

| PALU_BE     | 4         | I   | Byte write or output enable                           |

| PALU_DQ     | 32        | I/O | Data pins                                             |

| PALU_DX     | 4         | I   | Data extension pins for blending                      |

| PASS_OUT    | 1         | 0   | Compare output (special signal level, see Table 7.2)  |

| PASS_IN     | 2         | I   | Compare input (special signal level, see Table 7.2)   |

| HIT         | 1         | 0   | Picking Logic flag output (open-drain, see Table 7.2) |

| Total       | 55        |     |                                                       |

## PALU\_EN<sub>[1:0]</sub>

The PALU\_EN<sub>[1:0]</sub> pins must be "11" to start a Pixel ALU operation. If either PALU\_EN pin is "0", then all other Pixel ALU pins are ignored.

#### PALU\_WE

The PALU\_WE indicates a write operation when high ("1") and a read operation when low ("0").

### **PALU\_OP**<sub>[2:0]</sub>

The PALU\_OP<sub>[2:0]</sub> pins, together with PALU\_WE, specify the operation to be performed. See Table 3.4 for the Pixel ALU operation encoding.

#### PALU\_A<sub>[5:0]</sub>

The PALU\_ $A_{[5:0]}$  pins provide an address for the specified operation.

### PALU\_BE<sub>[3:0]</sub>

The PALU\_BE<sub>[3:0]</sub> pins apply to all read and write operations, including register writes and Dirty Tag writes. If PALU\_WE is low "0", indicating a read, the PALU\_BE pins are per byte output enables. If PALU\_WE is high "1", indicating a write, the PALU\_BE pins are per byte write enables. PALU\_BE0 controls PALU\_DQ<sub>[7:0]</sub>; PALU\_BE1 controls PALU\_DQ<sub>[15:8]</sub>; PALU\_BE2 controls PALU\_DQ<sub>[23:16</sub>]; and PALU\_BE3 controls PALU\_DQ<sub>[31:24]</sub>.

## **PALU\_DQ**<sub>[31:0]</sub>

Data is read from or written to the PALU\_DQ[31:0] pins. The write address of Pixel Buffer may be input from PALU\_DQ<sub>[29:24]</sub> in some modes of operation. See " An Application of the Write Address Control Register" on page 38.

##

## PALU\_DX<sub>[3:0]</sub>

Extra high-order bits of PALU\_DQ data are provided by PALU\_DX<sub>[3:0]</sub>. PALU\_DX0 is associated with PALU\_DQ[<sub>7:0]</sub>; PALU\_DX1 is associated with PALU\_DQ<sub>[15:8]</sub>; PALU\_DX2 is for PALU\_DQ<sub>[23:16]</sub>; and PALU\_DX3 is for PALU\_DQ<sub>[31:24]</sub>.

## PASS\_OUT

The comparison result of the Dual Compare unit is output on the PASS\_OUT pin. PASS\_OUT is low ("0") only when the Pixel ALU operation during the fifth stage of Pixel ALU pipeline is a Stateful Initial/Normal Data Write operation (see "Pixel Data Operations" on page 40) and when either match comparison or magnitude comparison fails. Otherwise, PASS\_OUT is high ("1"), indicating either the Pixel ALU operation is not a Stateful Initial/Normal Data Write or both comparison tests passed during the Stateful Initial/Normal Data Write.

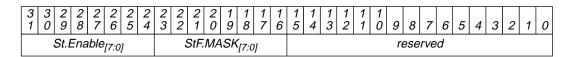

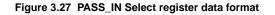

## $\textbf{PASS\_IN}_{[1:0]}$

When the PASS\_IN<sub>[1:0]</sub> pins are high ("11") and the internal comparison test also passes (PASS\_OUT is high ("1")), data is written to the Pixel Buffer if the Pixel ALU operation is a Stateful Normal/Initial Data Write. Each of the PASS\_IN[1:0] pins may be individually masked by the PASS\_INs Select register bits 0 and 8, PINS[0, 8], respectively.

#### HIT

The HIT pin is an open-drain, active low output. This pin reflects the internal status of the HIT flag. See "Compare Control Register (CCR  $_{[31:0]}$ )" on page 36 for a detailed description.

## **DRAM Control**

These signals command operations on the four DRAM banks, Global Bus and Video Buffer.

| Table | 2.3 | DRAM | control | signals |

|-------|-----|------|---------|---------|

|-------|-----|------|---------|---------|

| Signal<br>Name | Pin<br>Count | I/O | Description                                   |

|----------------|--------------|-----|-----------------------------------------------|

| DRAM_EN        | 1            | I   | Enable DRAM<br>operation at<br>next cycle     |

| DRAM_OP        | 3            | I   | DRAM opcode                                   |

| DRAM_BS        | 2            | I   | DRAM bank<br>select                           |

| DRAM_A         | 9            | 1   | Address for<br>page, block,<br>and video line |

| Total          | 15           |     |                                               |

#### DRAM\_EN

When DRAM\_EN is high ("1") at the rising edge of MCLK, a DRAM operation is initiated at the next clock cycle. Only the selected DRAM bank is enabled.

## **DRAM\_OP**<sub>[2:0]</sub>

The DRAM Opcode DRAM\_OP<sub>[2:0]</sub> specifies the DRAM operation. See Table 4.1 for the DRAM operation encoding.

## DRAM\_BS<sub>[1:0]</sub>

DRAM\_BS<sub>[1:0]</sub> is used to select one out of four banks. The selection codes are: "00" for Bank A, "01" for Bank B, "10" for Bank C, and "11" for Bank D.

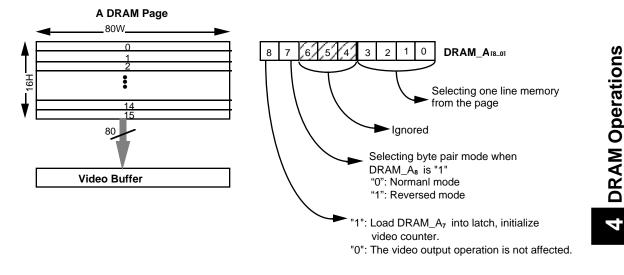

DRAM\_A<sub>[8:0]</sub>

The address pins DRAM\_A<sub>[8:0]</sub> are used to select one of the following: (i) a page in a DRAM bank, (ii) a block of data to be transferred between the sense amplifiers of a DRAM bank and the Pixel Buffer over the Global Bus, or (iii) 80 bytes of video data from the sense amplifiers of a DRAM page to a Video Buffer. Details are described in Chapter 4, "DRAM Operations."

#### Video Interface

These signals interface with a video RAMDAC chip.

| Signal<br>Name | Pin<br>Count | I/O | Description               |

|----------------|--------------|-----|---------------------------|

| VID_CLK        | 1            | I   | Video clock               |

| VID_CKE        | 1            | I   | Video clock<br>enable     |

| VID_OE         | 1            | I   | Video output<br>enable    |

| VID_Q          | 16           | 0   | Video data bus            |

| VID_QSF        | 1            | 0   | Video buffer<br>indicator |

| Total          | 20           |     |                           |

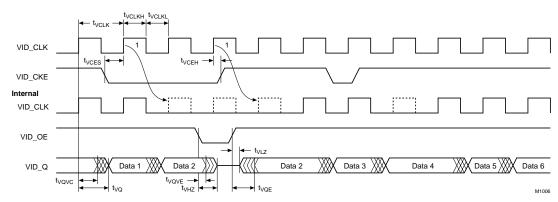

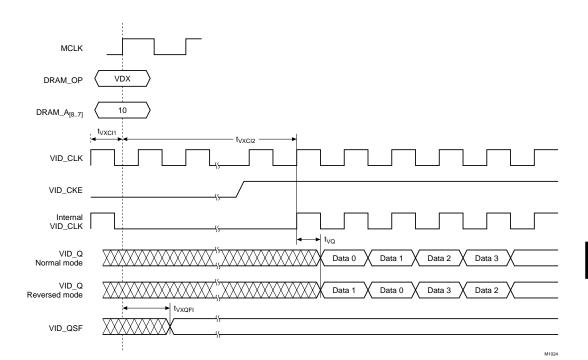

#### VID\_CLK

VID\_CLK is a free running or gated video shift clock.

#### VID\_CKE

VID\_CKE is a synchronous VID\_CLK enable signal. When VID\_CKE is high ("1"), the next VID\_CLK cycle will be enabled. The video counter will also be enabled in the next cycle.

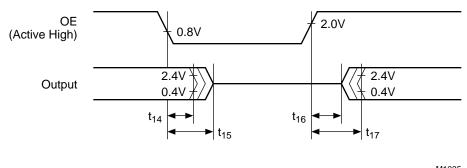

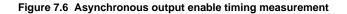

#### VID\_OE

VID\_OE is an asynchronous video output enable for VID\_Q. The video data bus is enabled when VID\_OE is high ("1").

## VID\_Q<sub>[15:0]</sub>

With 16-bit video data bus VID\_Q<sub>[15:0]</sub>, two bytes of data can be clocked out on the same cycle. In the 8-bit Video Buffer, the output format is arranged as even bytes on VID\_Q<sub>[7:0]</sub> and odd bytes on VID\_Q<sub>[15:8]</sub>. A detailed description of the two output data formats, normal mode and reversed mode, is in "Video Output Operation" on page 48.

Preliminary Rev. 0.95

3D-RAM (M5M410092B)

## VID\_QSF

The VID\_QSF output indicates which video buffer is currently providing video data. VID\_QSF is low ("0") when Video Buffer I is shifting data out. VID\_QSF is high ("1") when Video Buffer II is shifting data out.

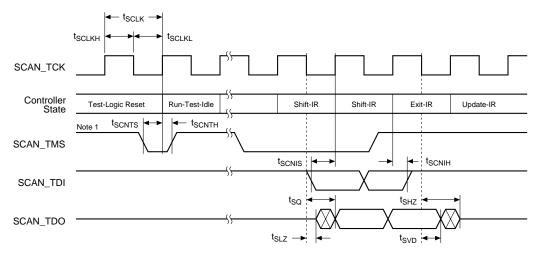

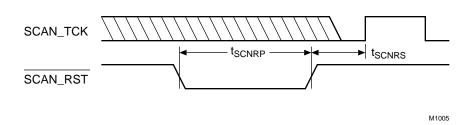

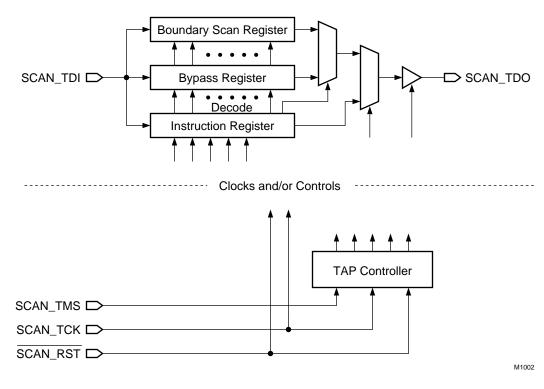

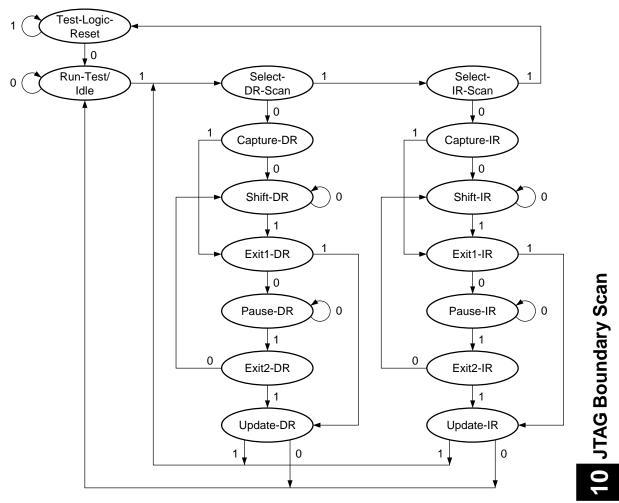

## **Test Access Port**

These signals interface to the Test Access Port for partial compliance with the IEEE Standard 1149.1 Test Access Port and Boundary Scan—Scan Architecture. The three input pins SCAN\_RST, SCAN\_TMS, and SCAN\_TDI should be pulled up to VDD with a 5K resistor. See Chapter 10, "JTAG Boundary Scan," for more details.

| Table 2 | .5 Seria | l test | signals |

|---------|----------|--------|---------|

|---------|----------|--------|---------|

| Signal<br>Name | Pin<br>Count | I/O | Description              |

|----------------|--------------|-----|--------------------------|

| SCAN_RST       | 1            | I   | Scan reset               |

| SCAN_TCK       | 1            | I   | Scan clock               |

| SCAN_TMS       | 1            | I   | Scan test<br>mode select |

| SCAN_TDI       | 1            | I   | Scan test<br>data input  |

| SCAN_TDO       | 1            | 0   | Scan test<br>data output |

| Total          | 5            |     |                          |

## **Power & Ground**

There are 13 Power Supply pins and 17 Ground pins. The NC pin should not be connected.

Table 2.6 Power and Ground

| Signal Name | Pin Count | Description   |

|-------------|-----------|---------------|

| Vss         | 17        | Ground        |

| Vdd         | 13        | Power supply  |

| NC          | 1         | No connection |

| Total       | 31        |               |

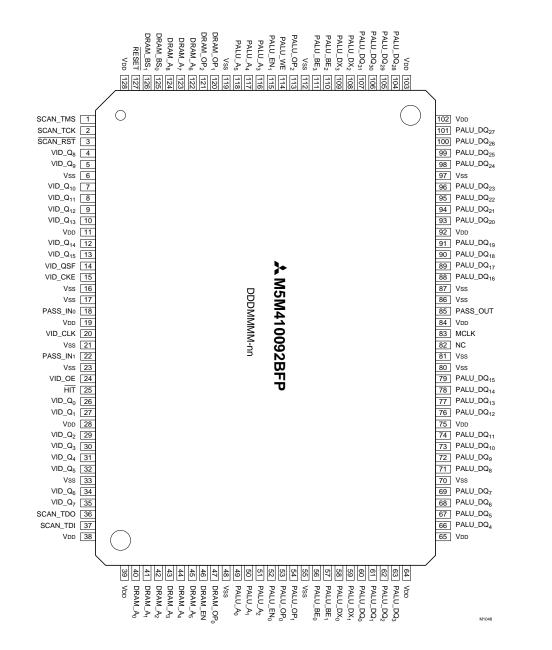

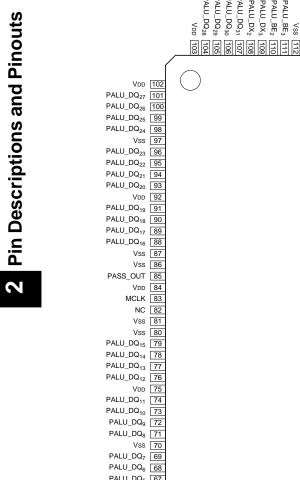

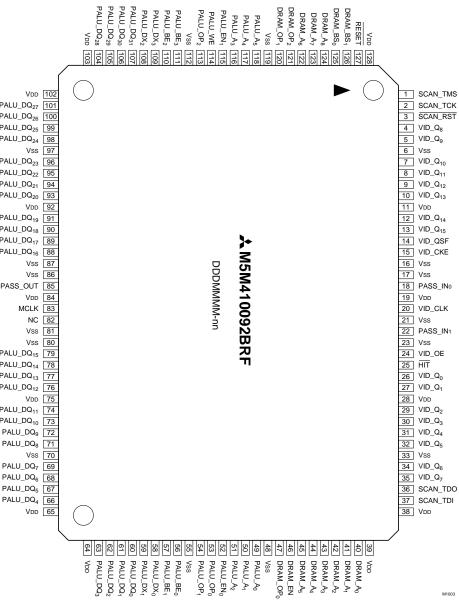

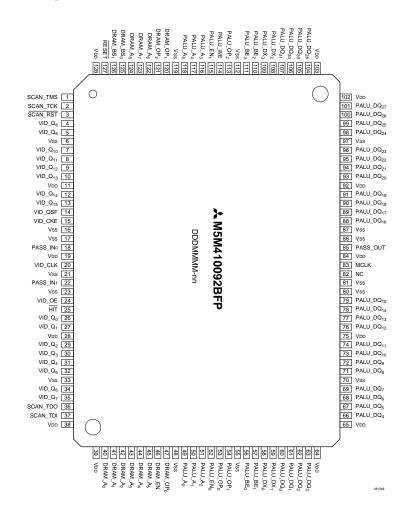

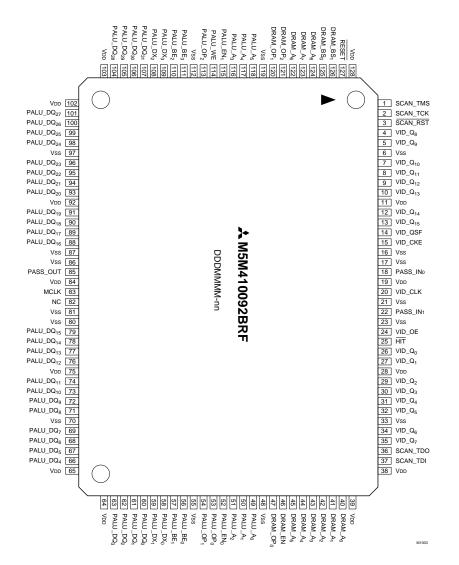

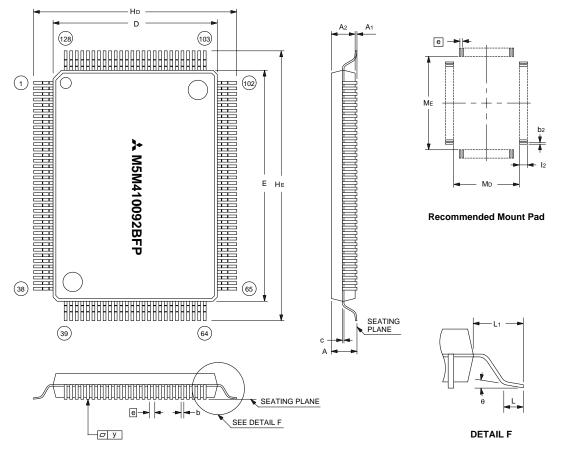

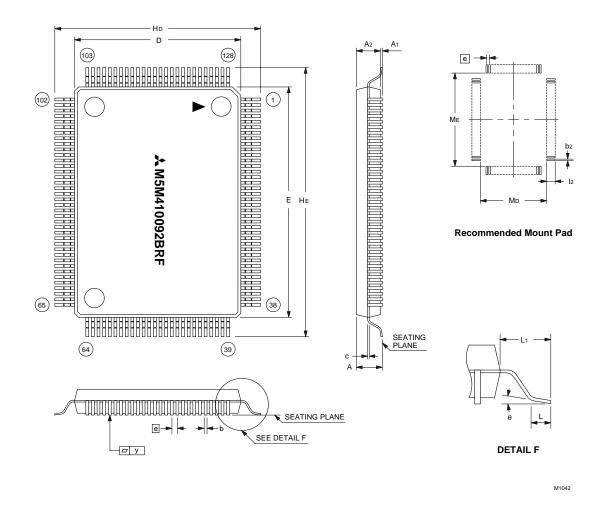

### **3D-RAM Pinouts**

There are two pinouts for 3D-RAM: normal pinout with pin 1 located at the lower left hand corner and specially marked by a small circle; and reverse pinout with pin 1 located at the upper left hand corner and marked by a large circle and a pointing triangle. The device in normal pinout is designated by the letters "FP" in the product number, and the device in reverse pinout by the letters "RF." In both pinouts, the mapping of pin number with pin name is identical.

#### Tracking Label

On the top surface of the 3D-RAM package, a tracking label is printed below the Mitsubishi logo and the 3D-RAM product number. The tracking label consists of 7 numbers followed by a dash and a speed/power grade designation and is represented by the mnemonic "DDDMMMM-nn". This mnemonic is explained below.

DDD: Data code

- MMMM: Manufacturing code

- nn: One of the following speed/power grade designations:

- "10"  $t_{CKL}$  (min) = 10 ns "13" —  $t_{CKL}$  (min) = 13 ns

## **Normal Pinout Diagram**

## **Reverse Pinout Diagram**

24

# Pixel ALU Operations

## **Pixel ALU Operations**

This chapter discusses details on the elements and operations of the Pixel Buffer and Pixel ALU in 3D-RAM. An operation that involves only the Pixel ALU and the Pixel Buffer is called a Pixel ALU operation. An operation that involves a DRAM array is categorized as a DRAM operation and is described in Chapter 4, "DRAM Operations." All registers of the 3D-RAM are defined and explained in this chapter.

### **Elements of the Pixel Buffer**

#### **Block and Word**

As stated in Chapter 2, the 2,048-bit Pixel Buffer is organized into eight 256-bit blocks. During a DRAM operation, these blocks can be addressed from the DRAM\_A pins for block transfers on the Global Bus. During a Pixel ALU operation, the 32-bit Pixel ALU accesses the Pixel Buffer, requiring not only the block address be specified but also the 32-bit word be identified. This is done via the 6-bit PALU\_A pins. The upper three bits select one of eight blocks in the Pixel Buffer, and the lower three bits specifies one of the eight words in the selected block. The availability of both the DRAM\_A and PALU\_A pins allows concurrent DRAM and Pixel ALU operations. Since a word is mapped directly to PALU\_DQ<sub>[31:0]</sub>, PALU\_DQ<sub>[7:0]</sub> is byte 0, PALU\_DQ<sub>[15:8]</sub> is byte 1, PALU\_DQ<sub>[23:16]</sub> is byte 2, and PALU\_DQ<sub>[31:24]</sub> is byte 3. Figure 3.1 is a simplified block diagram of these Pixel Buffer elements.

Figure 3.1 Pixel Buffer elements

#### **Dirty Tag**

Each data byte of a 256-bit block is associated with a Dirty Tag bit. This means that each <sup>\*</sup>-byte word is associated with four Dirty Tag bits and that a 32-bit Dirty Tag memory controls the corresponding 32-byte block data. The Dirty Tag RAM in the Pixel Buffer contains eight such 32-bit Dirty Tags. There are three aspects of Dirty Tag operations: tag clear, tag set, and tag initialization. In normal operation modes, the clearing and setting of the Dirty Tag by these read and write operations are done by the on-chip logic in the 3D-RAM and are essentially transparent to the rendering controller. The Dirty Tag bits are used by the 3D-RAM internally and are not output to the external pins.

When data is transferred from the sense amplifiers of a DRAM bank to a Pixel Buffer block over the Global Bus (i.e., a Read Block transfer which is a DRAM operation and is described in the next chapter), all 32 Dirty Tag bits associated with the selected Pixel Buffer block are cleared to "0". When data is transferred from a Pixel Buffer block to the sense amplifiers of a DRAM bank (i.e., a Write Block transfer, another DRAM operation), the Dirty Tag determines which data bytes can be written into the sense amplifiers. When a Dirty Tag bit is "1", the corresponding data byte is written under the control of the Plane Mask register (see the following section). When a Dirty Tag bit is "0", the corresponding byte of data in the DRAM bank is not written and retains its former value. Because the Dirty Tag prevents the unaltered bytes of a 256-bit block from being written into a DRAM bank, the power consumption of a Write Block transfer may be reduced by as much as 50%. This may be a significant power saving when a high-resolution display is constantly redrawn, such as in the case of high-quality fullscreen animation.

When a data word is read from the 32-bit ALU port of Pixel Buffer, none of the 32-bit Dirty Tags is affected or has any effect on the out-going data. The setting and initialization of the Dirty Tags are described in the paragraphs below.

| Table 3.1 Pixel A | U operations involving Dirty Tags |

|-------------------|-----------------------------------|

|-------------------|-----------------------------------|

| Pixel Operation                               | Pixel Data                                                 | New Dirty Tag Contents                                                                                                            |

|-----------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| (Stateful/<br>Stateless)Normal<br>Data Write  | Write bytes 0 to 3 from PALU_DQ<br>pins (per PALU_BE pins) | The four addressed Dirty Tag bits are ORed with PALU_BE <sub>[3:0]</sub> ; the other 28 Dirty Tag bits are unchanged.             |

| (Stateful/<br>Stateless)Initial<br>Data Write | Write bytes 0 to 3 from PALU_DQ pins (per PALU_BE pins)    | PALU_BE <sub>[3:0]</sub> is written to the 4<br>addressed Dirty Tag bits; "0" is written to<br>the 28 unaddressed Dirty Tag bits. |

| Replace Dirty Tag                             | Unchanged                                                  | PALU_DQ <sub>[31:0]</sub> replaces 32 Dirty Tag bits.                                                                             |

| OR Dirty Tag                                  | Unchanged                                                  | All 32 Dirty Tag bits are ORed with PALU_DQ <sub>[31:0]</sub> .                                                                   |

The Dirty Tag bits play an important role for all four write operations of the Pixel ALU to the Pixel Buffer: Stateful/Stateless Initial Data Write and Stateful/Stateless Normal Data Write. (These operations are also explained in "Pixel ALU Operations" on page 57.) Since the Pixel ALU operations conform to the 7-stage pipeline, the byte enable  $PALU_BE_{[3:0]}$  data also gets into the pipeline when the operation is issued. At the end of the pipeline, pixel data is written into a Pixel Buffer word and PALU\_BE<sub>[3:0]</sub> pins can change the four corresponding Dirty Tag bits. In the Initial Data Write operation, the four addressed Dirty Tag bits are replaced with PALU\_BE[3:0], while the other 28 Dirty Tag bits for the same block are cleared to "0". In the Normal Data Write operation, each of the four addressed Dirty Tag bits is set to "1" only when the corresponding PALU\_BE pin is "1". An addressed Dirty Tag bit is unchanged if the corresponding PALU\_BE pin is "0". The other 28 Dirty Tag bits for the same block are also unchanged.

The 32 Dirty Tag bits for a particular block can all be replaced with the PALU\_DQ data through the Pixel ALU operation "Replace Dirty Tag." Another Pixel ALU operation "OR Dirty Tag" changes the Dirty Tag contents for an addressed block with the result of the bitwise "OR" function on the original Dirty Tag data and the PALU\_DQ<sub>[31:0]</sub> data. The bit mapping between the Dirty Tag and PALU\_DQ pins is illustrated in Figure 3.1. For example, to change the Dirty Tag bits for word 0, the data should be placed on PALU\_DQ0, PALU\_DQ8, PALU\_DQ16, and PALU\_DQ24. To change the Dirty Tag bits for word 5, the data should be on PALU\_DQ5, PALU\_DQ13, PALU\_DQ21, and PALU\_DQ29. The following sub-section provides an application of these "Replace Dirty Tag" and "OR Dirty Tag" operations.

#### Using Dirty Tag for Color Expansion

Many 2D rendering operations, such as text drawing, involve writing the same color to many pixels. These operations can be greatly accelerated by specifying individual pixels with a single bit and having hardware automatically expand each bit to an entire pixel.

In 3D-RAM Color Expansion is done with the Dirty Tags associated with the Pixel Buffer blocks. The pixel color is written eight times to a Pixel Buffer block so that all of the pixels in the block are the same color. Next, a 32-bit word is written to the Dirty Tag of the associated block. Finally, the block is written to a DRAM bank. The pixel whose corresponding Dirty Tag bit is set is changed to the new color. The other pixels are unaffected.

A new 32-bit word may be written to the Dirty Tag afterwards, and the same Pixel Buffer block may be written to a different part of the DRAM array. Thus, one Pixel Buffer block can be used to hold the foreground color and used repeatedly to write text to the frame buffer.

#### Plane Mask

The 32-bit Plane Mask register (PM[31:0]) is used to qualify two write functions: (1) as per-bit write enables on 32-bit data for a Stateful (Initial/ Normal) Data Write operation from the Pixel ALU to the Pixel Buffer; (2) as per-bit write enables on 256-bit data for a Masked Write Block (MWB) operation from the Pixel Buffer to the sense amplifiers of a DRAM bank over the Global Bus. For a Stateful Data Write, the Plane Mask serves as per-bit write enables over the entering data from the Pixel ALU write port; bit 0 of the Plane Mask enables or disables bit 0 of the incoming 32-bit pixel data, bit 1 of the Plane Mask enables or disables bit 1 of the incoming 32-bit pixel data, and so on. For a Masked Write Block operation on the Global Bus side, when a Pixel Buffer block is transferred out to the DRAM, the 32-bit Plane Mask applies to every 32-bit word as per-bit write enables. In other words, bit 0 of the Plane Mask enables or disables bits 0, 32, 64, 96, 128, 160, 192, and 224 of the 256-bit block; bit 1 of the Plane Mask enables or disables bits 1, 33, 65, 97, 129, 161, 193, and 225.

A particular sense amplifier bit can be written only if both the Dirty Tag bit and the Plane Mask bit are logically "1". This kind of relationship among multiple enables and block data is illustrated in Figure 3.2 for the first 40 bits (which are Word 0 and byte 0 of Word 1) of the Global Bus.

It is important to note the simultaneous effects of the Plane Mask. Although 3D-RAM allows concurrent operations of Pixel ALU and DRAM, the user is cautioned that there is only one set of Plane Mask bits that can affect both Pixel ALU write and DRAM write operations at the same time. When different plane maskings are required, concurrent Pixel ALU Stateful Data Write operations and DRAM Masked Write Block operations must be avoided.

Once the Plane Mask is written, the new Plane Mask is effective for only the Stateful Data Write operations issued at later cycles, thereby conforming to the uniform 7-stage pipeline rule. The Plane Mask register is loaded through a Pixel ALU "Write Control Register" operation. The mapping of the Plane Mask to the PALU\_DQ pins is the same as the Word data to the pins (see also the section on "Block and Word" on page 27).

Figure 3-2 The relationship between Dirty Tags and Plane Mask for first 40 bits of the Global Bus. (Both the Dirty Tag bit and the Plane Mask bit must be 1 before a particular Sense Amp bit can be written.)

## Preliminary Rev. 0.95 3D-RAM (M5M410092B)

# Elements and Operations of the Pixel ALU

Chapter 2 presented an overview of the Pixel ALU, with an emphasis on the motivation and applications of the elements in the Pixel ALU. In this section, some of the same information is repeated, but the emphasis is on detailed technical specification.

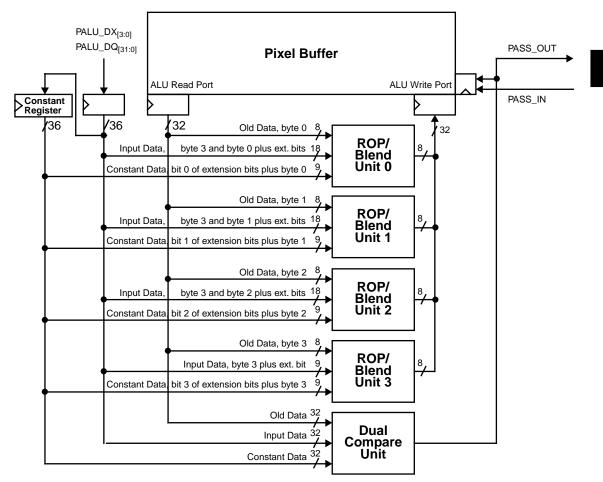

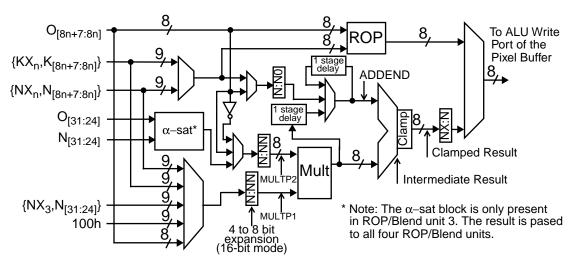

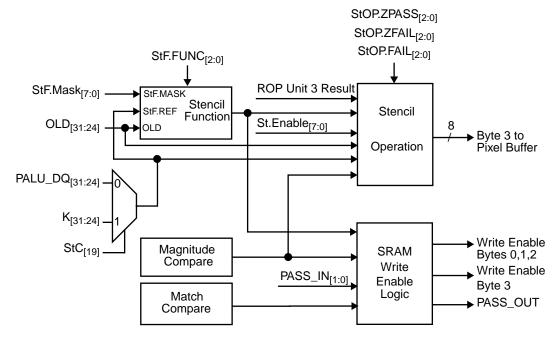

The elements of the Pixel ALU are four 8-bit ROP/ Blend units, one 32-bit Match Compare unit, one 32-bit Magnitude Compare unit, and the Picking Logic. Figure 3.3 shows the inputs to the ROP/ Blend units and the Dual Compare unit. In the figure, bus "O" is the old data from the Pixel Buffer; "N" and "NX" are from the PALU\_DX and PALU\_DQ pins, respectively; and finally, buses "KX" and "K" are from the internal 36-bit Constant Source register, with "KX" being the most significant four bits. The inputs to the Dual Compare unit are straightforward. The inputs to the ROP/Blend units are explained in the following sub-sections.

Figure 3.3 Pixel ALU (Pipeline stages are not shown)

3

#### **ROP/Blend Units**

Each ROP/Blend unit can be independently configured as either a ROP unit or a Blend unit through the programming of the ROP/Blend Control register. Each ROP unit can perform all 16 standard ROP functions, which are listed in Table 3.16. ROP functions are performed on a byte of the Old Data ("O") from the Pixel Buffer and a byte of the New Term, which is either the data from the data pins ("N") or the data from the Constant Source register ("K").

#### Pixel ALU Blend Modes (NEW)

For the blending operation, the general equation is as follows:

Write data to Pixel Buffer

- = New Term + (Old Data x Old Fraction)

- = (New Data x New Fraction) + (Old Data x Old Fraction)

To each Blend unit, an Addend (e.g. the "New Term" or 00h) is input from the PALU\_DX and PALU\_DQ pins (marked as {"NX", "N"}), from the Pixel Buffer (marked as "O"), or from the Constant Source register (marked as {"KX", "K"}). Multiplicand 1 (marked as "MULTP1") is the fraction term and is from one of five sources; Multiplicand 2 (marked as "MULTP2") is the data term and is from one of six sources. See Table 3.5 for a complete selection mapping of the Addend and Multiplicands.

In OpenGL terminology (see "The OpenGL Graphics System: A Specification (Version 1.1)"), New Data represents the color values of the source (SRC\_Color) which enter the Pixel ALU path from the PALU\_DQ pins; Old Data represents the color values of the destination (DST\_Color) which are from the Pixel Buffer. New Fraction is known as the source blend factor (sfactor); Old Fraction is known as the destination blend factor (dfactor). The color values, SRC\_Color and DST\_Color, can be represented in RGBA quadruplets form as (Rs, Gs, Bs, As) and (Rd, Gd, Bd, Ad), respectively. Define sfactor and dfactor as (Sr, Sg, Sb, Sa) and (Dr, Dg, Db, Da), respectively. The blending equation can be rewritten as:

Write data to Pixel Buffer

- = (SRC\_Color x sfactor) + (DST\_Color x dfactor)

- = (Rs, Gs, Bs, As) x (Sr, Sg, Sb, Sa) + (Rd, Gd, Bd, Ad) x (Dr, Dg, Db, Da)

- = (RsxSr+RdxDr, GsxSg+GdxDg, BsxSb+BdxDb, AsxSa+AdxDa)

All the possible values for OpenGL blending factors are listed in Table 3.2. The subtraction of quadruplets means subtracting them componentwise. The column "Relevant Factor" indicates whether the corresponding constant can be used to specify the source or destination blend factor.

The full blending function requires two multiplications and one addition for each of the four components in the quadruplet. Enumreating the eight possible values of destination blend factor and nine possible values of source blend factor, we arrive at the 72 blending modes illustrated in the matrix in Table 3.3. Not all of the combinations make sense. The majority of applications use a small number of combinations. Most of the blending modes with (0,0,0,0) or (1,1,1,1) as the blending factor can be realized with a half blender, meaning that they only require one multiplication and the addition. In addition, if one of the multiplications does not require destination colors or destination alpha from the frame buffer, this multiplication can be performed inside the rendering controller without having to read the destination data out of the frame buffer. Thus, only a half blender is needed inside the 3D-RAM to complete the blending equation in these cases. For the rest of the blending modes. the blending functions can be completed in two consecutive cycles using the 3D-RAM's Two-Cycle Blend operation by looping back the product term from the first cycle and combining it with the product term from the second cycle.

Table 3.2 Source and Destination Blending Factors

| Constant               | Relevant Factor       | Computed Blend Factor      |  |  |

|------------------------|-----------------------|----------------------------|--|--|

| GL_ZERO                | source or destination | (0,0,0,0)                  |  |  |

| GL_ONE                 | source or destination | (1,1,1,1)                  |  |  |

| GL_DST_COLOR           | source                | (Rd,Gd,Bd,Ad)              |  |  |

| GL_SRC_COLOR           | destination           | (Rs,Gs,Bs,As)              |  |  |

| GL_ONE_MINUS_DST_COLOR | source                | (1,1,1,1) – (Rd,Gd,Bd,Ad)  |  |  |

| GL_ONE_MINUS_SRC_COLOR | destination           | (1,1,1,1) – (Rs,Gs,Bs,As)  |  |  |

| GL_SRC_ALPHA           | source or destination | (As,As,As,As)              |  |  |

| GL_ONE_MINUS_SRC_ALPHA | source or destination | (1,1,1,1) – (As,As,As,As)  |  |  |

| GL_DST_ALPHA           | source or destination | (Ad,Ad,Ad,Ad)              |  |  |

| GL_ONE_MINUS_DST_ALPHA | source or destination | (1,1,1,1) – (Ad,Ad,Ad,Ad)  |  |  |

| GL_SRC_ALPHA_SATURATE  | source                | (f,f,f,1); f=min(As, 1–Ad) |  |  |

Table 3.3 OpenGL blending modes

|                         | Destination Blend Factor |     |               |                                 |               |                                 |               |                                 |  |

|-------------------------|--------------------------|-----|---------------|---------------------------------|---------------|---------------------------------|---------------|---------------------------------|--|

| Source Blend Factor     | ZERO                     | ONE | SRC_<br>COLOR | ONE_<br>MINUS_<br>SRC_<br>COLOR | SRC_<br>ALPHA | ONE_<br>MINUS_<br>SRC_<br>ALPHA | DST_<br>ALPHA | ONE_<br>MINUS_<br>DST_<br>ALPHA |  |

| ZERO                    | х                        | х   | x             | х                               | х             | x                               | x             | х                               |  |

| ONE                     | x                        | х   | х             | 0                               | х             | C, 0                            | х             | х                               |  |

| DST_COLOR               | x                        | x   | о             | о                               | 0             | о                               | о             | о                               |  |

| ONE_MINUS_<br>DST_COLOR | x                        | х   | 0             | 0                               | ο             | 0                               | 0             | 0                               |  |

| SRC_ALPHA               | x                        | x   | о             | о                               | с, о          | С, О                            | x             | х                               |  |

| ONE_MINUS_<br>SRC_ALPHA | x                        | x   | 0             | 0                               | C, 0          | C, O                            | х             | х                               |  |

| DST_ALPHA               | x                        | x   | о             | о                               | 0             | о                               | о             | о                               |  |

| ONE_MINUS_<br>DST_ALPHA | x                        | х   | 0             | Ο                               | 0             | 0                               | 0             | ο                               |  |

| SRC_ALPHA_<br>SATURATE  | x                        | х   | 0             | 0                               | 0             | 0                               | 0             | 0                               |  |

**Legend:** "x" = half blending in a single clock cycle; "o" = full blending in two cycles using the Two-Cycle Blend operation; "c" = one cycle blending with alpha blending ignored

3D-RAM accelerates 32 blending modes in single clock cycle throughput by half blending and the other 40 blending modes in two cycles. In addition, there are five cases, two-cycle blending modes may be accelerated in just one cycle if the alpha blending can be ignored.

#### Blending Mode Operation (NEW)

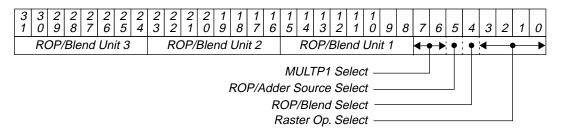

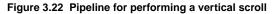

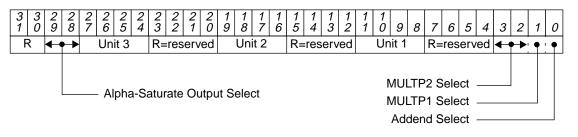

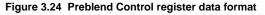

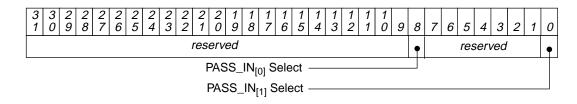

The simplified block diagram of the Blending unit is illustrated in Figure 3.4. To execute a singlecycle blending operation, the multiplicands and addend (MULTP1, MULTP2, Addend) must be selected by programming the ROP/Blend and Blend\_2 Control registers. Also, the ROP/Blend Control register must be set for blending. Once these registers are set, the blending operation is accomplished by performing a Stateful Write operation. Each Blend unit first performs the multiplication of the data term (MULTP2) and fraction term (MULTP1) and then the addition of the resulting product with the Addend, thereby completing a half blend.

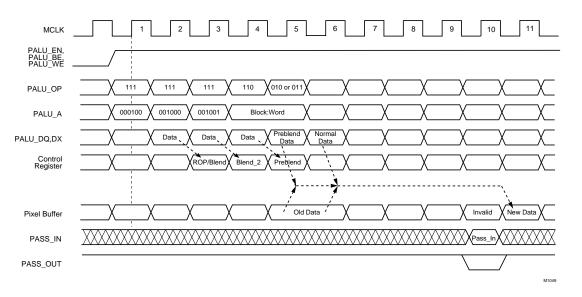

To execute a Two-Cycle Blend operation, it is necessary to program three registers. The ROP/ Blend and Blend\_2 Control registers are programmed just as they would be for a singlecycle blending operation. The selected MULTP1 and MULTP2 components will apply to the second cycle of the operation. The Addend selected by these two registers is ignored for the Two-Cycle Blend operation. The Preblend Control register selects MULTP2 for the Preblend Cycle (the first cycle during the Two-Cycle Blend operation) and the Addend for the Normal Cycle. MULTP1 and Addend are fixed to the PALU\_DQ bus for the Preblend Cycle. Once these three registers have been programmed, an "Initiate Two-Cycle Blending" operation (PALU\_OP=110, PALU WE=1) should be performed and followed by a Stateful Initial/Normal Write operation on the same pixel location (i.e. PALU\_A with the same Block:Word address and PALU\_BE<sub>[3:0]</sub> with the same enble settings). During the Preblend Cycle, MULTP1 and MULTP2 are multiplied and the result is "looped back" one stage in the pipeline.

The Addend is also "looped back" one stage. The Addend and the multiplier output are then available as possible Addends for the next cycle. Next, the Stateful Write is issued with the multiplicands selected by the ROP/Blend and Blend\_2 Control registers. The Addend selected by the ROP/Blend and Blend\_2 registers will be ignored. The blending occurs just as it would for a single-cycle operation except that the Addend source is chosen to be either the previous multiplier output or the previous Addend, based on the settings of the Preblend Control register.

Figure 3.4 illustrates the above description with a simplified block diagram. The blocks labelled "N:NN", "N:N0", and "NX:N" on the blending path represent the manner in which the 8-bit Blend units duplicate 4-bit data for the special (4,4,4,4) 16-bit color mode. Specifically, "N:NN" means that the 4-bit data is nibble-wise duplicated to form an 8-bit data; "N:N0" means an 8-bit data is formed by padding the lower nibble with 0000b; and "NX:N" means a 4-bit data is produced by truncating the lower nibble, regardless of its value. More explanations may be found in the section on "4-bit to 8-bit Expansion for Pixel ALU."

Note that the special OpenGL stencil mode, which will be described in the section on "Stencil Modes," uses portions of ROP/Blend unit 3 to accomplish its functions. For simplicity, the stencil logic is not shown in Figure 3.4 and, for the most part, can be thought of as a separate unit. It is important to note, however, that the stencil logic uses portions of the blending path and therefore, ROP/Blend unit 3 cannot be used for blending when the OpenGL stencil mode is being used.

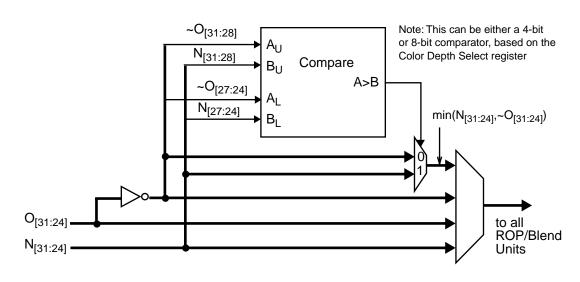

ROP/Blend units 0, 1 and 2 are identical, but unit 3 is slightly different because this unit typically handles the Alpha data. The Alpha-Saturate block shown in Figure 3.4 and Figure 3.5 is only present in ROP/Blend unit 3. The result from the Alpha-Saturate block is routed to all four ROP/Blend units as a possible source of MULTP2.

For the specifics of the data multiplexing and selections by the various register bits, refer to Figure 3.6. The timing diagram of an example

Two-Cycle Blend operation is presented in Figure 3.7.

Figure 3.4 ROP/Blend unit n (Pipeline stages ar not shown)

Figure 3.5 Block diagram of the Alpha-Saturate unit

3 Pixel ALU Operations

Graphics to be supplied in the next revision.

Figure 3.6 Details of data selections in Blend unit n by the various register bits

Figure 3.7 An Example of a Two-Cycle Blend operation

The mathematic operations performed in the Blend unit are summarized in Table 3.4. The Clamped Result is written to the Pixel Buffer, depending (1) on the PASS\_OUT pin, which is the result of internal Compare units, and (2) on the PASS\_IN<sub>[1:0]</sub> pins, which is the PASS\_OUT signal from the preceding 3D-RAM.

| Table 3.4 | Mathematical | operations in | Blend unit n |

|-----------|--------------|---------------|--------------|

|-----------|--------------|---------------|--------------|

| Operand                           | Range                              | Sources                                                    | Comments                                                                         |  |

|-----------------------------------|------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------|--|

| Multiplicand 1<br>(Fraction term) | 0.00h ~ 0.FFh<br>(8-bit unsigned)  | {NX <sub>n</sub> , N <sub>[8n+7:8n]</sub> }                | Source is from PALU_DX <sub>n</sub> and PALU_DQ <sub>[8n+7:8n]</sub> pins        |  |

|                                   | 0.00h ~ 0.FFh<br>(8-bit unsigned)  | {NX <sub>3</sub> , N <sub>[31:24]</sub> }                  | Source is from PALU_DX <sub>3</sub> and PALU_DQ <sub>[31:24]</sub> pins          |  |

|                                   | 0.00h ~ 0.FFh<br>(8-bit unsigned)  | O <sub>[8n+7:8n]</sub>                                     | Source is from the SRAM Pixel Buffer                                             |  |

|                                   | 0.00h ~ 0.FFh<br>(8-bit unsigned)  | {KX <sub>n</sub> , K <sub>[8n+7:8n]</sub> }                | Source is from the internal Constant Register                                    |  |

|                                   | 1.00h<br>(9-bit constant<br>1.00h) | 1.00h                                                      | Fractions greater than 1.00h are clamped to 1.00h                                |  |

| Multiplicand 2                    | 0 ~ 255                            | O <sub>[8n+7:8n]</sub>                                     | Source is from the SRAM Pixel Buffer                                             |  |

| (Data term)                       | (8-bit unsigned)                   | ~O <sub>[8n+7:8n]</sub>                                    | Source is inverted from O <sub>[8n+7:8n]</sub>                                   |  |

|                                   |                                    | min{N <sub>[31:24]</sub> , ~O <sub>[31:24]</sub> } (α-sat) | Source is from the $\alpha$ -saturate block in                                   |  |

|                                   |                                    | N <sub>[31:24]</sub>                                       | ROP/Blend Unit 3                                                                 |  |

|                                   |                                    | O <sub>[31:24]</sub>                                       |                                                                                  |  |

|                                   |                                    | ~O <sub>[31:24]</sub>                                      | _                                                                                |  |

| Addend                            | -256 ~ 255<br>(9-bit signed)       | {NX <sub>n</sub> , N <sub>[8n+7:8n]</sub> }                | Source is from PALU_DX <sub>n</sub> and PALU_DQ <sub>[8n+7:8n]</sub> pins        |  |

|                                   | -256 ~ 255<br>(9-bit signed)       | {KX <sub>n</sub> , K <sub>[8n+7:8n]</sub> }                | Source is from the internal Constant Register                                    |  |

|                                   | 0 ~ 255<br>(8-bit unsigned)        | O <sub>[8n+7:8n]</sub>                                     | Source is from the SRAM Pixel Buffer                                             |  |

|                                   | 0 ~ 255<br>(8-bit unsigned)        | Previous Addend<br>(N <sub>[8n+7:8n]</sub> )               | Source is from the previous stage<br>Addend (Loop Back Blending)                 |  |

|                                   | 0 ~ 255<br>(8-bit unsigned)        | MULTP1 x MULTP2                                            | Source is from the previous stage multiplier output (Loop Back Blending)         |  |

| Intermediate<br>Result            | -256 ~ 510<br>(10-bit signed)      | (MULTP1 x MULTP2) +<br>Addend                              |                                                                                  |  |

| Clamped<br>Result                 | 0 ~ 255<br>(8-bit unsigned)        | Intermediate Result                                        | The Clamped Result is written to the Pixel Buffer if the pass condition is valid |  |

|                                   |                                    |                                                            | If source > 255, result = $255$                                                  |  |

|                                   |                                    |                                                            | If source $< 0$ , result = 0                                                     |  |

The "Alpha" value, denoted as As and Ad, should be placed at the most significant byte of the respective bus, i.e. As at  $N_{[31:24]}$ , which is from PALU\_DQ<sub>[31:24]</sub>; and Ad at the O<sub>[31:24]</sub>, which is from the Pixel Buffer. Table 3.5 lists possible multiplicand/addend selections for each OpenGL blending mode. Note that the "Preblend Cycle" column only applies to two-cycle blending operations. Each table entry represents data for all four Blending units, and some entries contain two terms. The first term applies to blending units that are designated for blending color data (in Blend units 0, 1, and 2). The second term is for the Blend unit operating on the alpha value (unit 3). The individual color terms have been grouped together in the table for simplicity. For example, the term "Cd, Ad" represents "Rd, Gd, Bd, Ad" and "1–Cd, 1–Ad" represents "1–Rd, 1–Gd, 1–Bd, 1– Ad." Note that terms such as "1–Cd" and "1–Ad" that are generated inside the 3D-RAM are approximated by the 1's complement. For example, the term "1–Ad" is actually ~Ad, the bitwise inverse of Ad. Note also that in alpha\_saturate blending, the multiplicand selections for color and alpha are different. There are certainly more ways to do the blending operations than those listed in Table 3.5. This list demonstrates that the 3D-RAM does support all OpenGL blending modes.

Table 3.5 Multiplicand/Addend selection for each OpenGL blending mode

| Blending F | Fractions |        | Preblend   | Cycle        |              | Normal Cycle |                     |  |  |

|------------|-----------|--------|------------|--------------|--------------|--------------|---------------------|--|--|

| sfactor    | dfactor   | MULTP1 | MULTP2     | ADDEND       | MULTP1       | MULTP2       | ADDEND              |  |  |

| 0, 0       | 0, 0      | na     | na         | na           | 0,0 (from K) | Cd, Ad       | 0,0 (from DQ)       |  |  |

| 1, 1       | 0, 0      | na     | na         | na           | 0,0 (from K) | Cd, Ad       | Cs, As              |  |  |

| Cd, Ad     | 0, 0      | na     | na         | na           | Cs, As       | Cd, Ad       | 0,0 (from K)        |  |  |

| 1–Cd, 1–Ad | 0, 0      | na     | na         | na           | Cs, As       | 1–Cd, 1–Ad   | 0,0 (from K)        |  |  |

| As, As     | 0, 0      | na     | na         | na           | 0,0 (from K) | Cd, Ad       | Cs*As, As*As        |  |  |

|            |           | na     | na         | na           | Cs, As       | As, As       | 0,0 (from K)        |  |  |

| 1–As, 1–As | 0, 0      | na     | na         | na           | 0,0 (from K) | Cd, Ad       | Cs*(1-As), As*(1-As |  |  |

| Ad, Ad     | 0, 0      | na     | na         | na           | Cs, As       | Ad, Ad       | 0,0 (from K)        |  |  |

| 1–Ad, 1–Ad | 0, 0      | na     | na         | na           | Cs, As       | 1–Ad, 1–Ad   | 0,0 (from K)        |  |  |

| f, 1       | 0, 0      | na     | na         | na           | Cs, 1        | f, As        | 0,0 (from K)        |  |  |

| 0, 0       | 1, 1      | na     | na         | na           | 1, 1         | Cd, Ad       | 0,0 (from K)        |  |  |

| 1, 1       | 1, 1      | na     | na         | na           | 1, 1         | Cd, Ad       | Cs, As              |  |  |

| Cd, Ad     | 1, 1      | na     | na         | na           | Cs, As       | Cd, Ad       | Cd, Ad              |  |  |

| 1–Cd, 1–Ad | 1, 1      | na     | na         | na           | Cs, As       | 1–Cd, 1–Ad   | Cd, Ad              |  |  |

| As, As     | 1, 1      | na     | na         | na           | 1, 1         | Cd, Ad       | Cs*As, As*As        |  |  |

|            |           | na     | na         | na           | Cs, As       | As, As       | Cd, Ad              |  |  |

| 1–As, 1–As | 1, 1      | na     | na         | na           | 1, 1         | Cd, Ad       | Cs*(1-As), As*(1-As |  |  |

| Ad, Ad     | 1, 1      | na     | na         | na           | Cs, As       | Ad, Ad       | Cd, Ad              |  |  |

| 1–Ad, 1–Ad | 1, 1      | na     | na         | na           | Cs, As       | 1–Ad, 1–Ad   |                     |  |  |

| f, 1       | 1, 1      | na     | na         | na           | Cs, 1        | f, Ad        | Cd, As              |  |  |

| 0, 0       | Cs, As    | na     | na         | na           | Cs, As       | Cd, Ad       | 0,0 (from K)        |  |  |

| 1, 1       | Cs, As    | na     | na         | na           | Cs, As       | Cd, Ad       | Cs, As              |  |  |

| Cd, Ad     | Cs, As    | Cs, As | Cd, Ad     | х            | Cs, As       | Cd, Ad       | Loop Back(MPY)      |  |  |

| 1–Cd, 1–Ad | Cs, As    | Cs, As | 1–Cd, 1–Ad | х            | Cs, As       | Cd, Ad       | Loop Back(MPY)      |  |  |

| As, As     | Cs, As    | na     | na         | Cs*As, As*As | Cs, As       | Cd, Ad       | Loop Back(ADD)      |  |  |

|            |           | Cs, As | As, As     | х            | Cs, As       | Cd, Ad       | Loop Back(MPY)      |  |  |

Cs=Rs,Gs,Bs; Cd=Rd,Gd,Bd; x=don't care; na=not applicable; f=min(As,1-Ad); \*=arithmetic multiplication MPY=multiplier result; ADD=Addend term; K=Constant Source register; DQ=PALU\_DQ pins

| Blending   | Fractions  |        | Preblend   | Cycle                   |            | Normal ( | Cycle                            |

|------------|------------|--------|------------|-------------------------|------------|----------|----------------------------------|

| sfactor    | dfactor    | MULTP1 | MULTP2     | ADDEND                  | MULTP1     | MULTP2   | ADDEND                           |

| 1–As, 1–As | Cs, s      | na     | na         | Cs*(1–As),<br>As*(1–As) | Cs, As     | Cd, Ad   | Loop Back(ADD)                   |

| Ad, Ad     | Cs, As     | Cs, As | Ad, Ad     | х                       | Cs, As     | Cd, Ad   | Loop Back(MPY)                   |

| 1–Ad, 1–Ad | Cs, As     | Cs, As | 1–Ad, 1–Ad | х                       | Cs, As     | Cd, Ad   | Loop Back(MPY)                   |

| f, 1       | Cs, As     | Cs, na | f, na      | na, As                  | Cs, As     | Cd, Ad   | Loop Back(MPY)<br>Loop Back(ADD) |

| 0, 0       | 1–Cs, 1–As | na     | na         | na                      | 1–Cs, 1–As | Cd, Ad   | 0,0 (from K)                     |

| 1, 1       | 1–Cs, 1–As | na     | na         | Cs, As                  | 1–Cs, 1–As | Cd, Ad   | Loop Back(ADD)                   |

| Cd, Ad     | 1–Cs, 1–As | Cs, As | Cd, Ad     | х                       | 1–Cs, 1–As | Cd, Ad   | Loop Back(MPY)                   |

| 1–Cd, 1–Ad | 1–Cs, 1–As | Cs, As | 1–Cd, 1–Ad | х                       | 1–Cs, 1–As | Cd, Ad   | Loop Back(MPY)                   |

| As, As     | 1–Cs, 1–As | na     | na         | Cs*As, As*As            | 1–Cs, 1–As | Cd, Ad   | Loop Back(ADD)                   |

|            |            | Cs, As | As, As     | х                       | 1–Cs, 1–As | Cd, Ad   | Loop Back(MPY)                   |

| 1–As, 1–As | 1–Cs, 1–As | na     | na         | Cs*(1–As),<br>As*(1–As) | 1–Cs, 1–As | Cd, Ad   | Loop Back(ADD)                   |

| Ad, Ad     | 1–Cs, 1–As | Cs, As | Ad, Ad     | х                       | 1–Cs, 1–As | Cd, Ad   | Loop Back(MPY)                   |

| 1–Ad, 1–Ad | 1–Cs, 1–As | Cs, As | 1–Ad, 1–Ad | х                       | 1–Cs, 1–As | Cd, Ad   | Loop Back(MPY)                   |

| f, 1       | 1–Cs, 1–As | Cs, na | f, na      | na, As                  | 1–Cs, 1–As | Cd, Ad   | Loop Back(MPY)<br>Loop Back(ADD  |

| 0, 0       | As, As     | na     | na         | na                      | As, As     | Cd, Ad   | 0,0 (from K)                     |

| 1, 1       | As, As     | na     | na         | na                      | As, As     | Cd, Ad   | Cs, As                           |

| Cd, Ad     | As, As     | Cs, As | Cd, Ad     | х                       | As, As     | Cd, Ad   | Loop Back(MPY                    |

| 1–Cd, 1–Ad | As, As     | Cs, As | 1–Cd, 1–Ad | х                       | As, As     | Cd, Ad   | Loop Back(MPY)                   |

| As, As     | As, As     | na     | na         | na                      | As, As     | Cd, –    | Cs*As, –                         |

|            |            | Cs, As | As, As     | х                       | As, As     | Cd, Ad   | Loop Back(MPY)                   |

|            |            | na     | na         | na                      | As, –      | Cd, –    | Cs*(1–As), –                     |

| 1–As, 1–As | As, As     | х      | х          | Cs*(1–As),<br>As*(1–As) | As, As     | Cd, Ad   | Loop Back(ADD                    |

| Ad, Ad     | As, As     | Cs, As | Ad, Ad     | х                       | As, As     | Cd, Ad   | Loop Back(MPY                    |

| 1–Ad, 1–Ad | As, As     | Cs, As | 1–Ad, 1–Ad | х                       | As, As     | Cd, Ad   | Loop Back(MPY                    |

| f, 1       | As,As      | Cs, na | f, na      | na, As                  | As, As     | Cd, Ad   | Loop Back(MPY)<br>Loop Back(ADD) |

| 0, 0       | 1–As, 1–As | na     | na         | na                      | 1–As, 1–As | Cd, Ad   | 0,0 (from K)                     |

| 1, 1       | 1–As, 1–As | na     | na         | na                      | 1–As, –    | Cd, –    | Cs, –                            |

|            |            | х      | x          | Cs, As                  | 1–As, 1–As | Cd, Ad   | Loop Back(ADD)                   |

| Cd, Ad     | 1–As, 1–As | Cs, As | Cd, Ad     | x                       | 1–As, 1–As | Cd, Ad   | Loop Back(MPY                    |

| 1–Cd, 1–Ad | 1–As, 1–As | Cs, As | 1–Cd, 1–Ad | х                       | 1–As, 1–As | Cd, Ad   | Loop Back(MPY                    |

| As, As     | 1–As, 1–As | na     | na         | na                      | 1–As, 1–As | Cd, –    | Cs*As, –                         |

|            |            | Cs, As | As, As     | х                       | 1–As, 1–As | Cd, Ad   | Loop Back(MPY)                   |

|            |            | na     | na         | na                      | 1–As, 1–As | Cd, –    | Cs*(1–As), –                     |

| 1–As, 1–As | 1–As, 1–As | х      | х          | Cs*(1–As),<br>As*(1–As) | 1–As, 1–As | Cd, Ad   | Loop Back(ADD)                   |

| Ad, Ad     | 1–As, 1–As | Cs, As | Ad, Ad     | x                       | 1–As, 1–As | Cd, Ad   | Loop Back(MPY)                   |

| 1–Ad, 1–Ad | 1–As, 1–As | Cs, As | 1–Ad, 1–Ad | x                       | 1–As, 1–As | Cd, Ad   | Loop Back(MPY)                   |

| f, 1       | 1–As, 1–As | Cs, As | f, 1       | x                       | 1–As, 1–As | Cd, Ad   | Loop Back(MPY)                   |

Table 3.5 Multiplicand/Addend selection for each OpenGL blending mode

Cs=Rs,Gs,Bs; Cd=Rd,Gd,Bd; x=don't care; na=not applicable; f=min(As,1-Ad); \*=arithmetic multiplication MPY=multiplier result; ADD=Addend term; K=Constant Source register; DQ=PALU\_DQ pins

| Blending   | Fractions  |        | Preblend   | Cycle  | Normal Cycle |            |                                   |

|------------|------------|--------|------------|--------|--------------|------------|-----------------------------------|

| sfactor    | dfactor    | MULTP1 | MULTP2     | ADDEND | MULTP1       | MULTP2     | ADDEND                            |

| 0, 0       | Ad, Ad     | na     | na         | na     | Cd, Ad       | Cd, Ad     | 0,0 (from K)                      |

| 1, 1       | Ad, Ad     | na     | na         | na     | Cd, Ad       | Cd, Ad     | Cs, As                            |

| Cd, Ad     | Ad, Ad     | Cs, As | Cd, Ad     | х      | Cd, Ad       | Ad, Ad     | Loop Back(MPY)                    |

| 1–Cd, 1–Ad | Ad, Ad     | Cs, As | 1–Cd, 1–Ad | х      | Cd, Ad       | Ad, Ad     | Loop Back(MPY)                    |

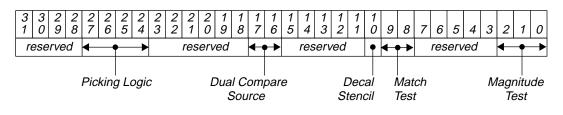

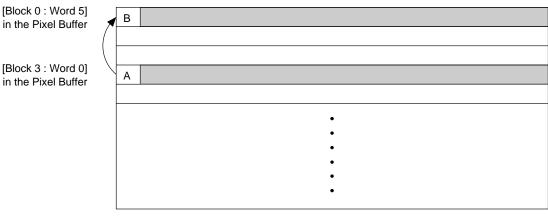

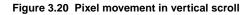

| As, As     | Ad, Ad     | na     | na         | na     | Cd, Ad       | Ad, Ad     | Cs*As, As*As                      |