#### DESCRIPTION

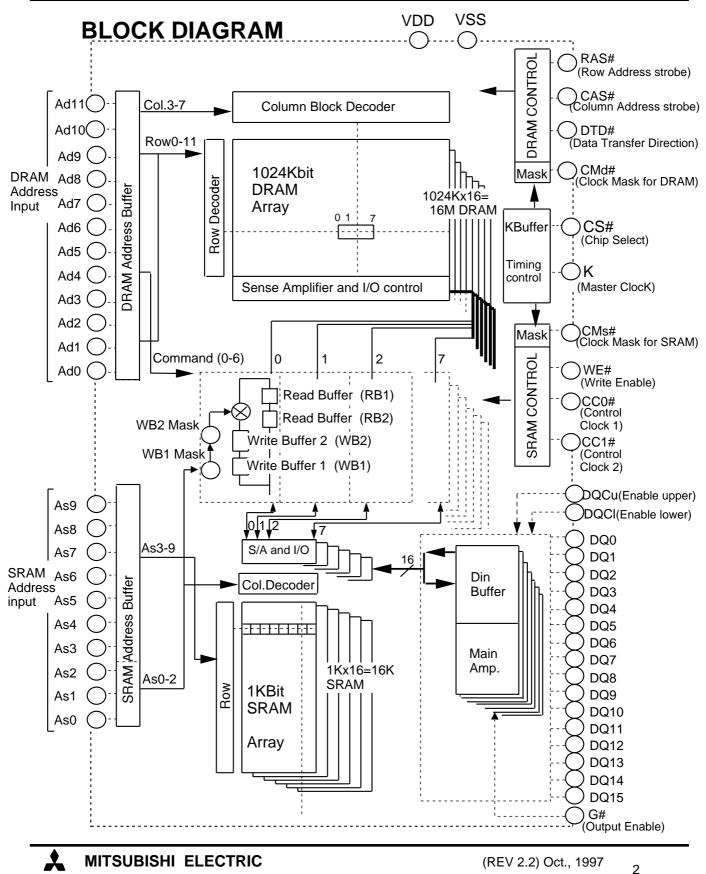

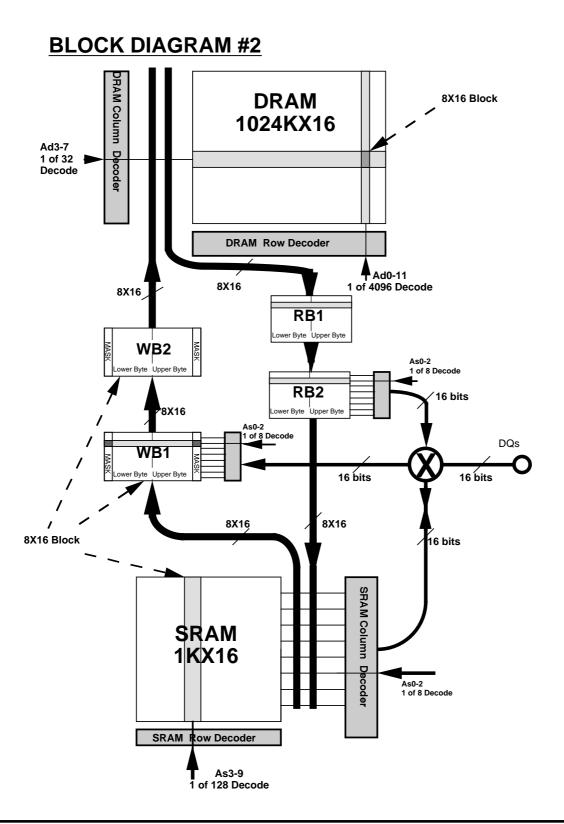

- The M5M4V16169TP is a 16M-bit Cached DRAM which integrates input registers, a 1,048,576-word by 16-bit dynamic memory array and a 1024- word by 16-bit static RAM array as a cache memory (block size 8x16) onto a single monolithic circuit. The block data transfer between the DRAM and the data transfer buffers (RB1/RB2/WB1/WB2) is performed in one instruction cycle, a fundamental advantage over the combination of conventional DRAM and SRAM cache.

- 2. The RAM is fabricated with a high performance CMOS process, and is ideal for large-capacity memory systems where high speed, low power dissipation, and low cost are essential. The use of quadruple-layer polysilicon process combined with silicide and double layer aluminum wiring technology, a single-transistor dynamic storage stacked capacitor cell, and a six-transistor static storage cache cell provides high circuit density at reduced costs.

#### **FEATURES**

| Type name       | SRAM<br>Access/cycle | DRAM<br>Access/cycle | Power<br>Dissipation (Typ) |  |  |

|-----------------|----------------------|----------------------|----------------------------|--|--|

| M5M4V16169TP-10 | 10ns/10ns            | 54ns/80ns            | DRAM: 460mW<br>SRAM: 990mW |  |  |

| M5M4V16169TP-12 | 11ns/12ns            | 56ns/96ns            | DRAM: 400mW<br>SRAM: 860mW |  |  |

| M5M4V16169TP-15 | 12ns/15ns            | 65ns/120ns           | DRAM: 330mW<br>SRAM: 760mW |  |  |

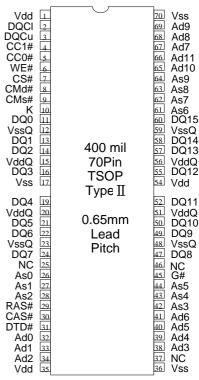

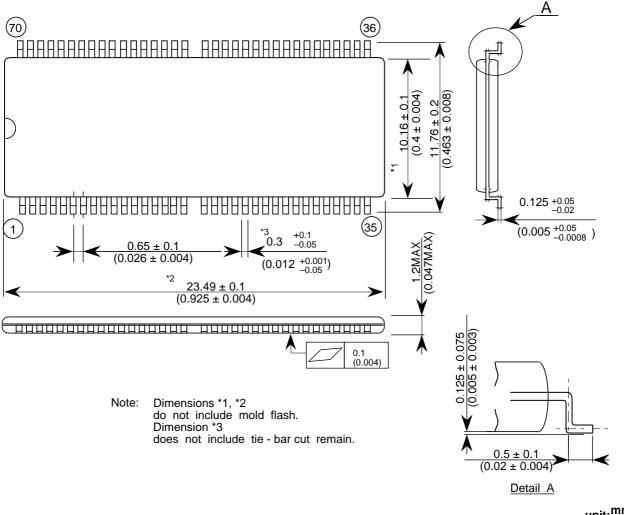

- 70-pin,400-mil TSOP (type I ) with 0.65mm lead pitch and 23.49mm package length.

- Multiplexed DRAM address inputs for reduced pin count and higher system densities.

- Selectable output operation (transparent / latched / registered) using set command register cycle.

- Single 3.3V +/- 0.3V Power Supply. (3.3V +/-0.15V for -10 part)

- 4096 refresh cycles every 64ms (Ad0 -> Ad11).

- Applicable for both direct-mapped and associative systems.

- Synchronous design for precise control with an external clock (K).

- Output retention by advanced mask clock (CMs#).

- All inputs/outputs low capacitance and LVTTL compatible.

- Asynchronous output enable (G#) for bus control.

- Separate DRAM and SRAM address inputs for fast SRAM access.

- Page Mode capability.

- Auto Refresh capability.

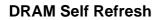

- Self Refresh capability.

#### PIN CONFIGURATION (TOP VIEW)

| Package code:70 |

|-----------------|

|-----------------|

| К         | : Master Clock            |

|-----------|---------------------------|

| CS#       | : Chip Select             |

| CMd#      | : DRAM Clock Mask         |

| RAS#      | : Row Addr. Strobe        |

| CAS#      | : Column Addr. Strobe     |

| DTD#      | : Data Transfer Direction |

| Ad        | : DRAM Address            |

| CMs#      | : SRAM Clock Mask         |

| CC0#,CC1; | #: Control Clocks         |

| WE#       | : Write Enable            |

| DQC(u/l)  | : I/O Byte Control        |

| As        | : SRAM Address            |

| G#        | : Output Enable           |

| DQ        | : Data I/O                |

| Vdd       | : Power Supply            |

| VddQ      | : DQ Power Supply         |

| Vss       | : Ground                  |

| VssQ      | : DQ Ground               |

1

## M5M4V16169TP-10,-12,-15

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

MITSUBISHI ELECTRIC

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

## FUNCTION TRUTH TABLE

| Mnemonic           |     | SRAM             |      |      | As (SRAM<br>address) |     |                      | DRAM             | 1                | Ad (DRAM a | ıddre | ss)                      |                  |             |     |

|--------------------|-----|------------------|------|------|----------------------|-----|----------------------|------------------|------------------|------------|-------|--------------------------|------------------|-------------|-----|

| CODE               | CS# | Previous<br>CMs# | CC0# | CC1# | DQC<br>(u/l)         | WE# | As0-9                | Previous<br>CMd# | RAS#             | CAS#       | DTD#  | Ad0-11                   | Ad2              | Ad1         | Ad0 |

| NOP                | Н   | Н                | Х    | Х    | Х                    | Х   | Х                    | Н                | Х                | Х          | Х     | Х                        | -<br>-<br>-<br>- |             |     |

| SPD                | Х   | L                | Х    | Х    | Х                    | Х   | Х                    | Х                | Х                | Х          | Х     | Х                        |                  |             |     |

| DES                | L   | Н                | Н    | Н    | Х                    | Х   | Х                    | х                | Х                | Х          | Х     | Х                        | -<br>-<br>-<br>- | 1           |     |

| SR <sup>(10)</sup> | L   | Н                | н    | L    | H/L <sup>(11)</sup>  | Н   | As0-9                | х                | Х                | Х          | Х     | Х                        | -<br>-<br>-<br>- | 1           |     |

| SW <sup>(10)</sup> | L   | Н                | н    | L    | (11)<br>H/L          | L   | As0-9                | Х                | Х                | Х          | Х     | Х                        |                  | -           |     |

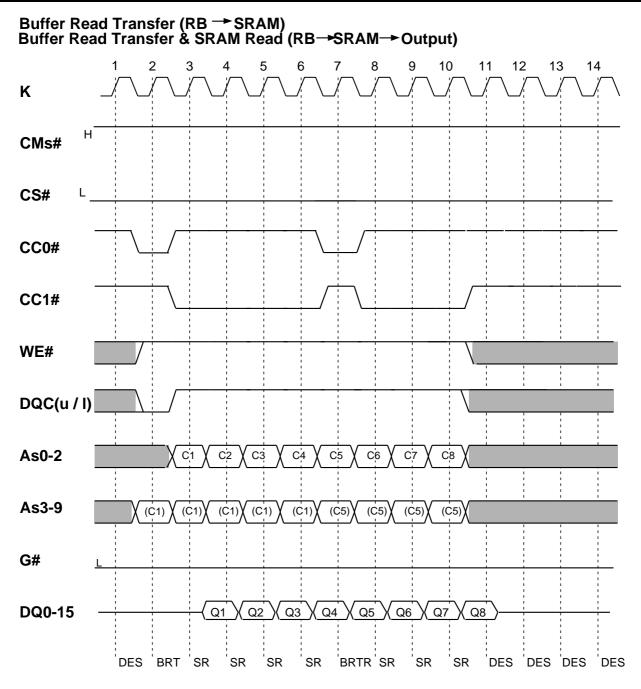

| BRT                | L   | Н                | L    | Н    | L                    | Н   | As3-9                | х                | Х                | Х          | Х     | Х                        | <br> <br> <br>   | 1           |     |

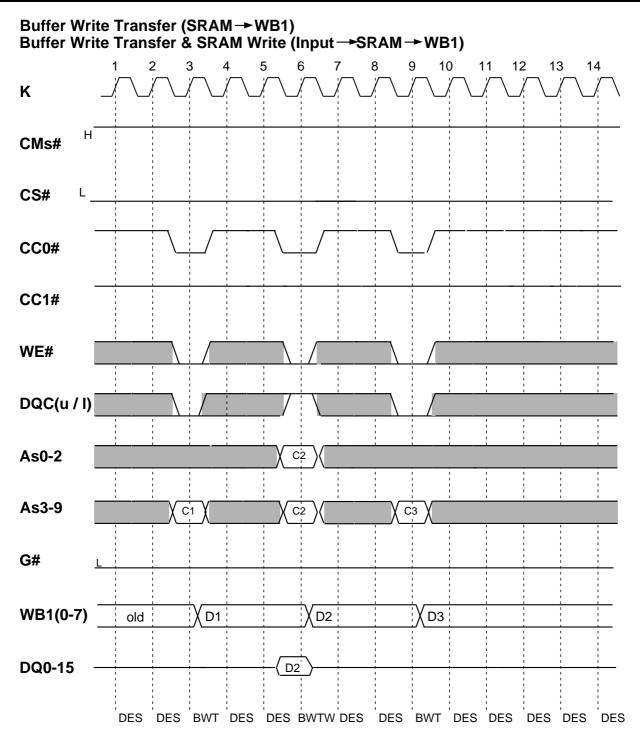

| BWT                | L   | Н                | L    | Н    | L                    | L   | As3-9                | х                | Х                | Х          | Х     | х                        |                  |             |     |

| BRTR (10)          | L   | Н                | L    | Н    | (11)<br>H/L          | н   | As0-9                | Х                | Х                | Х          | Х     | Х                        | 1                |             |     |

| (10)<br>BWTW       | L   | Н                | L    | Н    | (11)<br>H/L          | L   | As0-9                | х                | Х                | Х          | Х     | Х                        | -<br>-<br>-      |             |     |

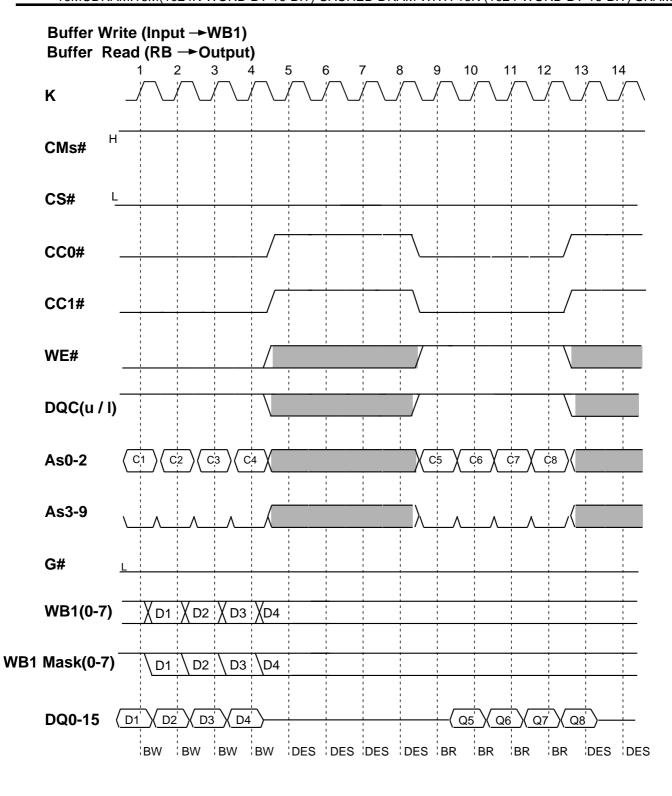

| BR <sup>(10)</sup> | L   | Н                | L    | L    | (11)<br>H/L          | Н   | As0-2 <sup>(2)</sup> | х                | Х                | Х          | Х     | Х                        | 1                | -           |     |

| BW (10)            | L   | Н                | L    | L    | (11)<br>H/L          | L   | As0-2 <sup>(2)</sup> |                  | Х                | Х          | Х     | Х                        | 1                |             | -   |

| DPD                | Х   | Х                | Х    | Х    | Х                    | Х   | Х                    | L                | X <sup>(1)</sup> | χ(1)       | χ(1)  | Х                        | <br> <br>        |             |     |

| DNOP               | L   | х                | Х    | Х    | х                    | х   | х                    | н                | Н                | Н          | Х     | х                        |                  |             |     |

| DRT                | L   | Х                | Х    | Х    | Х                    | Х   | Х                    | н                | Н                | L          | Н     | Ad3-7 (2)<br>(Col.Block) | 0                | 0           | 0   |

| DWT1               | L   | х                | х    | х    | х                    | х   | х                    | н                | н                | L          | L     | Ad3-7 (2)<br>(Col.Block) | 0                | 0           | 0   |

| DWT1R              | L   | х                | Х    | Х    | х                    | Х   | Х                    | н                | н                | L          | L     |                          | 0                | 0           | 1   |

| DWT2               | L   | Х                | Х    | Х    | х                    | х   | Х                    | н                | н                | L          | L     | Ad3-7 (2)<br>(Col.Block) | 0                | 1           | 0   |

| DWT2R              | L   | Х                | Х    | Х    | Х                    | Х   | Х                    | н                | н                | L          | L     | Ad3-7 (2)<br>(Col.Block) | 0                | 1           | 1   |

| ACT                | L   | х                | х    | х    | х                    | х   | х                    | H <sup>(9)</sup> | L                | н          | Н     | Ad0-11<br>(Row Add.)     |                  | -           |     |

| PCG                | L   | Х                | х    | Х    | х                    | х   | х                    | н                | L                | н          | L     | X                        |                  |             |     |

| ARF                | L   | х                | х    | х    | х                    | х   | х                    | H <sup>(7)</sup> | L                | L          | н     | х                        | <br> <br> <br>   | <br> <br>   |     |

| SRF                | L   | х                | х    | х    | х                    | х   | х                    | H <sup>(8)</sup> |                  | L          | н     | х                        | <br> <br>        | -<br>-<br>- |     |

| SCR                | L   | Х                | Х    | х    | х                    | х   | х                    | н                | L                | L          | L     | Command                  | <br> <br>        |             |     |

NOTES

1) For the DPD function, the RAS#, CAS# and DTD# inputs are DON'T CARE except for the L,L,H combination

For the DPD function, the RAS#, CAS# and DTD# inputs are DON'T CARE except for the L,L,H combination (Respectively).

The unused addresses must be set to Low.

Use New: If BW or BWT or BWTW is initiated the same cycle as DWT1 or DWT1R, new data is loaded into the buffer and transferred to DRAM.

Clear 1 or 2 Transfer Mask Bits (as addressed by As0-2 and DQCU/L).

Actual number of bits transfer depends on the state of the DTBW Mask and the DQCU/DQCL inputs. Note: If DQC(U/L) is Low, the corresponding DQ(s) is(are) disabled (Input and Output Buffer). SR,SW,BR and BW cycles with DQCU and DQCL Low result in a Deselect SRAM operation.

Following a DWT1 or DWT1R cycle, the entire WB1 Transfer Mask is Set (i.e., data can no longer be transferred from WB1 to DRAM. Succeeding Buffer-Writes or Buffer Write Transfers will Clear Mask bits.

CMd# during current cycle must be High (see timing diagram for Auto-Refresh).

CMd# during current cycle must be Low (see timing diagram for Self-Refresh).

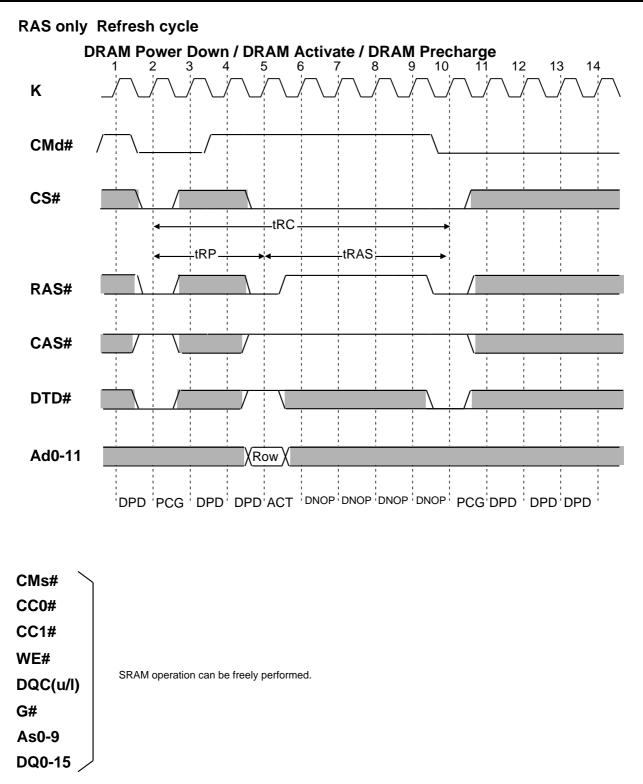

ARAS only refresh can be accomplished by issuing an ACT followed by PCG. (tRC must be observed)

These functions can be used with Burst Mode.

When DQCU is Low, DQ 15-8 are in a high Z state. When DQCL is Low DQ 7-0 are in a high Z state. See DQCU/L Pin Description for more detail.

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

|         |              |                                 |              |                       | -     |         |                                    |                                  |  |

|---------|--------------|---------------------------------|--------------|-----------------------|-------|---------|------------------------------------|----------------------------------|--|

| \\/rite |              | <u>a Transf</u><br>fers Xfer    |              |                       | DQ    | pin     | Function                           |                                  |  |

| WB1     | WB2          | WB1<br>Mask                     | WB2<br>Mask  | Read<br>Buffer<br>1,2 | Din   | Dout    |                                    |                                  |  |

| -       | -            | -                               | -            | -                     | -     | Hi-Z    | No OPeration                       |                                  |  |

| -       | -            | -                               | -            | -                     | -     | Suspend | SRAM Power Down&<br>Data retention | No operation                     |  |

| _       | -            | -                               | -            | -                     | -     | Hi-Z    | Deselect SRAM                      | No operation                     |  |

| -       | -            | -                               | -            | -                     | -     | Valid   | SRAM Read                          | SRAM->DO                         |  |

| -       | -            | -                               | _            | -                     | Valid | Hi-Z    | SRAM Write                         | DIN->SRAM                        |  |

| -       | -            | -                               | -            | Use                   | -     | Hi-Z    | Buffer Read Xfer                   | RB->SRAM                         |  |

| Load    | -            | Clear<br>Mask                   | I            | -                     | -     | Hi-Z    | Buffer Write Xfer                  | SRAM->WB1                        |  |

| -       | -            | -                               | I            | Use                   | -     | Valid   | Buffer Read Xfer & Read            | RB->SRAM->DO                     |  |

| Load    | -            | Clear<br>Mask                   | I            | -                     | Valid | Hi-Z    | Buffer Write Xfer & Write          | DIN->SRAM->WB1                   |  |

| -       | -            | -                               | I            | Use                   | -     | Valid   | Buffer Read                        | RB->DO                           |  |

| Load    | -            | Clear 1 <b>(4)</b><br>or 2 bits | -            | -                     | Valid | Hi-Z    | Buffer Write                       | DIN->WB1                         |  |

| _       | -            | -                               | -            | -                     | -     | -       | DRAM Power Down                    | No operation                     |  |

| -       | -            | -                               | -            | -                     | -     | -       | DRAM No OPeration                  | No operation                     |  |

| -       | -            | -                               | -            | Load                  | -     | -       | DRAM Read Xfer                     | DRAM->RB1->RB2                   |  |

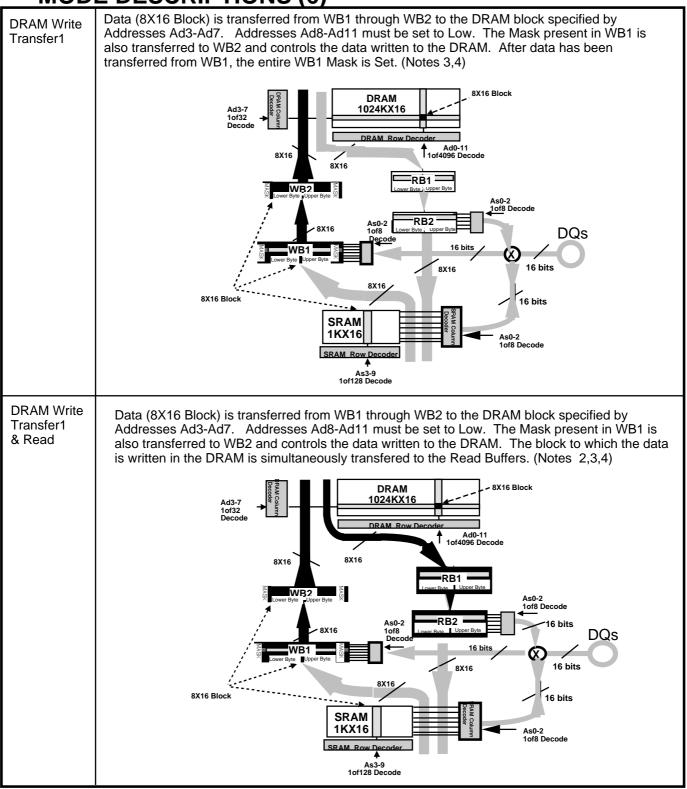

| Use     | Load/<br>Use | Use <sup>(6)</sup>              | Load/<br>Use | -                     | -     | -       | DRAM Write Xfer1                   | <b>(3)</b><br>WB1->WB2->DRAM     |  |

| Use     | Load/<br>Use | Use <b>(6)</b>                  | Load/<br>Use | Load                  | -     | -       | DRAM Write Xfer1<br>& Read         | WB1->WB2-> (3)<br>DRAM->RB1->RB2 |  |

| -       | Use          | -                               | Use          | -                     | -     | -       | DRAM Write Xfer2                   | WB2->DRAM                        |  |

| -       | Use          | -                               | Use          | Load                  | -     | -       | DRAM Write Xfer<br>& Read          | WB2->DRAM-><br>RB1->RB2          |  |

| _       | -            | -                               | I            | _                     | -     | -       | DRAM Activate                      | Page Call                        |  |

| _       | -            | _                               | _            | -                     | -     | -       | DRAM Precharge                     |                                  |  |

| _       | -            | -                               | Ι            | -                     | -     | -       | Auto Refresh                       |                                  |  |

| _       | -            | -                               | -            | -                     | -     | _       | Self Refresh Entry                 |                                  |  |

| -       | _            | -                               | -            | _                     | -     | _       | Set Command Register               |                                  |  |

## FUNCTION TRUTH TABLE

| Function    | Data Transferred (max)   |

|-------------|--------------------------|

| Din> SRAM   | 8/16 bits (5)            |

| Din> WB1    | 8/16bits (5)             |

| SRAM> WB1   | 128 bits (8X16bit-block) |

| WB1> WB2    | 128 bits (8X16bit-block) |

| WB2> DRAM   | 128 bits (8X16bit-block) |

| WB2 -> RB1  | 128 bits (8X16bit-block) |

| DRAM -> RB1 | 128 bits (8X16bit-block) |

| RB1> RB2    | 128 bits (8X16bit-block) |

| RB2> Dout   | 8/16 bits (5)            |

| RB2> SRAM   | 128 bits (8X16bit-block) |

DO: Data Out DIN: Data In WB1: Write Buffer 1 WB2: Write Buffer 2 RB1: Read Buffer 1 RB2: Read Buffer 2

Footnotes on previous page.

MITSUBISHI ELECTRIC

1

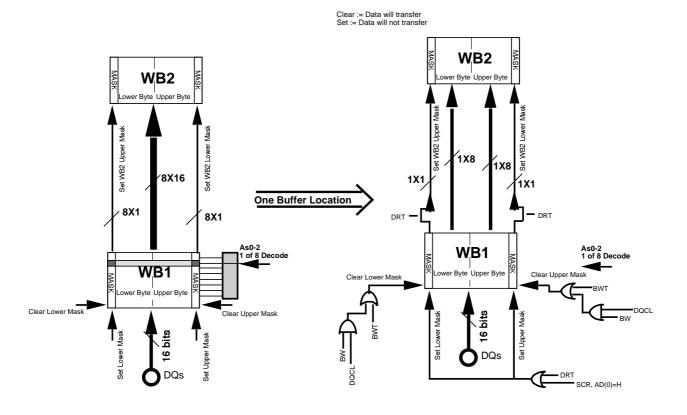

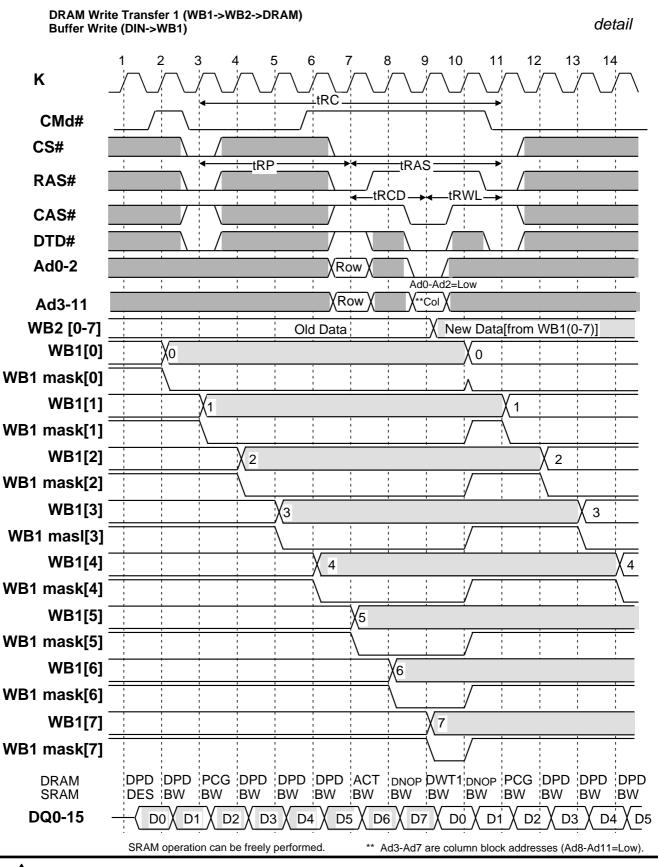

## Detail of Write Buffer Transfer Masks:

Write Buffer 1 (WB1) and Write Buffer 2 (WB2) both have a transfer mask associated with them. These masks when not set or "cleared" will allow data that has been written to WB1 to pass to WB2, and from WB2 to the DRAM. When the mask is "set" the data in the write buffer is not allowed to be transferred to WB2 or to the DRAM.

#### Write Buffer 1 mask:

The transfer mask has two masking bits associate with each of the eight words of data that can be written to the buffer. The two bits per word are associated with DQCU and DQCL. If DQCU or DQCL is used, to mask the I/O while writing to the buffer, the corresponding mask bit is set for the 8-bits not being written and cleared for those that are being written. Otherwise if DQCU/L are not used to mask the I/O during a buffer write both bits associated with the buffer write address are cleared. The mask bits that are cleared will allow the data written to their corresponding address to pass to the WB2 during a DRT or a DRTR. At the same time the data is transferred the contents of WB1 mask is transferred to the WB2 mask.

The mask associated with WB1 is cleared during a buffer write (BW), buffer write transfer (BWT), or buffer write transfer write (BWTW). In the case of the BWTW all bits are cleared except those associated with the the buffer address. The two bits that correspond to the buffer address are set according to DQCU and DQCL. The mask is set with a dram read transfer (DRT), dram read transfer read (DRTR), or an SCR with Ad(0) = H.

#### Write Buffer 2 mask:

The WB2 mask is set from the state of the WB1 mask when a DRT or a DRTR occurs. The mask data from the WB1 is held in the WB2 mask until another DRT or DRTR occurs. If a bit is set in the WB2 mask the data will not be transferred to the DRAM. If the bit is cleared the data will be allowed to transfer to the DRAM.

MITSUBISHI ELECTRIC

M5M4V16169TP-10,-12,-15 16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

# **PIN DESCRIPTIONS(1)**

|          | -     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| к        | Input | Master Clock Provides the fundamental timing and the internal clock frequency for the CDRAM. All external timing parameters (with the exception of G# in read cycle and CMd# in Self refresh cycle) are specified with respect to either the rising or falling edge of K.                                                                                                                                                                                                                                                 |

| CMd#     | Input | DRAM Clock Mask controls the operation of the internal DRAM master clock (K). When CMd# is Low at the rising edge of K, the internal DRAM master clock (K) for the following cycle is ceased and input stages are powered-off, resulting in a DRAM Power Down.                                                                                                                                                                                                                                                            |

| RAS#     | Input | Row Address Strobe is used in conjunction with Master clock K (depending on the states of CMd#, CAS#, and DTD#) to activate the DRAM (latching the Row Address lines and accessing 1 of 4096 rows), initiate a DRAM precharge cycle, perform a DRAM Read or Write Transfer, DRAM Write Transfer & Read, set the command registers, start an Auto-Refresh cycle, enter a Self-Refresh cycle,create a DRAM NOP cycle, or power down the DRAM.                                                                               |

| CAS#     | Input | Column Address Strobe is used in conjunction with the Master Clock K to latch the Column addresses. When preceded by RAS# in a DRAM access cycle, CAS# initiates a DRAM Write Transfer (WB1/2 -> DRAM, if DTD#=L), DRAM Write Transfer & Read (WB1/2 -> DRAM -> RB, if DTD#=L) or DRAM Read Transfer (DRAM -> RB, if DTD#=H), depending on the state of DTD# (see DTD# pin description).                                                                                                                                  |

| DTD#     | Input | Data Transfer Direction controls DRAM-to-RB(read) / WB-to-DRAM (write) direction. If preceded by a RAS# low cycle, both CAS# and DTD# low (on the rising edge of K) initiate a DRAM Write Transfer cycle. If DTD# stays High with the above conditions, a DRAM Read Transfer cycle results. DTD# can also initiate DRAM Activate, DRAM Precharge, Auto-Refresh, Set-Command Register, and Self Refresh cycles.                                                                                                            |

| Ad0-Ad11 | Input | DRAM Address Lines are Multiplexed to reduce pin count. Ad0-Ad11 (@<br>RAS=low,CAS=high,DTD=high, K=Rising edge) specify the Row Address of the<br>DRAM to activate and refresh the selected page and Ad3-Ad7 (@<br>RAS=high,CAS=low,K=Rising edge) specify the Block Address of the DRAM. In<br>addition, Ad0-Ad2 (@ RAS=high,CAS=low, K=Rising edge) specify the transfer<br>operation of the DRAM . Also Ad0-Ad11 (@RAS=low,CAS=low, DTD=low,<br>K=Rising Edge) are used as the command in set command register cycle. |

| CS#      | Input | The Chip Select controls the operation of the CDRAM. When CSd#=H at the rising edge of K and the previous CMd# or CMs# is high, the chip is in No Operation mode.                                                                                                                                                                                                                                                                                                                                                         |

| CMs#     | Input | SRAM Clock Mask controls the operation of the internal SRAM master clock (Ks).<br>When CMs# is asserted at a rising edge of K, the internal SRAM master clock for<br>the following cycle is suspended, resulting in the power down of the SRAM portion<br>of the circuit, including the Sense Amps. CMs# can also be used to retain output<br>data during SRAM power-down.                                                                                                                                                |

M5M4V16169TP-10,-12,-15 16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

# **PIN DESCRIPTIONS(2)**

| DQCu,DQCl | Input               | DQCu/I are I/OByte control signals. If G#=Low, DQCu/I have a control of output impedence: DQCu controls upper DQs (DQ8-15) & DQCI controls lower DQs (DQ0-7). DQCu/I also control both input data during SRAM Writes or Buffer Writes and transfer mask during Buffer Writes. (WB1 transfer Mask for each byte is written (bits are cleared) during Buffer Writes depending on DQCu/I inputs.)                                                  |

|-----------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WE#       | Input               | Write Enable controls SRAM and Buffer read and write operations. A high on the WE# pin causes either a Buffer Read, SRAM Read, Buffer Read Transfer and/or a Buffer Read Transfer & Read to occur (depending on the state of the CCO# and CC1# bits). A low on the WE# pin causes either a Buffer Write, SRAM Write, Buffer Write Transfer and/or a Buffer Write Transfer & Write to occur (depending on the state of the CCO# and CC1# inputs) |

| CC0#,CC1# | Inputs              | The Control Clock Inputs control SRAM and Buffer operations. CC0# is Low for all Buffer Writes, Reads, and Transfers, and High for all other SRAM operations. CC1# is high for all Buffer Read Transfers and Buffer Write Transfers.                                                                                                                                                                                                            |

| As0-As9   | Inputs              | SRAM Addresses are non-multiplexed, and access 1024 - 16-bit words (configured as 128 Rows X 8 Columns X 16 Bits, where the Block Size is 8 X 16) in the SRAM array. As0-As2 select word address within a block, and As3-As9 select the SRAM row(block).                                                                                                                                                                                        |

| G#        | Input               | The Output Enable is an asynchronous input. G#=high forces the outputs to high impedence.                                                                                                                                                                                                                                                                                                                                                       |

| DQ0-DQ15  | Inputs /<br>Outputs | Output operation is either transparent, latched, or registered depending on the state of the command register. The Data Lines for the CDRAM are asynchronously controlled by G#.                                                                                                                                                                                                                                                                |

|           |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

M5M4V16169TP-10,-12,-15 16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

# **MODE DESCRIPTIONS (1)**

| NOP                | No Operation. Outputs are high-impedance. All input buffers remain active.                                                                                                                                                                                                                     |  |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SRAM<br>Power-Down | If CMs#=Low at the rising edge of K, the SRAM enters SRAM Power Down at the next rising edge of K. During this mode, the internal SRAM K clock becomes inactive. The Output Buffers remain enabled and are controlled by G#. All input buffers of SRAM clocks and SRAM addresses are inactive. |  |  |  |  |  |

| Deselect SRAM      | All transfer functions and input/output operations to and from the SRAM and Buffer are disabled. This cycle is useful for output impedence control (Hi-Z,Low-Z) without G#. Output buffers are active during this cycle for registered output mode control.                                    |  |  |  |  |  |

| SRAM Read          | Data is read from the SRAM to the I/O pins. Addresses As0-As9 are used to select the data to be read. As3-As9 decode the SRAM Row (=Block), and As0-As2 decode (1 of 8) the 16-bit word. DQCu and DQCI control the impedence (High-Z/Low-Z) of the upper and lower bytes, respectively.        |  |  |  |  |  |

| SRAM Write         | Bata is written from the I/O pins to the SRAM. Addresses As0-As9 are used to select the location to be written. DQCu and DQCI control Upper and Lower byte writes, expectively.                                                                                                                |  |  |  |  |  |

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

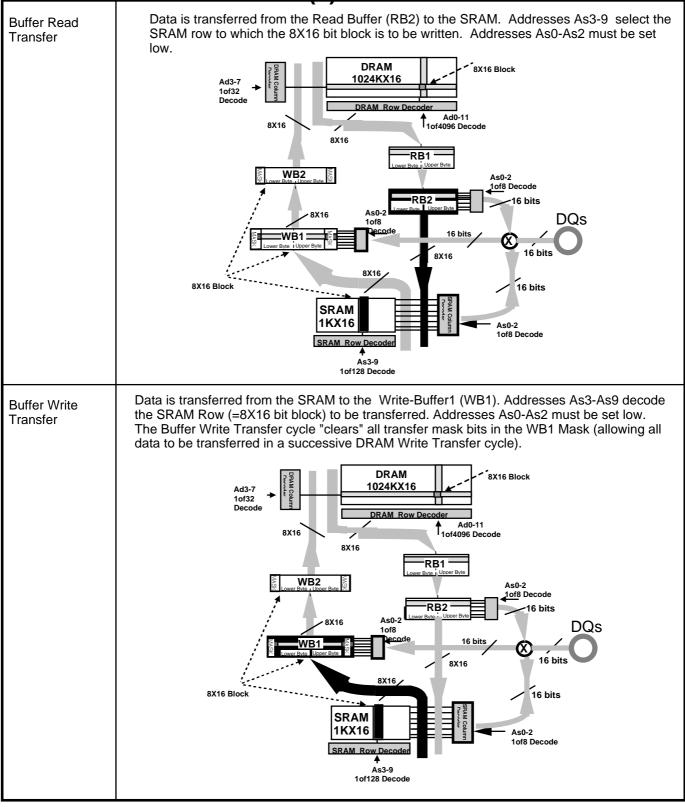

## **MODE DESCRIPTIONS (2)**

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

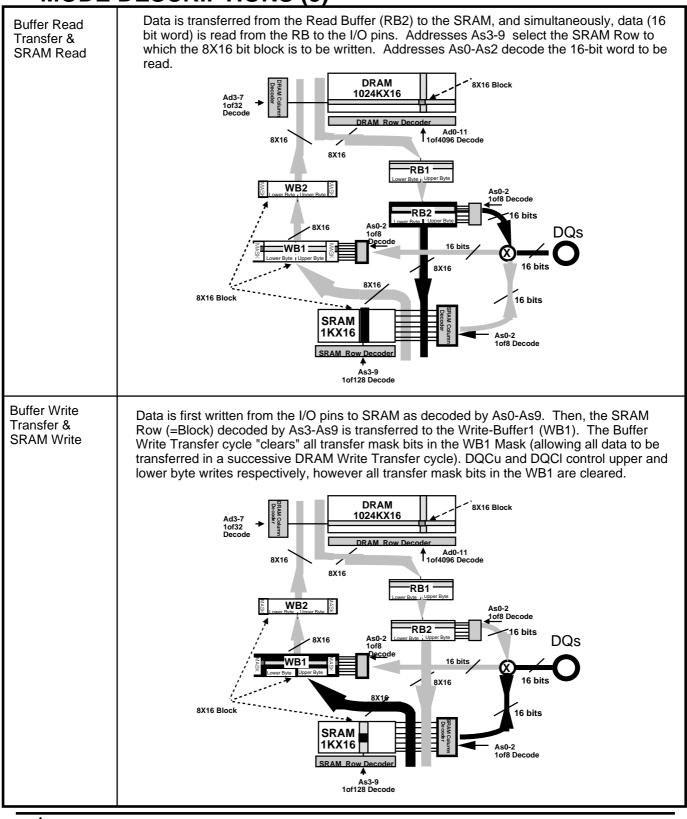

## **MODE DESCRIPTIONS (3)**

MITSUBISHI ELECTRIC

## M5M4V16169TP-10,-12,-15

(REV 2.2) Oct., 1997

12

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

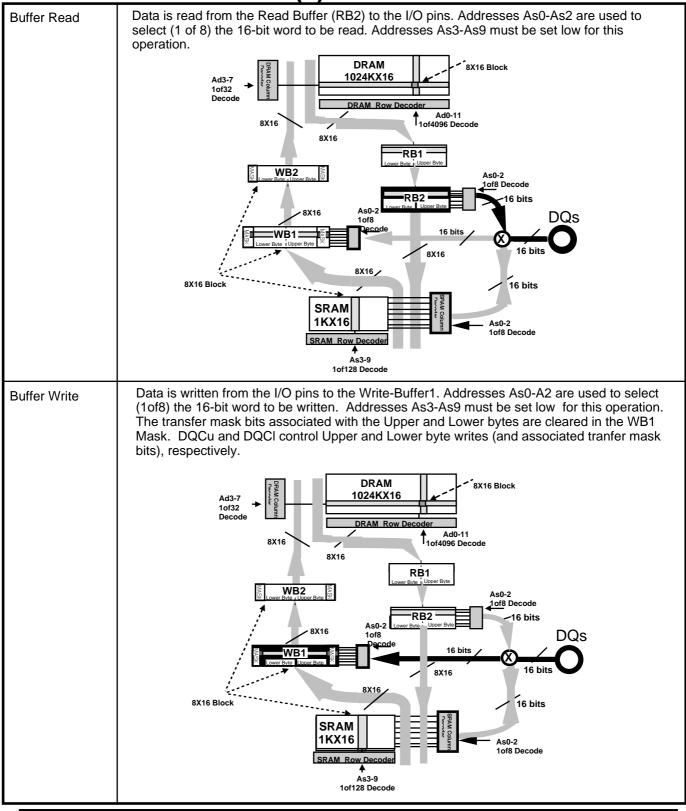

# **MODE DESCRIPTIONS (4)**

L

**MITSUBISHI ELECTRIC**

M5M4V16169TP-10,-12,-15 16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

## **MODE DESCRIPTIONS (5)**

| DRAM<br>Power-Down    | If CMd#=Low at the rising edge of K, the DRAM enters DRAM Power Down at the next rising edge of K. During this mode, the internal DRAM K clock becomes inactive. Also all input buffers of DRAM clocks and DRAM addresses are inactive. Note that the latency of DRAM Read Transfer cycle is not counted up in this cycle.                     |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRAM NOP              | The DNOP cycle is used when no other DRAM operations are desired, holding the DRAM in its present (precharge/activate) state.                                                                                                                                                                                                                  |

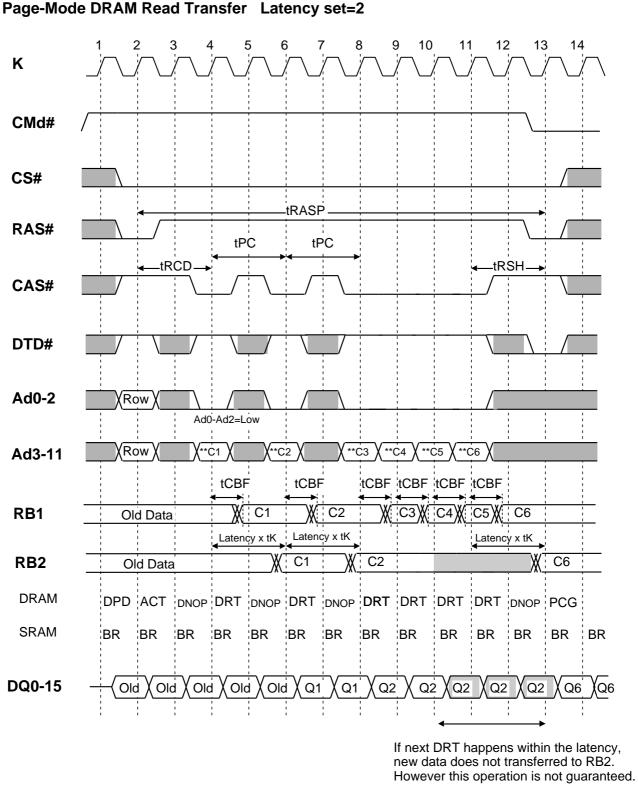

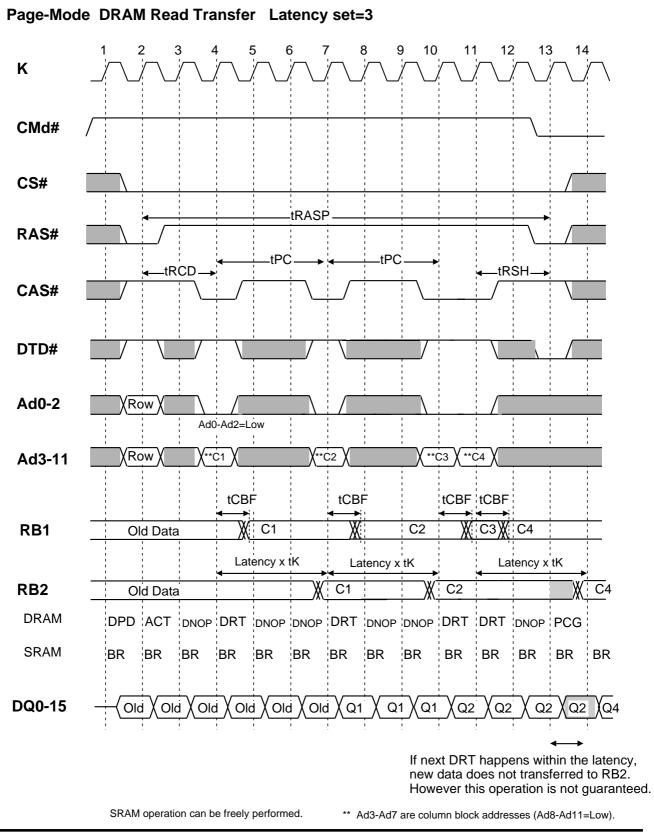

| DRAM Read<br>Transfer | A Block (8X16) is transferred from the DRAM to the Read Buffer (RB1/RB2) as specified by Addresses Ad3-Ad7. Addresses Ad8-Ad11 must be set to Low. After the Latency Period (specified in the Access Latency Table) new data will be present in the Read Buffers. Prior to the Latency timeout, old data will be present in RB2. (Notes 1,2,4) |

## M5M4V16169TP-10,-12,-15

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

## **MODE DESCRIPTIONS (6)**

(REV 2.2) Oct., 1997

15

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

## **MODE DESCRIPTIONS (7)**

**MITSUBISHI ELECTRIC**

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

## **MODE DESCRIPTIONS (8)**

| DRAM<br>Activate           | Addresses are latched from the Ad0-Ad11 inputs by the rising edge of K. Internally, a DRAM row is selected (Page Call) in preparation for a DRAM Read or Write Transfer cycle. A DRAM Precharge cycle must separate all DRAM Activate cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRAM<br>Precharge          | Internally, the active DRAM row is deselected (completing the refresh process) and page-mode is disabled. The DRAM is precharged prior to another DRAM Activate cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

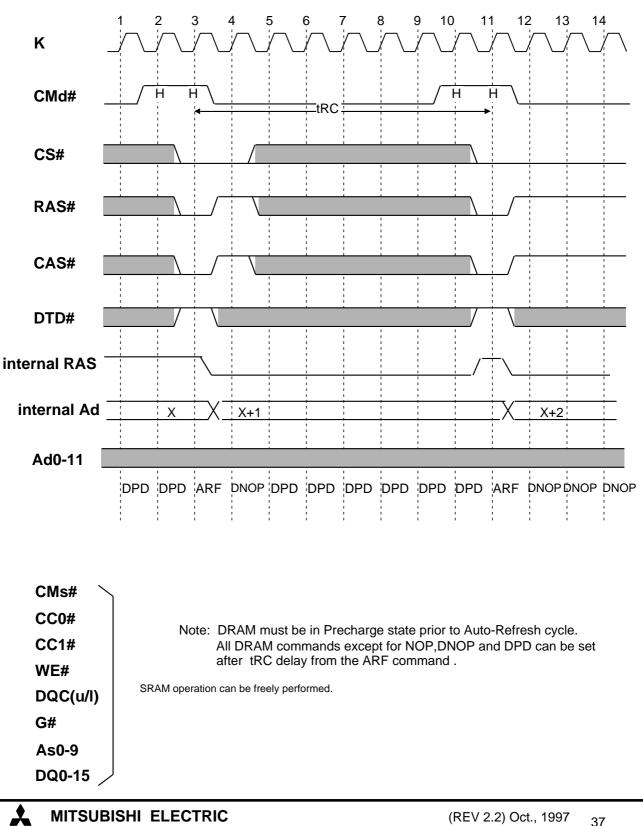

| DRAM<br>Auto-Refresh       | Internally, a DRAM row is selected and refreshed (as addressed by an internal, self-<br>incrementing counter), followed by an internally generated Precharge cycle. The Auto refresh<br>cycle can be implemented only if the DRAM is in Precharge state (i.e., a Precharge or Auto-<br>Refresh cycle occurred more recently than an Acitvate cycle). After an Auto refresh cycle the<br>DRAM is in left in a Precharged state. DRAM Auto-Refresh is similar to a CAS-Before-RAS<br>(CBR) mode in standard DRAMs.                                                                                                                                                                                                                                                             |

| DRAM<br>Self Refresh       | All clock buffers are suspended, and CMd# asynchronously controls Self Refresh (CMd# rising edge initiates exit from Self Refresh). During Self Refresh, device enters a low power mode, the DRAM is automatically refreshed during this mode. A DNOP must be performed after exiting Self Refresh mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

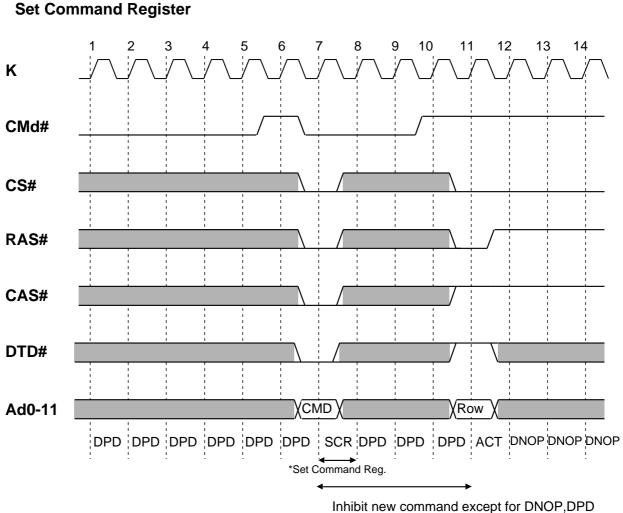

| Set<br>Command<br>Register | When SCR is initiated,the addresses present on the Ad0-Ad11 DRAM Address pins determine<br>the DRAM Read/Write Transfer Latency, the Output Mode (transparent / latched / registered),<br>and WB1 transfer mask mode (set-all/ no change). No DRAM operation is executed in this<br>cycle. Refer to the SCR truth table for legal address values.<br>During SCR cycle and the following 3 clock cycles(totally 4 clock cycles), only NOP,DNOP or<br>DPD are allowed in DRAM portion and only NOP,DES or SPD are done in SRAM portion. The<br>set commands are valid at least after the above 4 clocks later and the previous function is not<br>guaranteed to work if it has not been completed.(i.e. DRT ,DWT1&R,DWT2&R and SR,BR and<br>BRTR with registered output mode.) |

Notes:

1) This function is performed in a latency period specified in the access latency table.

2) After the latency period (specified in the access latency table) new data will be present

in the read buffers. Prior to the latency timeout, old data will be present in RB1/RB2.

3) After data has been transferred from WB1, the entire WB1 mask is set.

4) Valid Ad0-Ad2 addresses are shown in the FUNCTION TRUTH TABLE.

## Power-On sequence

Before starting normal operation, the following power on sequence is necessary.

1) Apply power and maintain stable power (pause) for 500us. When power is applied the DQ pins assume a Hi-Z state and remainin this condition until an SRAM or Buffer read operation is performed.

2) Perform a precharge (PCG) operation.

3) After tRP, perform 8 auto refresh commands (ARF) with adequate interval (tRC).

4) Issue concurrent set command register (SCR) and deselect (DES) to initilize the mode register.

After this sequence, the RAM is in idle state and ready for normal operation. Note that DNOP / DPD and DES / SPD or NOP command will be the stand-by command for the above power sequence.

### **Output Operations**

#### **Transparent**

#### Latched

### **Registered**

## M5M4V16169TP-10,-12,-15

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

A MITSUBISHI ELECTRIC

(REV 2.2) Oct., 1997 19

#### ABSOLUTE MAXIMUM RATINGS

| Symbol | Parameter             | Conditions          | Ratings    | Unit |

|--------|-----------------------|---------------------|------------|------|

| Vdd    | Supply Voltage        | With respect to Vss | -0.5 ~ 4.6 | V    |

| VI     | Input Voltage         |                     | -0.5 ~ 4.6 | V    |

| Vo     | Output Voltage        |                     | -0.5 ~ 4.6 | V    |

| IO     | Output Current        |                     | 50         | mA   |

| Pd     | Power Dissipation     |                     | 1000       | mW   |

| Topr   | Operating Temperature |                     | 0~70       | °C   |

| Tstg   | Storage Temperature   |                     | -65 ~ 150  | °C   |

#### **RECOMMENDED OPERATING CONDITIONS**

(Ta=0 ~ 70°C, unless otherwise noted)

| Symbol       | Parameter                               | Limits        |     |         | Unit |

|--------------|-----------------------------------------|---------------|-----|---------|------|

|              |                                         | Min. Typ. Max |     |         |      |

| Vdd          | Supply Voltage                          | 3.0           | 3.3 | 3.6     | V    |

| Vss          | Supply Voltage                          | 0             | 0   | 0       | V    |

| Vih(A)       | High-level Input Voltage address inputs | 2.0           |     | Vdd+0.3 | V    |

| <b>Ин(с)</b> | High-level Input Voltage clock inputs   | 2.0           |     | Vdd+0.3 | V    |

| Vih(dq)      | High-level Input Voltage DQ inputs      | 2.0           |     | 3.6     | V    |

| ЧL           | Low-level Input Voltage all inputs      | -0.3          |     | 0.8     | V    |

## CAPACITANCE

(Ta=0~70°C, Vdd=3.3±0.3V for -12 and -15, Vdd=3.3V±0.15V for -10 Vss=0V, unless otherwise noted)

| Symbol | Parameter                      | Test Condition | Limits (MAX) | Unit |

|--------|--------------------------------|----------------|--------------|------|

| CI(A)  | Input Capacitance, Address pin | VI=Vss         | 5            | рF   |

| CI(C)  | Input Capacitance, Clock pin   | f=1MHz         | 7            | рF   |

| CI/O   | Input Capacitance, I/O pin     | VI=25mVrms     | 8            | рF   |

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

#### AVERAGE SUPPLY CURRENT from Vcc

(Ta=0~70°C, Vdd=3.3±0.3V for -12 and -15, Vdd=3.3V±0.15V for -10 Vss=0V, unless otherwise noted)

| Symbol    | Condition                                                                                              |     | Limits (N | 1AX) | Unit |

|-----------|--------------------------------------------------------------------------------------------------------|-----|-----------|------|------|

| Cynibol   | Conduction                                                                                             | -10 | -12       | -15  | •••• |

| IccS      | Average supply current of SRAM operating, tK=min.<br>DRAM=DPD output open data input=H or L            | 300 | 260       | 230  | mA   |

| IccD      | Average supply current of DRAM operating, tRC=min.<br>SRAM=SPD                                         | 140 | 120       | 100  | mA   |

| IccD(PG)  | Average supply current of DRAM page-mode tPC=min. SRAM=SPD                                             | 180 | 150       | 120  | mA   |

| Icc(STN1) | LVTTL standby, tK=min, DRAM=DNOP & SRAM=DES,<br>or NOP all input=stable. output open data input=H or L | 75  | 65        | 55   | mA   |

| Icc(STN2) | CMOS standby, tK=min, DRAM=DNOP & SRAM=DES,<br>or NOP all input=stable. output open data input=H or L  | 45  | 40        | 35   | mA   |

| Icc(PD)   | CMOS Power Down current, CMd#=CMs#=L,tK=min.                                                           | 5   | 5         | 5    | mA   |

| Icc(SRF)  | CMOS Self Refresh current, CMd#=CMs#=L,tK=                                                             | 1   | 1         | 1    | mA   |

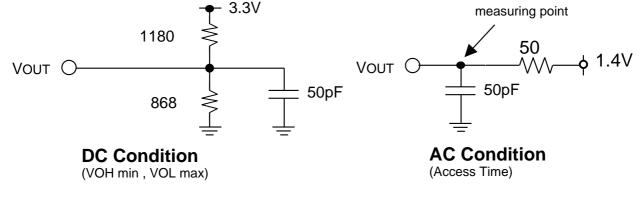

#### AC OPERATING CONDITIONS AND CHARACTERISTICS

(Ta=0~70°C, Vdd=3.3±0.3V for -12 and -15, Vdd=3.3V±0.15V for -10 Vss=0V, unless otherwise noted)

| Symbol   | Parameter                      | Test Condition         | Limits  |         | Unit |

|----------|--------------------------------|------------------------|---------|---------|------|

|          |                                |                        | Min.    | Max     |      |

| VOH(DC)* | High-level Output Voltage (DC) | IOH= –2mA              | 2.4     | -       | V    |

| VOL(DC)* | Low-level Output Voltage (DC)  | IOL= +2mA              | -       | 0.4     | V    |

| VOH(AC)* | High-level Output Voltage (AC) | 50 serial termination  | 1/2 Vcc | -       | V    |

| VOL(AC)* | Low-level Output Voltage (AC)  | 50 serial termination  | -       | 1/2 Vcc | V    |

| loz      | Off-state Output Current       | Q floating VO=0 ~ VddQ | -10     | 10      | μA   |

| ll       | Input Current                  | VIH=0 ~VddQ+0.3V       | -10     | 10      | μA   |

$^{\ast}$  VOH(AC) and VOL(AC) are the reference levels for AC measurements.

VOH(DC) and VOL(DC) are the final levels the outputs reach.

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

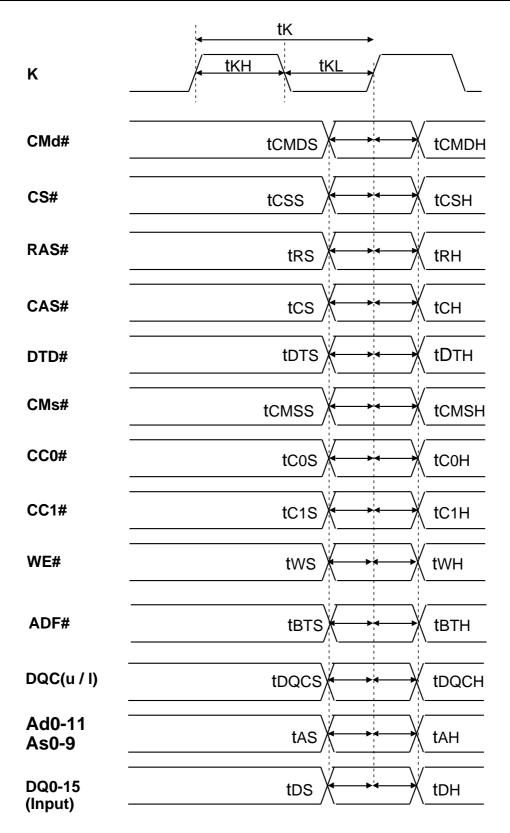

### **<u>TIMING REQUIREMENTS</u>** (CLK pulse, input signals setup / hold time to CLK edge)

(Ta=0~70°C, Vdd=3.3±0.3V for -12 and -15, Vdd=3.3V±0.15V for -10 Vss=0V, unless otherwise noted)

Input Pulse Levels:

0 to 3.0V

2ns

Input Timing Measurement Reference Level: 1.5V

Input Rise/Fall Time:

|         |                        | Limits |     |      |     |      |     |        |  |

|---------|------------------------|--------|-----|------|-----|------|-----|--------|--|

| Symbol  | Parameter              | -1     | 0   | -1   | 2   | -15  |     | — Unit |  |

|         |                        | Min.   | Max | Min. | Max | Min. | Max |        |  |

| tK      | Clock Cycle Time       | 10     |     | 12   |     | 15   |     | ns     |  |

| tKH     | Clock High Pulse Width | 4      |     | 4    |     | 4    |     | ns     |  |

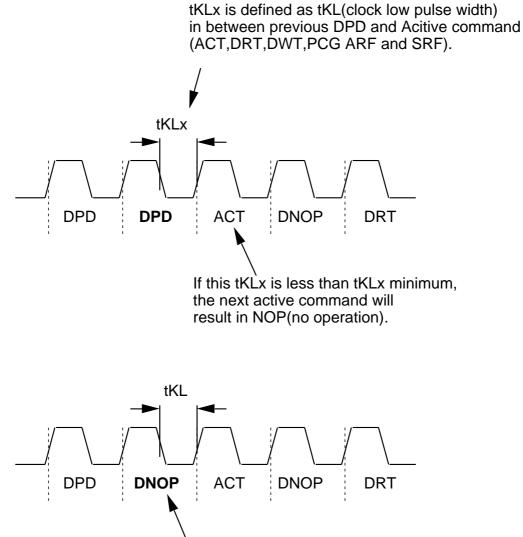

| tKL*    | Clock Low Pulse Width  | 4      |     | 4    |     | 4    |     | ns     |  |

| tCMDS   | Setup Time for CMd#    | 4      |     | 4    |     | 4    |     | ns     |  |

| tCMDH** | Hold Time for CMd#     | 1      |     | 1    |     | 1    |     | ns     |  |

| tRS     | Setup Time for RAS#    | 4      |     | 4    |     | 4    |     | ns     |  |

| tRH**   | Hold Time for RAS#     | 1      |     | 1    |     | 1    |     | ns     |  |

| tCS     | Setup Time for CAS#    | 4      |     | 4    |     | 4    |     | ns     |  |

| tCH**   | Hold Time for CAS#     | 1      |     | 1    |     | 1    |     | ns     |  |

| tDTS    | Setup Time for DTD#    | 4      |     | 4    |     | 4    |     | ns     |  |

| tDTH**  | Hold Time for DTD#     | 1      |     | 1    |     | 1    |     | ns     |  |

| tCMSS   | Setup Time for CMs#    | 4      |     | 4    |     | 4    |     | ns     |  |

| tCMSH** | Hold Time for CMs#     | 1      |     | 1    |     | 1    |     | ns     |  |

| tWS     | Setup Time for WE#     | 4      |     | 4    |     | 4    |     | ns     |  |

| tWH**   | Hold Time for WE#      | 1      |     | 1    |     | 1    |     | ns     |  |

| tC0S    | Setup Time for CC0#    | 4      |     | 4    |     | 4    |     | ns     |  |

| tC0H**  | Hold Time for CC0#     | 1      |     | 1    |     | 1    |     | ns     |  |

| tC1S    | Setup Time for CC1#    | 4      |     | 4    |     | 4    |     | ns     |  |

| tC1H**  | Hold Time for CC1#     | 1      |     | 1    |     | 1    |     | ns     |  |

| tAS     | Setup Time for Address | 4      |     | 4    |     | 4    |     | ns     |  |

| tAH**   | Hold Time for Address  | 1      |     | 1    |     | 1    |     | ns     |  |

| tDS     | Setup Time for DIN     | 4      |     | 4    |     | 4    |     | ns     |  |

| tDH**   | Hold Time for DIN      | 1      |     | 1    |     | 1    |     | ns     |  |

| tDQCS   | Setup Time for DQC     | 4      |     | 4    |     | 4    |     | ns     |  |

| tDQCH** | Hold Time for DQC      | 1      |     | 1    |     | 1    |     | ns     |  |

| tCSS    | Setup Time for CS#     | 4      |     | 4    |     | 4    |     | ns     |  |

| tCSH**  | Hold Time for CS#      | 1      |     | 1    |     | 1    |     | ns     |  |

\*Note:Please refer to next page.

\*\*Note:tH min. of 1.0ns is guaranteed at 3.0V to 3.45V. Otherwise 2.0ns. (3.0V to 3.6V)

\*Note : tKLx between previous DPD and Acitive command(ACT,DRT,DWT,PCG ARF and SRF) is 7.0ns minimum, otherwise it is 4.0ns minimum. If this tKLx is less than tKLx minimum, the next active command will result in NOP(no operation).

To avoid tKLx restriction, use DNOP instead of DPD.

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

#### TIMING REQUIREMENTS (Read, Write, Refresh)

(Ta=0~70°C, Vdd=3.3±0.3V for -12 and -15, Vdd=3.3V±0.15V for -10 Vss=0V, unless otherwise noted)

| Input Pulse Levels:                       | 0 to 3.0V |

|-------------------------------------------|-----------|

| Input Timing Measurement Reference Level: | 1.5V      |

| Input Rise/Fall Time:                     | 2ns       |

|        |                                   | Limits |         |      |         |      |         |        |  |

|--------|-----------------------------------|--------|---------|------|---------|------|---------|--------|--|

| Symbol | Parameter                         | -10    |         | -12  |         | -15  |         | - Unit |  |

| -      |                                   | Min.   | Max     | Min. | Max     | Min. | Max     |        |  |

| tREF   | Refresh Cycle Time                |        | 64      |      | 64      |      | 64      | ms     |  |

| tRP    | Precharge Time                    | 30     |         | 36   |         | 40   |         | ns     |  |

| tRCD   | Delay Time, Add Strb. Row to Col. | 24     |         | 24   |         | 30   |         | ns     |  |

| tRC*   | DRAM Activate-Read Cycle Time     | 80     |         | 96   |         | 120  |         | ns     |  |

| tWC*   | DRAM Activate-Write Cycle Time    | 80     |         | 96   |         | 120  |         | ns     |  |

| tPC    | Page Cycle Time                   | 20     |         | 24   |         | 30   |         | ns     |  |

| tRAS   | Activate Time                     | 50     | 10,000  | 60   | 10,000  | 70   | 10,000  | ns     |  |

| tRASP  | Page mode Activate Time           | 50     | 100,000 | 60   | 100,000 | 70   | 100,000 | ns     |  |

| tRWL   | Write to Precharge Lead Time      | 15     |         | 15   |         | 15   |         | ns     |  |

| tRSH   | Read to Precharge Hold Time       | 10     |         | 12   |         | 15   |         | ns     |  |

\*Note: When tRP and tRAS = Min. values, tRC and tWC = tRP + tRAS.

#### TIMING PARAMETER-CLK TABLE

| Version | -10  |       |      |       | -12  |       |      |       | -15  |       |      |       |

|---------|------|-------|------|-------|------|-------|------|-------|------|-------|------|-------|

| Freq.   | 100  | 0.0   | 50.  | 0     | 83.  | 3     | 41.7 |       | 66.6 |       | 33.3 |       |

| (MHz)   | Min. | Max   |

| tREF    |      | 6.40M |      | 3.20M |      | 5.33M |      | 2.67M |      | 4.27M |      | 2.13M |

| tRP     | 3    |       | 2    |       | 3    |       | 2    |       | 3    |       | 2    |       |

| tRCD    | 3    |       | 2    |       | 2    |       | 1    |       | 2    |       | 1    |       |

| tRC     | 8    |       | 5    |       | 8    |       | 5    |       | 8    |       | 4    |       |

| tWC     | 8    |       | 5    |       | 8    |       | 5    |       | 8    |       | 4    |       |

| tPC     | 2    |       | 1    |       | 2    |       | 1    |       | 2    |       | 1    |       |

| tRAS    | 5    | 1000  | 3    | 500   | 5    | 833   | 3    | 417   | 5    | 667   | 3    | 333   |

| tRASP   | 5    | 10000 | 3    | 5000  | 5    | 8333  | 3    | 4167  | 5    | 6667  | 3    | 3333  |

| tRWL    | 2    |       | 1    |       | 2    |       | 1    |       | 1    |       | 1    |       |

| tRSH    | 1    |       | 1    |       | 1    |       | 1    |       | 1    |       | 1    |       |

Note: Value of K can be determined by integer (timing parameter/tCLK) for any clock frequency.

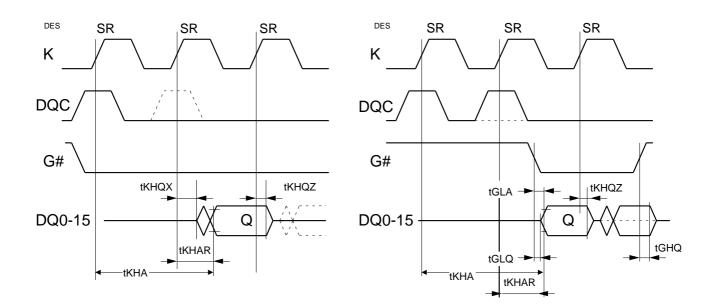

## SWITCHING CHARACTERISTICS

(Ta=0~70°C, Vdd=3.3 $\pm$ 0.3V for -12 and -15, Vdd=3.3V $\pm$ 0.15V for -10 Vss=0V, unless otherwise noted)

|        |                                       |      |     | Li   | mits |      |     | Unit |

|--------|---------------------------------------|------|-----|------|------|------|-----|------|

| Symbol | Parameter                             | -1   | 0   |      | 12   | -15  |     |      |

|        |                                       | Min. | Max | Min. | Max  | Min. | Max |      |

| tCBF   | Buffer-Fill from DRAM Read Transfer   |      | 20  |      | 20   |      | 20  | ns   |

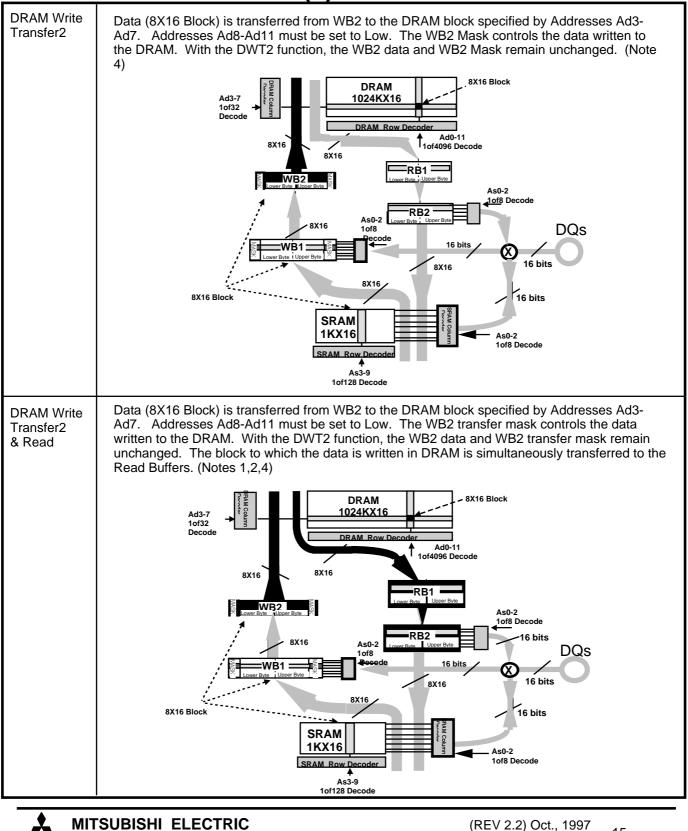

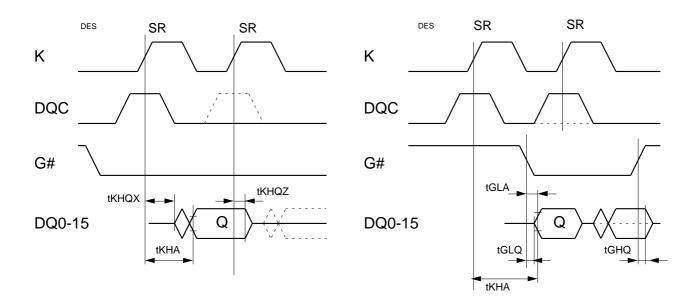

| tKHA   | Access Time from K-High Edge          |      | 10  |      | 11   |      | 12  | ns   |

| tKHQX  | Output Active Time from K-High Edge   | 2    |     | 2    |      | 3    |     | ns   |

| tKHQZ  | Output Disable Time from K-High Edge  | 2    | 8   | 2    | 8    | 3    | 8   | ns   |

| tKLA   | Access Time from K-Low Edge           |      | 10  |      | 11   |      | 12  | ns   |

| tKLQX  | Output Active Time from K-Low Edge    | 2    |     | 2    |      | 3    |     | ns   |

| tKLQZ  | Output Disable Time from K-Low Edge   | 2    | 8   | 2    | 8    | 3    | 8   | ns   |

| tKHAR  | Access Time from K-High Edge          |      | 7   |      | 7.5  |      | 8   | ns   |

| tKHQXR | Output Active Time from K-High Edge   | 2    |     | 2    |      | 3    |     | ns   |

| tKHQZR | Output Disable Time from K-High Edge  | 2    | 8   | 2    | 8    | 3    | 8   | ns   |

| tGLA   | Access Time from G#-Low Edge          |      | 7   |      | 7.5  |      | 8   | ns   |

| tGLQ   | Output Active Time from G#-Low Edge   | 2    |     | 2    |      | 3    |     | ns   |

| tGHQ   | Output Disable Time from G#-High Edge | 2    | 7   | 2    | 7    | 3    | 7   | ns   |

## **ACCESS LATENCY (Minimum)**

#### TIMING PARAMETER-CLK TABLE

| Version | n -10 -12 |      |      | -15  |      |      |

|---------|-----------|------|------|------|------|------|

| Freq.   | 100.0     | 50.0 | 83.3 | 41.7 | 66.6 | 33.3 |

| (MHz)   | Max       | Max  | Max  | Max  | Max  | Max  |

| tRAC*   | 6         | 4    | 5    | 3    | 5    | 3    |

| tCAC**  | 3         | 2    | 3    | 2    | 3    | 2    |

| tRCD    | 3         | 2    | 2    | 1    | 2    | 1    |

| tCBF    | 2         | 1    | 2    | 1    | 2    | 1    |

| tKHA    | 1         | 1    | 1    | 1    | 1    | 1    |

| tKLA    | 1         | 1    | 1    | 1    | 1    | 1    |

| tKHAR   | 1         | 1    | 1    | 1    | 1    | 1    |

| tGLA    | 1         | 1    | 1    | 1    | 1    | 1    |

tRAC\* =tRCD+tCBF+tKHA

tCAC\*\*=tCBF+tKHA

Note: Value of K can be determined by integer (timing parameter/tCLK) for any clock frequency.

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

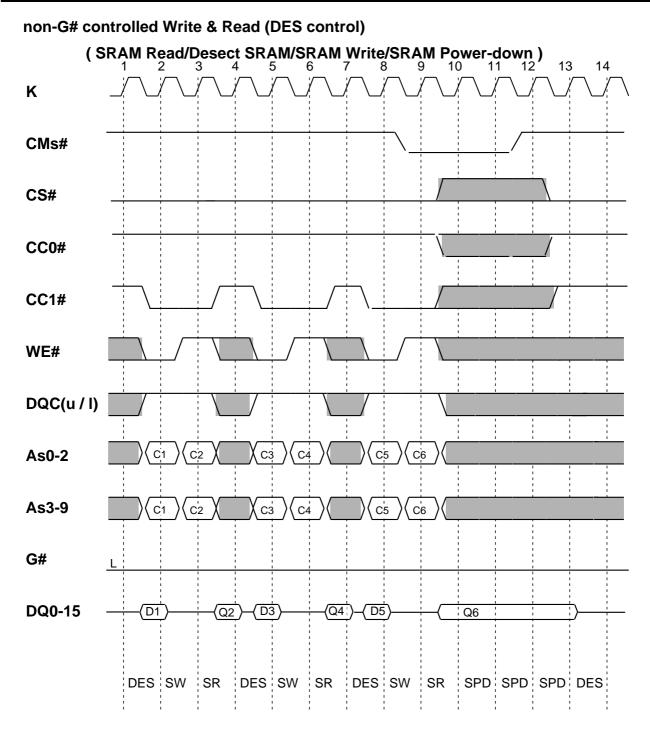

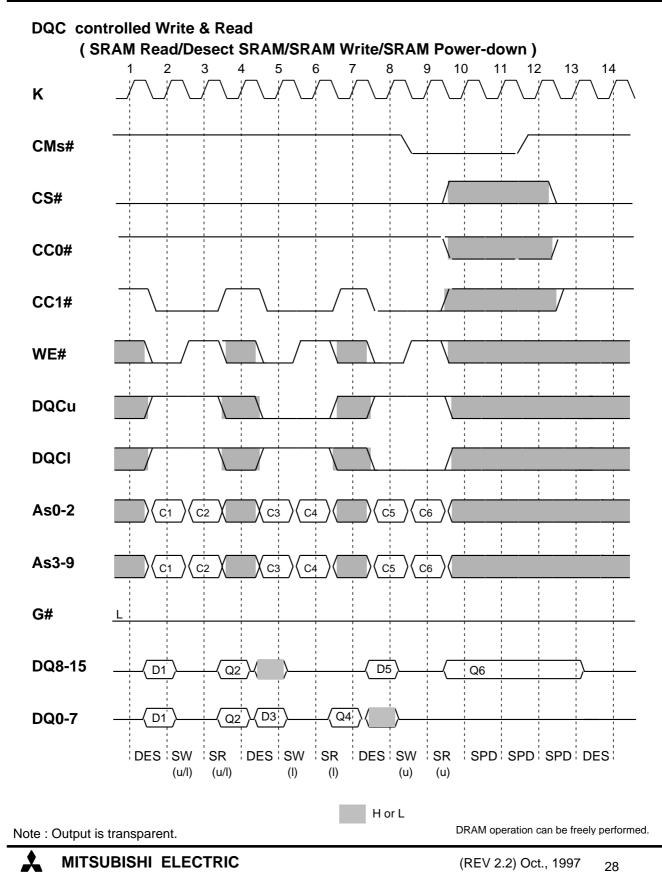

Note : Output is transparent.

DRAM operation can be freely performed.

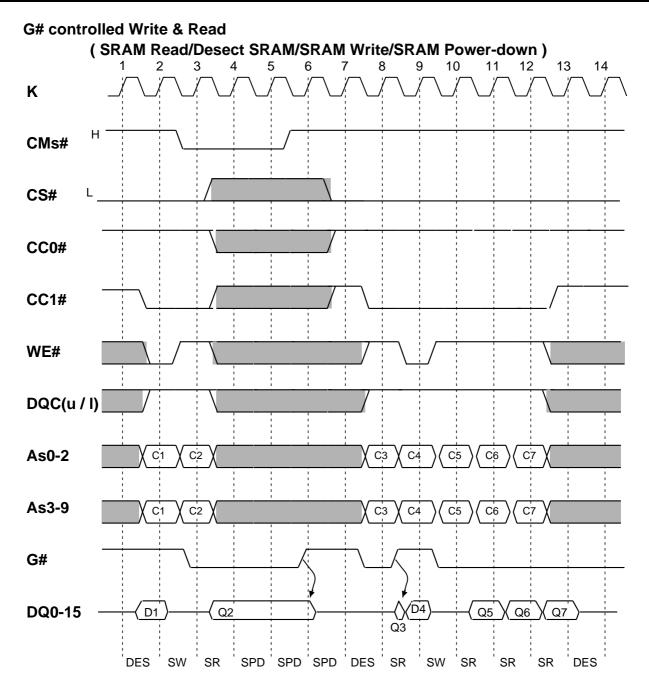

Note : Output is transparent.

DRAM operation can be freely performed.

## M5M4V16169TP-10,-12,-15

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

## M5M4V16169TP-10,-12,-15

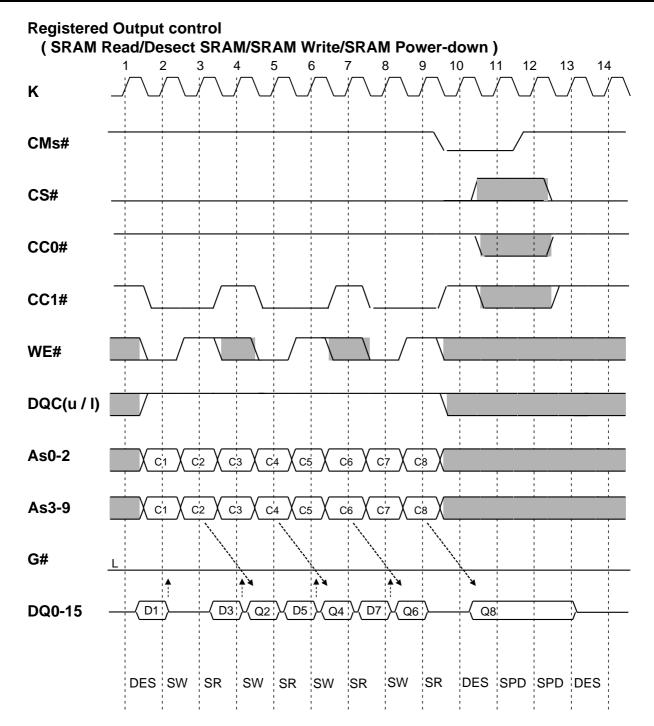

Note : Output is registered. DRAM operation can be freely performed.

MITSUBISHI ELECTRIC

## M5M4V16169TP-10,-12,-15

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

Note : Output is transparent. DRAM operation can be freely performed.

**MITSUBISHI ELECTRIC**

(REV 2.2) Oct., 1997 30

## M5M4V16169TP-10,-12,-15

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

Note : Output is transparent. DRAM operation can be freely performed.

M5M4V16169TP-10,-12,-15 16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

Note : Output is transparent.

DRAM operation can be freely performed.

**MITSUBISHI ELECTRIC**

**MITSUBISHI LSIs**

M5M4V16169TP-10,-12,-15

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

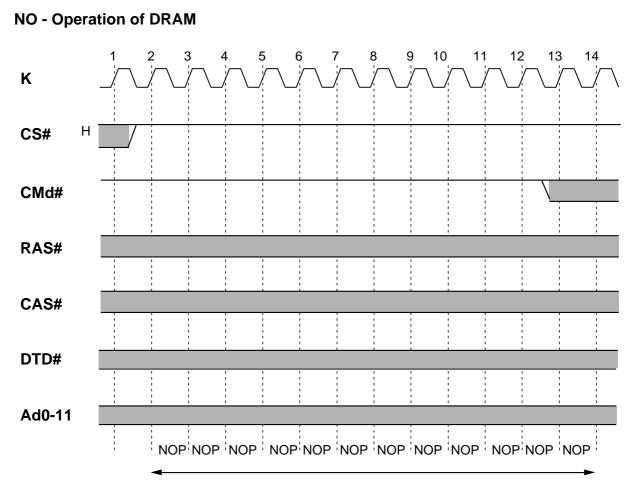

## **NO - Operation of SRAM** 9 10 11 12 13 14 2 3 6 7 8 5 Κ CMs# Н CS# **CC0# CC1#** WE# DQC(U/I) AS0-9

NO-Operation Mode

DPD operation can be freely performed.

🙏 MITSUBISHI ELECTRIC

NO-Operation Mode

SPD operation can be freely performed.

**MITSUBISHI LSIs**

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

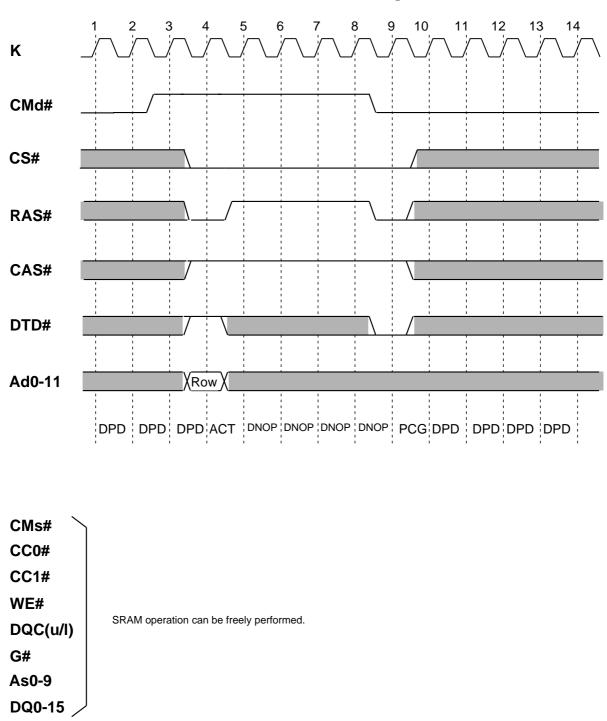

DRAM Power Down / DRAM Activate / DRAM Precharge

DPD is recommended during no operation to save power.

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

MITSUBISHI ELECTRIC

M5M4V16169TP-10,-12,-15 16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

**MITSUBISHI LSIs**

#### **DRAM Auto Refresh**

<u>Self Refresh Entry:</u> (Note: DRAM must be in Precharge state prior to Self-Refresh Entry) Previous CMd#=H, Present CMd#=L, CS#=RAS#=CAS#=L, DTD#=H (CMd# must remain low to maintain Self Refresh).

#### Self Refresh Exit (in order):

- a) resume K clock

- b) CMd#=H

- c) Wait tRC for recovery

- d) Resume normal operation

SRAM operation can be freely performed.

#### MITSUBISHI LSIs M5M4V16169TP-10,-12,-15 16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

This page intentionally left blank.

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

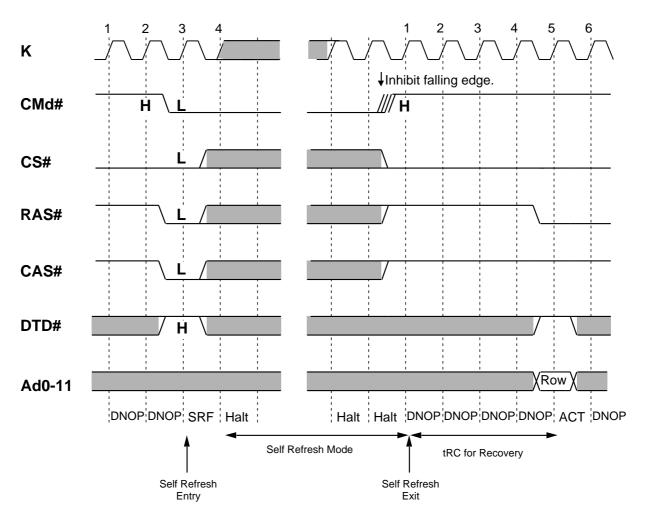

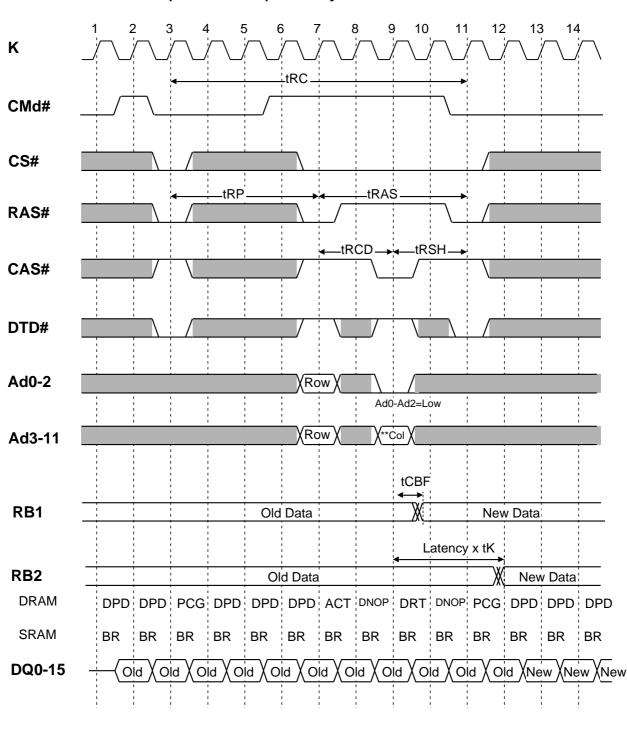

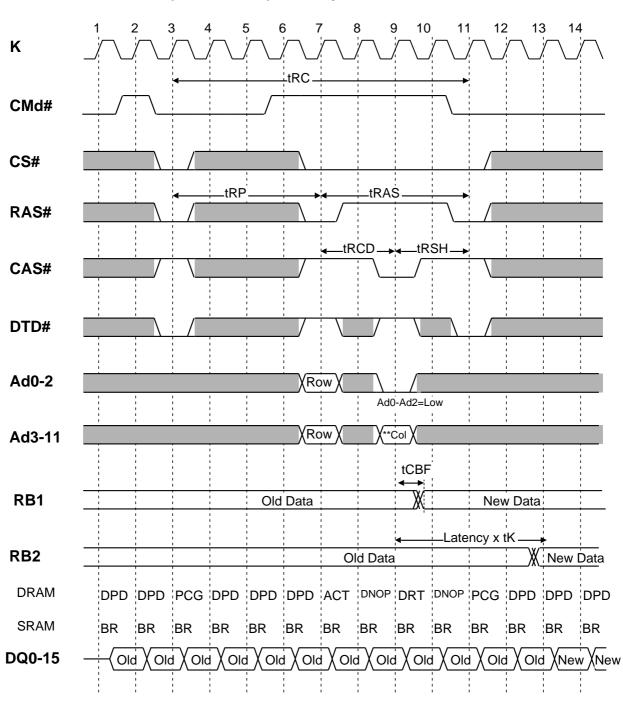

#### DRAM Read Transfer (DRAM -> RB) Latency set=1

SRAM operation can be freely performed.

\*\* Ad3-Ad7 are column block addresses (Ad8-Ad11=Low).

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

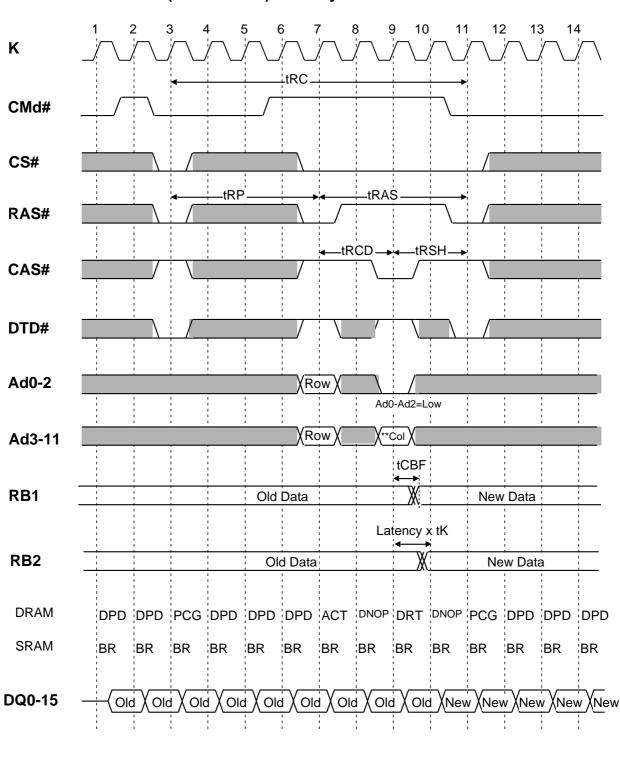

#### DRAM Read Transfer (DRAM -> RB) Latency set=2

SRAM operation can be freely performed.

\*\* Ad3-Ad7 are column block addresses (Ad8-Ad11=Low).

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

#### DRAM Read Transfer (DRAM -> RB) Latency set=3

SRAM operation can be freely performed.

\*\* Ad3-Ad7 are column block addresses (Ad8-Ad11=Low).

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

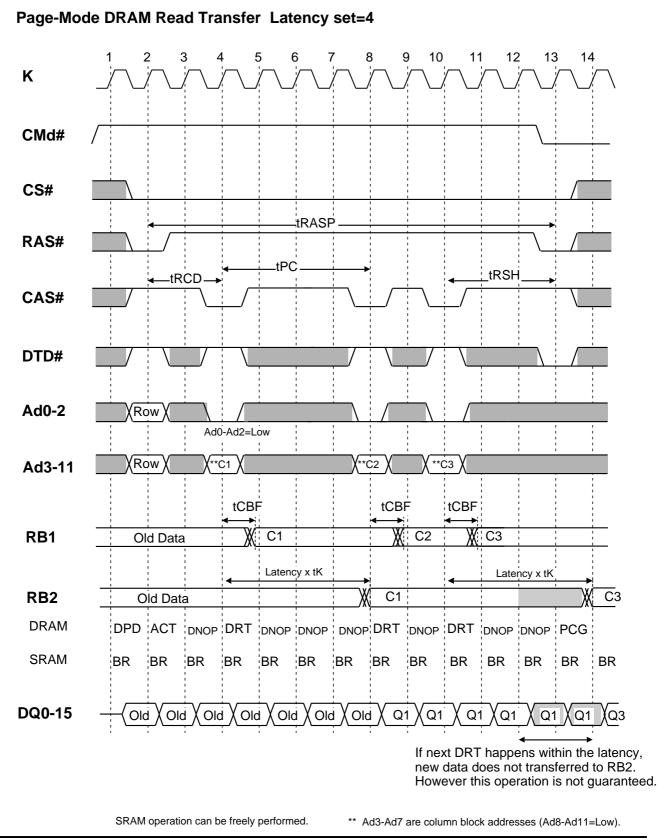

#### DRAM Read Transfer (DRAM -> RB) Latency set=4

SRAM operation can be freely performed.

\*\* Ad3-Ad7 are column block addresses (Ad8-Ad11=Low).

MITSUBISHI ELECTRIC

ᆂ

M5M4V16169TP-10,-12,-15 16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

**MITSUBISHI ELECTRIC**

(REV 2.2) Oct., 1997 44

**MITSUBISHI LSIs**

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

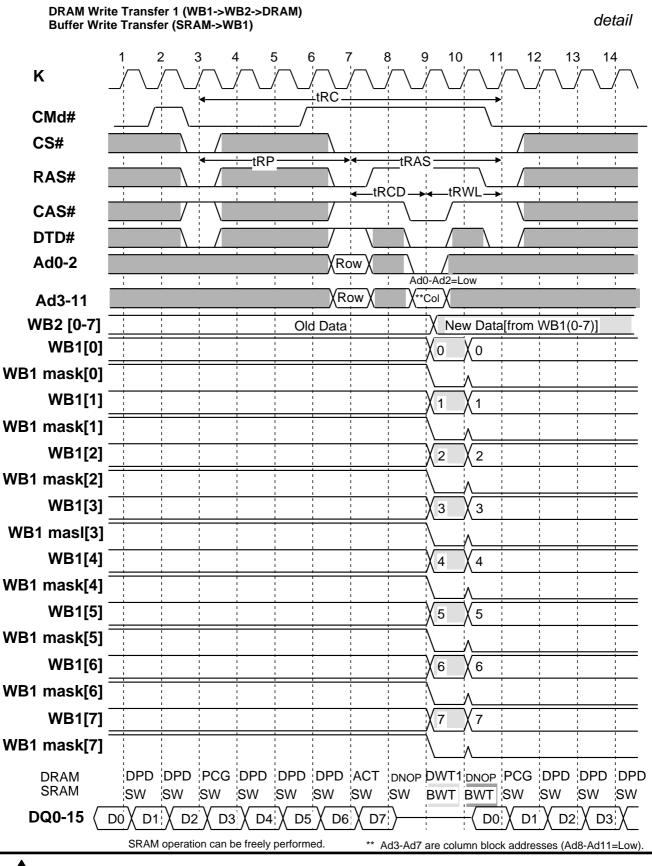

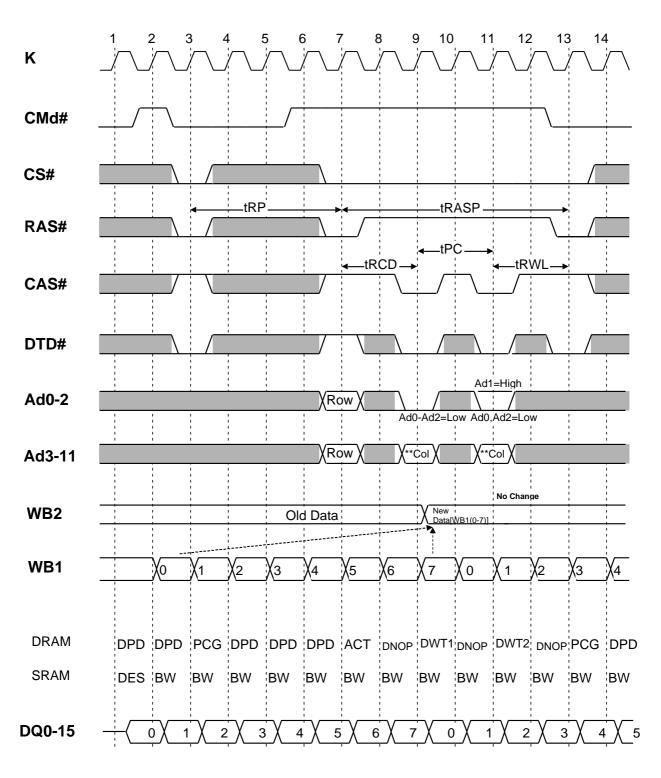

SRAM operation can be freely performed.

\*\* Ad3-Ad7 are column block addresses (Ad8-Ad11=Low).

**MITSUBISHI LSIs**

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

**MITSUBISHI LSIs**

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

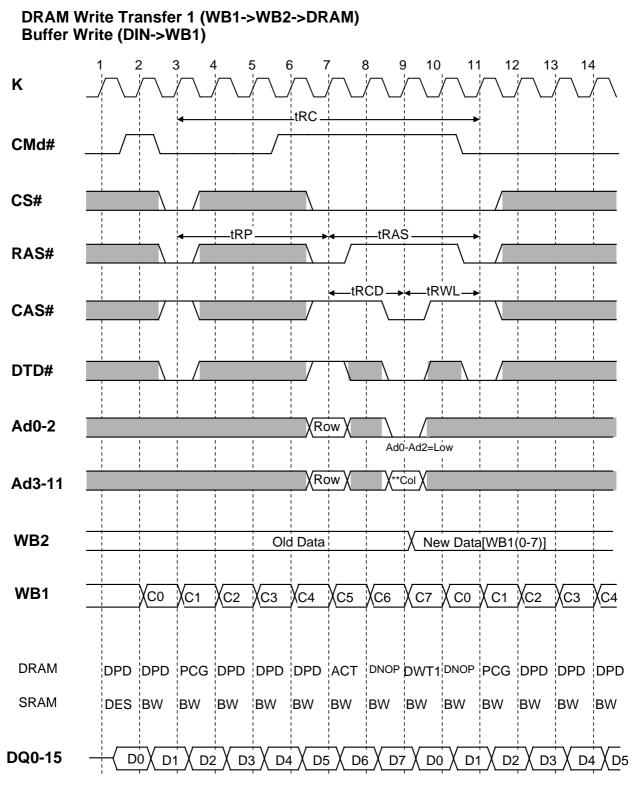

Please refer to next page in detail.

SRAM operation can be freely performed.

\*\* Ad3-Ad7 are column block addresses (Ad8-Ad11=Low).

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

### 🙏 MITSUBISHI ELECTRIC

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

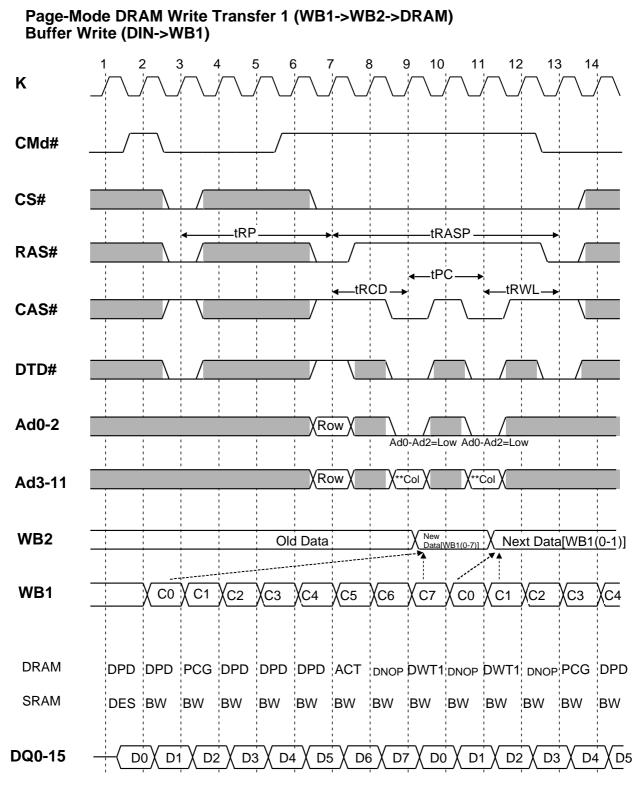

Please refer to next page in detail.

SRAM operation can be freely performed.

\*\* Ad3-Ad7 are column block addresses (Ad8-Ad11=Low).

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

🙏 MITSUBISHI ELECTRIC

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

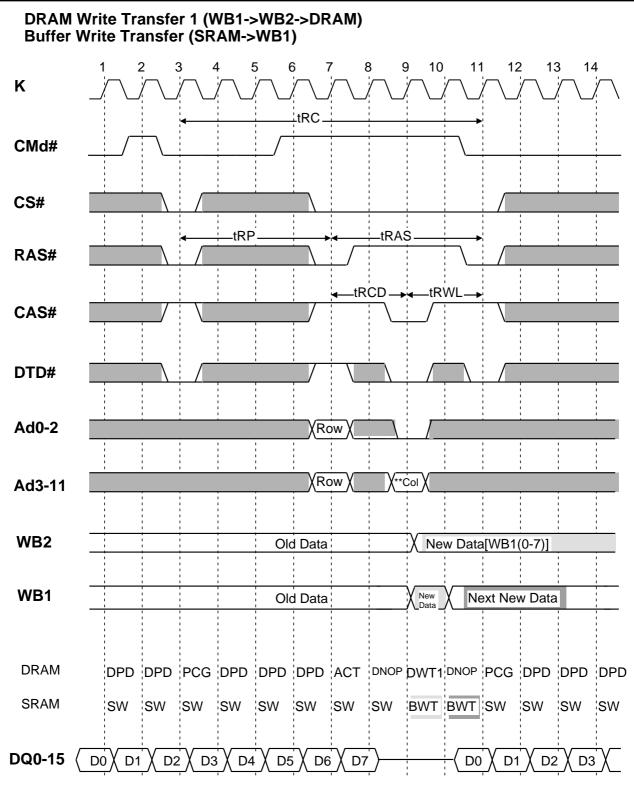

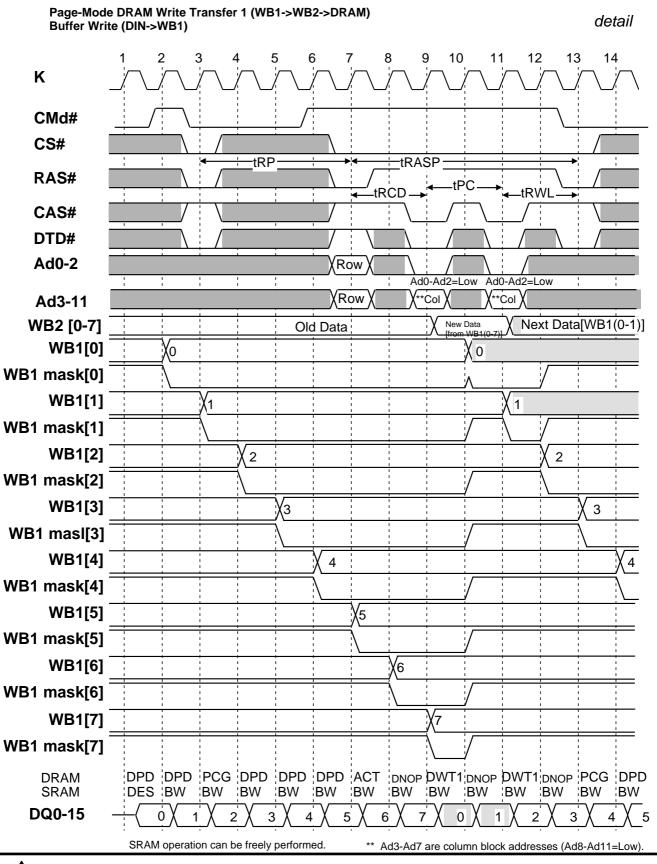

Please refer to next page in detail.

SRAM operation can be freely performed.

\*\* Ad3-Ad7 are column block addresses (Ad8-Ad11=Low).

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

🙏 MITSUBISHI ELECTRIC

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

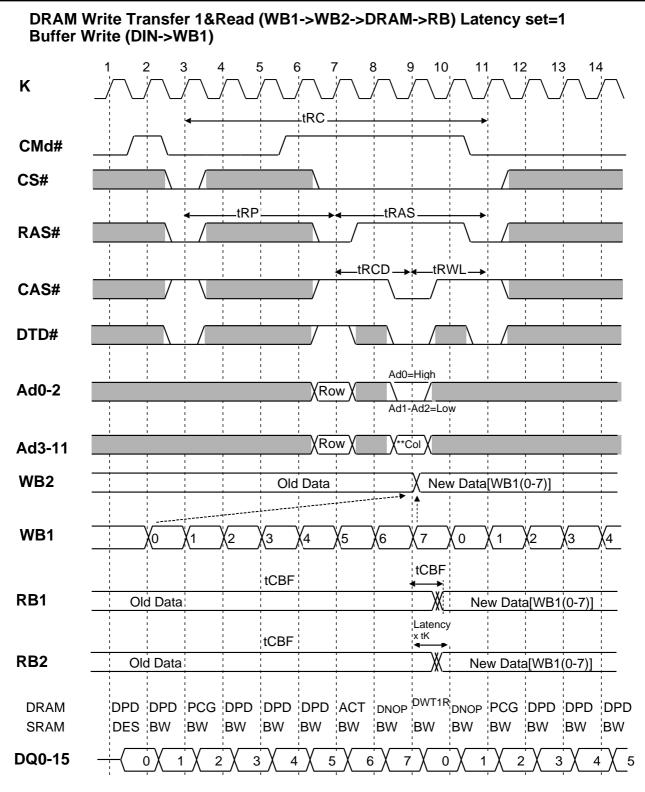

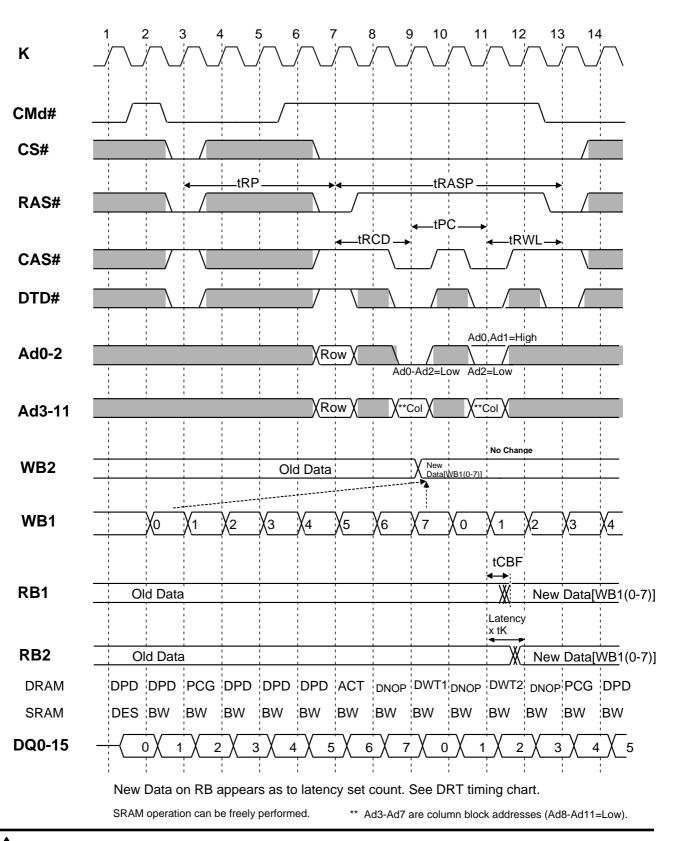

New Data on RB appears as to latency set count. See DRT timing chart.

SRAM operation can be freely performed.

\*\* Ad3-Ad7 are column block addresses (Ad8-Ad11=Low).

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

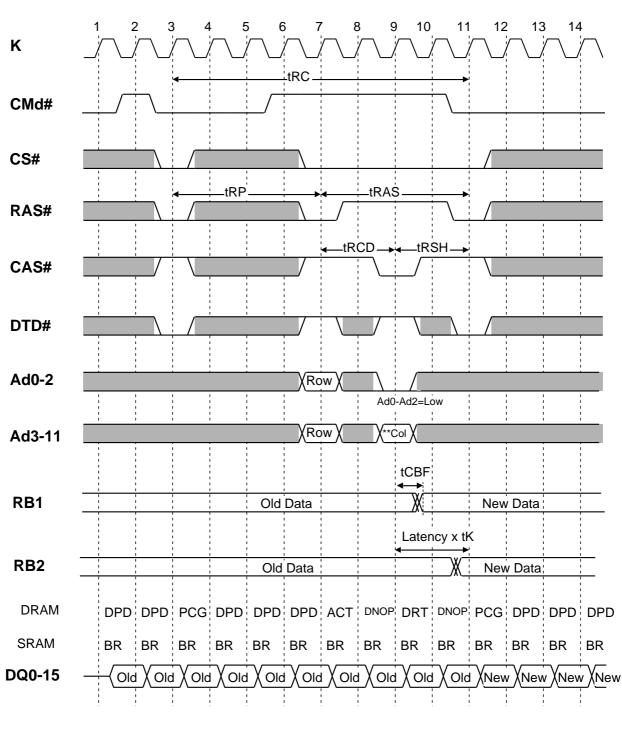

DRAM Write Transfer 2 (WB2->DRAM)

SRAM operation can be freely performed.

\*\* Ad3-Ad7 are column block addresses (Ad8-Ad11=Low).

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

DRAM Write Transfer2 & Read (WB2->DRAM->RB) Latency set=1

<sup>🙏</sup> MITSUBISHI ELECTRIC

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

This page intentionally blank.

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

DES,SPD and NOP.

$^{\ast}$  Ad0-11 must be set according to set command truth table while Ad8-Ad11=Low

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

#### Set Command Register Detailed Truth Table for SCR

| Address Input                                                                               |      |     |     |     |     |     |     |     |     |     |                                                        | Command                                                                                                                                                     |

|---------------------------------------------------------------------------------------------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ad11                                                                                        | Ad10 | Ad9 | Ad8 | Ad7 | Ad6 | Ad5 | Ad4 | Ad3 | Ad2 | Ad1 | Ad0                                                    |                                                                                                                                                             |

| L                                                                                           | Х    | Х   | Х   | Х   | L   | L   | L   | Х   | X   | L   | Х                                                      | * Latency 1                                                                                                                                                 |

| L                                                                                           | Х    | Х   | Х   | Х   | L   | L   | Н   | Х   | X   | L   | Х                                                      | 2                                                                                                                                                           |

| Г                                                                                           | Х    | Х   | Х   | X   | L   | Н   | L   | Х   | X   | L   | Х                                                      | 3                                                                                                                                                           |

| L                                                                                           | Х    | Х   | Х   | Х   | L   | Н   | Н   | Х   | X   | L   | Х                                                      | 4                                                                                                                                                           |

| L                                                                                           | Х    | Х   | Х   | Х   | Х   | Х   | X   | L   | L   | L   | Х                                                      | Output Mode<br>Transparent                                                                                                                                  |

| L                                                                                           | Х    | Х   | Х   | Х   | Х   | Х   | X   | L   | н   | L   | Х                                                      | Latched                                                                                                                                                     |

| L                                                                                           | Х    | Х   | Х   | Х   | Х   | Х   | X   | Н   | L   | L   | Х                                                      | Registered                                                                                                                                                  |

| L                                                                                           | Х    | Х   | Х   | Х   | Х   | Х   | X   | Х   | X   | L   | L                                                      | No Operation<br>of Mask                                                                                                                                     |

| L                                                                                           | Х    | Х   | Х   | Х   | Х   | Х   | X   | Х   | X   | L   | н                                                      | Set All WB1<br>Xfer Masks                                                                                                                                   |

| L                                                                                           | Х    | Х   | L   | L   | Х   | Х   | X   | Х   | X   | L   | Х                                                      | reserved                                                                                                                                                    |

| L                                                                                           | Х    | Х   | L   | Н   | Х   | Х   | X   | Х   | X   | L   | Х                                                      | reserved                                                                                                                                                    |

| L                                                                                           | Х    | Х   | Н   | L   | Х   | Х   | X   | Х   | X   | L   | Х                                                      | reserved                                                                                                                                                    |

| L                                                                                           | Х    | Х   | Н   | Н   | Х   | Х   | X   | Х   | X   | L   | Х                                                      | reserved                                                                                                                                                    |

| L                                                                                           | Х    | L   | Х   | Х   | Х   | Х   | X   | Х   | X   | L   | Х                                                      | reserved                                                                                                                                                    |

| L                                                                                           | Х    | Н   | Х   | X   | Х   | Х   | X   | Х   | X   | L   | Х                                                      | reserved                                                                                                                                                    |

| K Latency is<br>CMd# K Latency is<br>CS# CS# CS# Cycles requi<br>RAS# CAS# CAS# Cock freque |      |     |     |     |     |     |     |     |     |     | require<br>ne DRA<br>fore, it o<br>requen<br>icy) x (t | the number of clock<br>ed to transfer new dat<br>M to the Read Buffer<br>can be adjusted to the<br>acy of the system.<br>K) should meet tCBF<br>equirement. |

A MITSUBISHI ELECTRIC

16MCDRAM:16M(1024K-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

# 70P3S Package Dimension

unit:<u>mm</u> (inch)