# 256K x 32 Synchronous Graphics RAM

## Features

- Fully synchronous; all signals registered on positive edge of system clock.

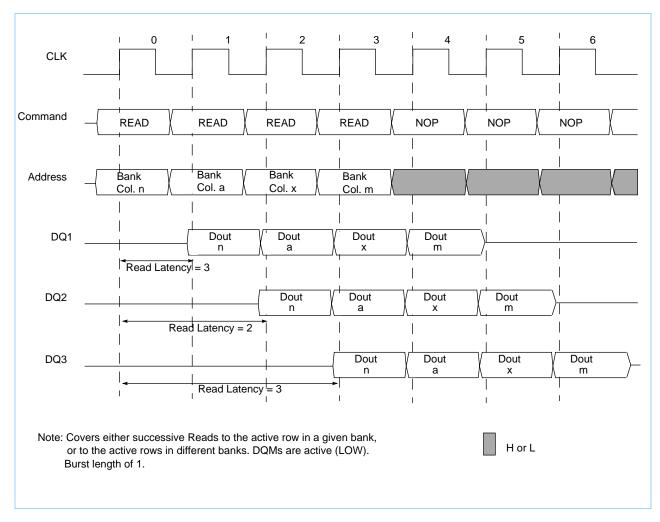

- Internal pipelined operation; column address can be changed every clock cycle.

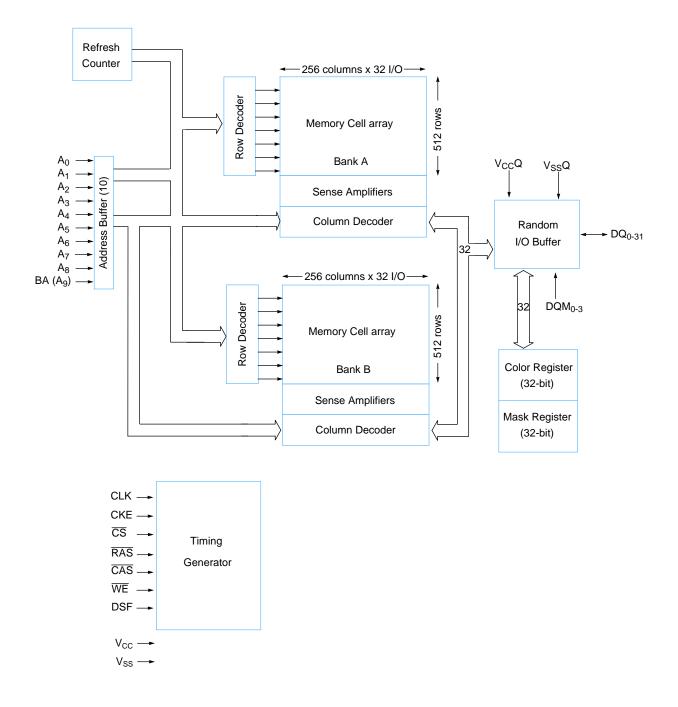

- Dual internal banks for hiding row precharge; Each bank is 128k x 32.

- Programmable burst lengths: 1, 2, 4, 8 or full page

- Burst Read with Single Write

- Programmable CAS Latency: 1, 2, 3

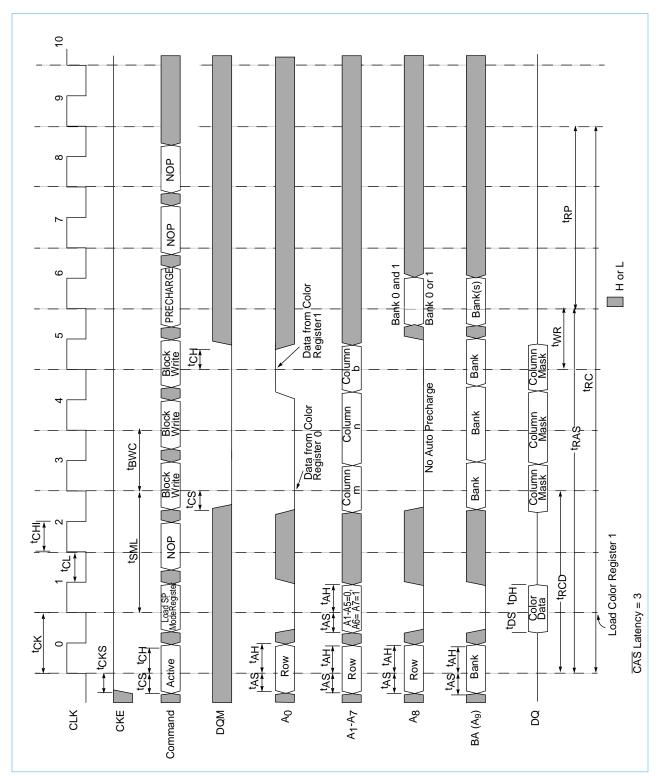

- 8 column Block Write and Write-per-Bit modes

- 100Mhz Block Write operation

- Two Color Registers

- Independent byte operation via DQM<sub>0-3</sub>

- Auto Precharge and Auto Refresh modes

- 1K Refresh cycles/16ms

- 1K Refresh cycles/128ms for Self Refresh parts

- LVTTL- compatible inputs and outputs

## Description

The IBM 256K x 32 SGRAM is a high speed 8Mb CMOS DRAM with built-in graphics features. It is internally configured as a dual bank 128K x 32 DRAM with a synchronous interface (all signals are registered on the positive edge of the clock signal CLK). Each bank is organized as a 512 rows x 256 columns x 32 bits.

Read/Write to the SGRAM are burst oriented; accesses start at a selected location and continue for a programmed number of locations. By having a Programmable Mode Register, and Load Special Mode Register the system can choose Read or Write burst lengths of 1, 2, 4, or 8 locations or the Full Page with burst termination option.

An Auto Precharge function may be enabled to provide a self-timed precharge that is initiated at the end of the burst sequence.

The SGRAM uses an internal pipelined architecture to achieve high speed operation, which also allows the column address to be changed on every clock cycle to achieve a high-speed fully random access. Precharging one bank while accessing the alternate bank will hide the precharge cycles, and provide seamless high speed random operation.

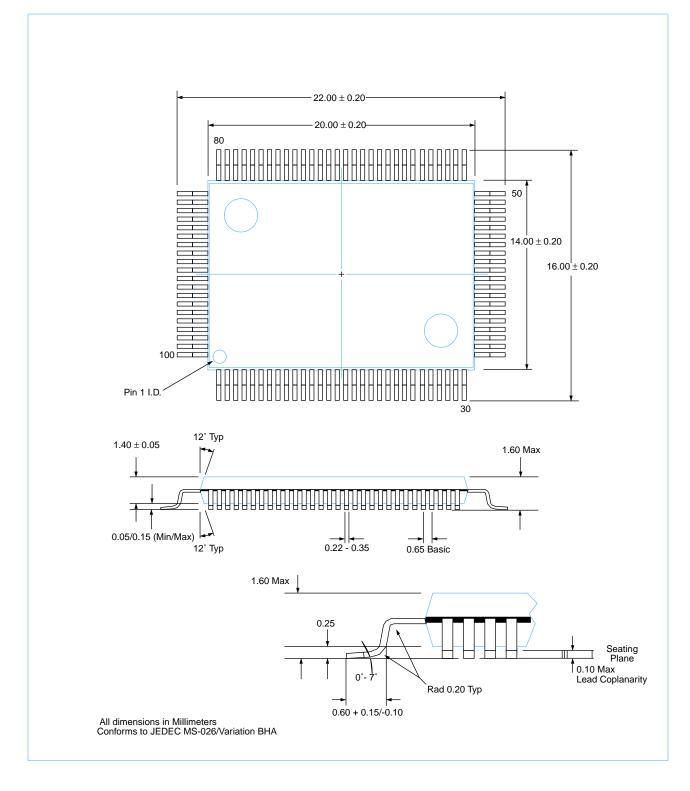

- Single  $3.3V \pm 0.3$

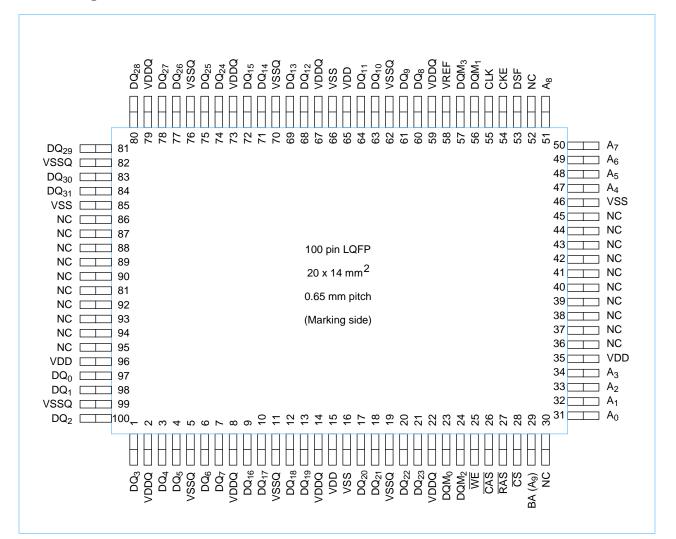

- 100-pin LQFP (0.65mm lead pitch)

| Options                                                                                                                  | Marking            |

|--------------------------------------------------------------------------------------------------------------------------|--------------------|

| Timing<br>7R5ns Access (≤ 133 Mhz clock rate)<br>10ns Access (≤ 100 Mhz clock rate)<br>12ns Access (≤ 83 Mhz clock rate) | -7R5<br>-10<br>-12 |

| Self Refresh (Special part)                                                                                              | Р                  |

| Plastic Package<br>100-pin LQFP (0.65mm lead pitch)                                                                      |                    |

# **Key Timing Parameters**

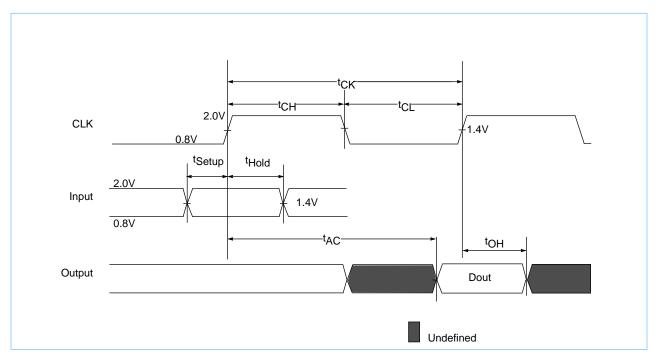

| Speed<br>Grade | Clock Frequency<br>(MHz) | Access<br>Time (ns) | Setup<br>Time (ns) | Hold<br>Time (ns) |

|----------------|--------------------------|---------------------|--------------------|-------------------|

| -7R5           | 133                      | 7                   | 2.5                | 1.0               |

| -10            | 100                      | 9                   | 3.0                | 1.0               |

| -12            | 83                       | 11                  | 3.5                | 1.5               |

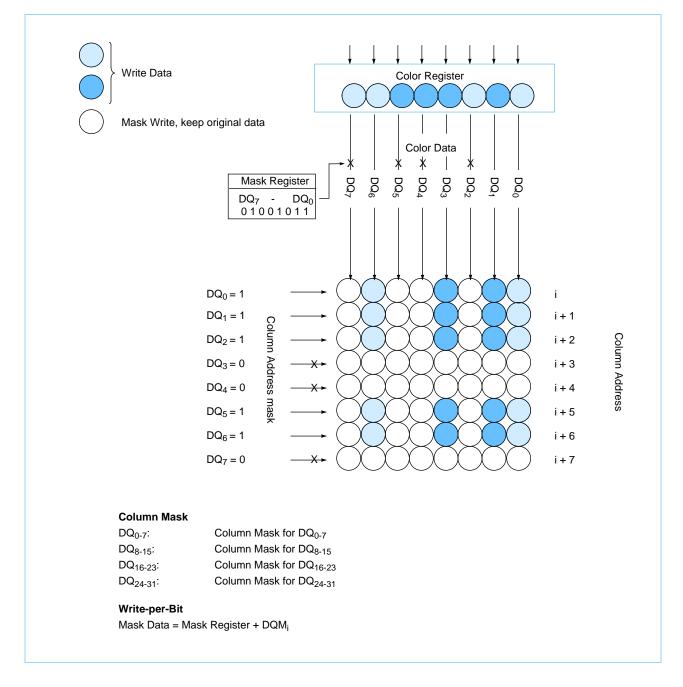

The SGRAM differs from the Synchronous DRAM (SDRAM) by providing an 8 column Block Write function and a Write-per-Bit (WPB) function. The Block Write and WPB functions may be combined with individual byte enables  $DQM_0$ - $DQM_3$ .

The part is designed to operate at 3.3V only. An Auto Refresh mode is provided along with a power saving Power Down mode. All inputs and outputs are LVTTL compatible.

## Applications

- Frame buffer for PC 2D/3D graphics applications

- One high speed device to displace two 256K x16 DRAMs at 2x performance

- High speed buffer for laser printers

- High speed buffer for RAID systems and disk drives

- Network and communication applications

- SET-TOP box application

- · Games application

- Multimedia due to multiple bank architecture

# **Ordering Information**

| Part Number                                                                                                | Features           | Speed | Voltage | Package                          | Notes |  |  |

|------------------------------------------------------------------------------------------------------------|--------------------|-------|---------|----------------------------------|-------|--|--|

| IBM038329NQ6A - 7R5                                                                                        | 133 MHz, 4BE, sync | 8     |         |                                  | 1     |  |  |

| IBM038329NQ6A - 10                                                                                         | 100 MHz, 4BE, sync | 10    |         |                                  | 1     |  |  |

| IBM038329NQ6A - 12                                                                                         | 83 MHz, 4BE, sync  | 12    | 2.01/   | 20X14 mm <sup>2</sup><br>100-pin | 1     |  |  |

| IBM038329PQ6A - 7R5                                                                                        | 133 MHz, 4BE, sync | 8     | 3.3V    | LQFP<br>(0.65min lead pitch)     | 2     |  |  |

| IBM038329PQ6A - 10                                                                                         | 100 MHz, 4BE, sync | 10    |         |                                  | 2     |  |  |

| IBM038329PQ6A - 12                                                                                         | 83 MHz, 4BE, sync  | 12    |         |                                  | 2     |  |  |

| <ol> <li>Low Power 8-Mb SGRAM parts.</li> <li>Long Retention, extra low power 8-Mb SGRAM parts.</li> </ol> |                    |       |         |                                  |       |  |  |

## **Block Diagram**

## **Pin Configurations**

| Symbol                               | Function              |

|--------------------------------------|-----------------------|

| A <sub>0</sub> -BA (A <sub>9</sub> ) | Address Inputs        |

| A <sub>0</sub> -A <sub>8</sub>       | Row Address Inputs    |

| A <sub>0</sub> -A <sub>8</sub>       | Column Address Inputs |

| BA (A <sub>9</sub> )                 | Bank Select           |

| CS                                   | Chip Select           |

| CAS                                  | Column Address Strobe |

| CKE                                  | Clock Enable          |

| CLK                                  | System Clock Input    |

| DQ <sub>0</sub> -DQ <sub>31</sub>    | Data Inputs/Outputs   |

| DQM0-DQM3                            | DQ Mask Enable        |

| Function                |

|-------------------------|

| Special Function Enable |

| No Connection           |

| Row Address Strobe      |

| Supply Voltage          |

| Supply Voltage for DQs  |

| Reference Input         |

| Ground                  |

| Ground for DQs          |

| Write Enable            |

|                         |

**Note:** A<sub>9</sub> has been renamed BA to match JEDEC 8Mb nomenclature.

# **Signal Descriptions**

| Name                                                  | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> -A <sub>8</sub> , BA (A <sub>9</sub> ) | I   | Address bits $A_0$ - $A_8$ are row addresses when Active command is activated.<br>Address bits $A_0$ - $A_7$ are column addresses when $\overrightarrow{CAS}$ is active.<br>Address bit $A_8$ , when $\overrightarrow{CAS}$ is active, enables/disables Auto Precharge.<br>Address bit BA ( $A_9$ ) selects which of the two memory banks is to be used.                                   |

| CAS                                                   | I   | CAS is part of the input command to the SGRAM. See truth table for details.                                                                                                                                                                                                                                                                                                                |

| CKE                                                   | I   | Clock Enable disables the clock internally, thus allowing data to remain on the output for several CLK cycles. Clock Enable is also used as part of the input command to specify self-refresh.                                                                                                                                                                                             |

| CLK                                                   | I   | CLK is driven by the system clock. All SGRAM input signals are sampled on the positive edge of CLK. The CLK also increments the internal burst counter and controls the output registers.                                                                                                                                                                                                  |

| <u>cs</u>                                             | I   | Chip Select indicates that the command on the input lines is for this device. If $\overline{CS}$ is high, the input command(s) will be ignored.                                                                                                                                                                                                                                            |

| DQ <sub>0</sub> -DQ <sub>31</sub>                     | I/O | Data Input/Output lines transfer data between the memory array and the system bus. These are also input mask bits for Write-per-Bit. When Block Write is activated, DQs provide column address mask.                                                                                                                                                                                       |

| DQM <sub>0</sub> -DQM <sub>3</sub>                    | I   | During Read, DQM=1 turns off the output buffers.<br>During Write, DQM=1 prevents a write to the current memory location.<br>DQM <sub>0</sub> corresponds to the lowest byte (DQ <sub>0</sub> -DQ <sub>7</sub> ).<br>DQM <sub>1</sub> corresponds to DQ <sub>8-15</sub> .<br>DQM <sub>2</sub> corresponds to DQ <sub>16-23</sub> .<br>DQM <sub>3</sub> corresponds to DQ <sub>24-31</sub> . |

| RAS                                                   | I   | RAS is part of the input command to the SGRAM. See truth table for details.                                                                                                                                                                                                                                                                                                                |

| V <sub>REF</sub>                                      | I   | Reference voltage input for SSTL operation.                                                                                                                                                                                                                                                                                                                                                |

| WE                                                    | I   | Write Enable is part of the input command. See truth table or details.                                                                                                                                                                                                                                                                                                                     |

## **Operative Command Table (Part 1 of 6)**

| Current State | $\overline{CS}$ | RAS | CAS | WE | DSF | Add        | Command    | Action                       | Notes |

|---------------|-----------------|-----|-----|----|-----|------------|------------|------------------------------|-------|

|               | н               | Х   | х   | х  | х   | Х          | INHBT      | Nop or Power Down            | 5     |

|               | L               | н   | н   | х  | х   | Х          | NOP or BST | Nop or Power Down            | 5     |

| Idle          | L               | н   | L   | н  | х   | BA, CA, AP | RD/RDA     | ILLEGAL                      | 3     |

|               | L               | н   | L   | L  | L   | BA, CA, AP | WR/WRA     | ILLEGAL                      | 3     |

|               | L               | н   | L   | L  | н   | BA, CA, AP | BW/BWA     | ILLEGAL                      |       |

|               | L               | L   | н   | н  | L   | BA, RA     | ACT        | Row Active: No I/O Mask      |       |

|               | L               | L   | н   | н  | н   | BA, RA     | ACTM       | Row Active: I/O Mask         |       |

|               | L               | L   | н   | L  | х   | BA, PA     | PRE/PREAL  | Nop                          |       |

|               | L               | L   | L   | н  | х   | Х          | REF/SREF   | Refresh or Self Refresh      | 6     |

|               | L               | L   | L   | L  | L   | Op-Code    | LMR        | Mode Register Access         |       |

|               | L               | L   | L   | L  | н   | Op-Code    | LSMR       | Special Mode Register Access |       |

|               | н               | х   | х   | х  | х   | Х          | INHBT      | Nop                          |       |

| Row Active    | L               | н   | н   | х  | х   | Х          | NOP or BST | Nop                          |       |

| NOW ACTIVE    | L               | н   | L   | н  | х   | BA, CA, AP | RD/RDA     | Begin Read: Determine AP     | 11    |

|               | L               | н   | L   | L  | L   | BA, CA, AP | WR/WRA     | Begin Write: Determine AP    | 11    |

|               | L               | н   | L   | L  | н   | BA, CA, AP | BW/BWA     | Block Write: Determine AP    |       |

|               | L               | L   | н   | н  | L   | BA, RA     | ACT        | ILLEGAL                      | 3     |

|               | L               | L   | н   | н  | н   | BA, RA     | ACTM       | ILLEGAL                      |       |

|               | L               | L   | н   | L  | х   | BA, PA     | PRE/PREAL  | Precharge                    | 8     |

|               | L               | L   | L   | н  | х   | Х          | REF/SREF   | ILLEGAL                      |       |

|               | L               | L   | L   | L  | L   | Op-Code    | LMR        | ILLEGAL                      |       |

|               | L               | L   | L   | L  | н   | Op-Code    | LSMR       | Special Mode Register Access |       |

|               |                 |     |     |    |     |            | 1          | 1                            |       |

1. H:High level, L:Low level, X:High or low level (Don't care), V:Valid data input.

2. All entries assume that CKE was active (High level) during the preceding clock cycle.

3. Illegal to bank specified states; Function may be legal in the bank indicated by Bank Address (BA), depending on the state of that bank.

4. Must satisfy bus contention, bus turn around, and/or write recovery requirements.

5. If both are idle, and CKE is inactive (Low level), the device will enter Power Down Mode. All inputs buffers except CKE will be disabled.

6. If both banks are idle, and CKE is inactive (Low level), the device will enter Self Refresh Mode. All input buffer except CKE will be disabled.

7. Illegal if  $t_{RRD}$  is not satisfied.

8. Illegal if  $t_{RAS}$  is not satisfied.

- 9. Must satisfy burst interrupt condition.

- 10. Must mask preceding data which don't satisfy t<sub>DPL</sub>.

11. Illegal if t<sub>RCD</sub> is not satisfied.

| $RA = Row Address (A_0 - A_8)$ | BA = Bank Address (BA)            | $PA = Prechare All (A_8)$   |

|--------------------------------|-----------------------------------|-----------------------------|

| NOP = No Operation Command     | $CA = Column Address (A_0 - A_7)$ | $AP = Auto Precharge (A_8)$ |

## **Operative Command Table (Part 2 of 6)**

| Current State | $\overline{\text{CS}}$ | RAS | CAS | WE | DSF | Add        | Command   | Action                                      | Notes |

|---------------|------------------------|-----|-----|----|-----|------------|-----------|---------------------------------------------|-------|

|               | н                      | Х   | х   | х  | х   | Х          | INHBT     | Continue Burst to End -> Row Active         |       |

|               | L                      | н   | н   | х  | х   | Х          | NOP       | Continue Burst to End -> Row Active         |       |

| Read          | L                      | н   | н   | L  | х   | х          | BST       | Burst Stop -> Row Active                    |       |

|               | L                      | н   | L   | н  | х   | BA, CA, AP | RD/RDA    | Term Burst, New Read: Determine AP          | 9     |

|               | L                      | н   | L   | L  | L   | BA, CA, AP | WR/WRA    | Term Burst, Start Write: Determine AP       | 4, 9  |

|               | L                      | н   | L   | L  | н   | BA, CA, AP | BW/BWA    | Term Burst, Start Block Write: Determine AP | 4, 9  |

|               | L                      | L   | н   | н  | L   | BA, RA     | ACT       | ILLEGAL                                     | 3     |

|               | L                      | L   | н   | н  | н   | BA, RA     | ACTM      | ILLEGAL                                     | 3     |

|               | L                      | L   | н   | L  | х   | BA, PA     | PRE/PREAL | Term Burst, Precharging                     |       |

|               | L                      | L   | L   | н  | Х   | Х          | REF/SREF  | ILLEGAL                                     |       |

|               | L                      | L   | L   | L  | L   | Op-Code    | LMR       | ILLEGAL                                     |       |

| -             | L                      | L   | L   | L  | н   | Op-Code    | LSMR      | ILLEGAL                                     |       |

|               | н                      | х   | х   | х  | х   | Х          | INHBT     | Continue Burst to End -> Row Active         |       |

|               | L                      | н   | н   | х  | х   | х          | NOP       | Continue Burst to End -> Row Active         |       |

| Write         | L                      | н   | н   | L  | Х   | х          | BST       | Burst Stop -> Row Active                    |       |

|               | L                      | н   | L   | н  | х   | BA, CA, AP | RD/RDA    | Term Burst, New Read: Determine AP          | 9     |

|               | L                      | н   | L   | L  | L   | BA, CA, AP | WR/WRA    | Term Burst, Start Write: Determine AP       | 4, 9  |

|               | L                      | н   | L   | L  | н   | BA, CA, AP | BW/BWA    | Term Burst, Start Block Write: Determine AP | 4, 9  |

|               | L                      | L   | н   | н  | L   | BA, RA     | ACT       | ILLEGAL                                     | 3     |

|               | L                      | L   | Н   | Н  | Н   | BA, RA     | ACTM      | ILLEGAL                                     | 3     |

|               | L                      | L   | Н   | L  | Х   | BA, PA     | PRE/PREAL | Term Burst, Precharging                     | 10    |

|               | L                      | L   | L   | н  | Х   | Х          | REF/SREF  | ILLEGAL                                     |       |

|               | L                      | L   | L   | L  | L   | Op-Code    | LMR       | ILLEGAL                                     |       |

|               | L                      | L   | L   | L  | н   | Op-Code    | LSMR      | ILLEGAL                                     |       |

1. H:High level, L:Low level, X:High or low level (Don't care), V:Valid data input.

2. All entries assume that CKE was active (High level) during the preceding clock cycle.

3. Illegal to bank specified states; Function may be legal in the bank indicated by Bank Address (BA), depending on the state of that bank.

4. Must satisfy bus contention, bus turn around, and/or write recovery requirements.

5. If both are idle, and CKE is inactive (Low level), the device will enter Power Down Mode. All inputs buffers except CKE will be disabled.

6. If both banks are idle, and CKE is inactive (Low level), the device will enter Self Refresh Mode. All input buffer except CKE will be disabled.

7. Illegal if  $t_{RRD}$  is not satisfied.

8. Illegal if  $t_{\mathsf{RAS}}$  is not satisfied.

9. Must satisfy burst interrupt condition.

$RA = Row Address (A_0 - A_8)$ NOP = No Operation Command

10. Must mask preceding data which don't satisfy t<sub>DPL</sub>.

11. Illegal if t<sub>RCD</sub> is not satisfied.

BA = Bank Address (BA) CA = Column Address (A<sub>0</sub> - A<sub>7</sub>)  $PA = Prechare All (A_8)$  $AP = Auto Precharge (A_8)$

## **Operative Command Table (Part 3 of 6)**

| Current State           | CS | RAS | CAS | WE | DSF | Add        | Command   | Action                               | Notes |

|-------------------------|----|-----|-----|----|-----|------------|-----------|--------------------------------------|-------|

|                         | н  | х   | х   | х  | Х   | Х          | INHBT     | Continue Burst to End -> Precharging |       |

|                         | L  | н   | н   | х  | х   | х          | NOP       | Continue Burst to End -> Precharging |       |

| Read with<br>Auto Pre-  | L  | н   | н   | L  | х   | х          | BST       | ILLEGAL                              |       |

| charge                  | L  | н   | L   | н  | х   | BA, CA, AP | RD/RDA    | ILLEGAL                              |       |

|                         | L  | н   | L   | L  | L   | BA, CA, AP | WR/WRA    | ILLEGAL                              |       |

|                         | L  | н   | L   | L  | н   | BA, CA, AP | BW/BWA    | ILLEGAL                              |       |

|                         | L  | L   | н   | н  | L   | BA, RA     | ACT       | ILLEGAL                              | 3     |

|                         | L  | L   | н   | н  | н   | BA, RA     | ACTM      | ILLEGAL                              | 3     |

|                         | L  | L   | н   | L  | х   | BA, PA     | PRE/PREAL | ILLEGAL                              | 3     |

|                         | L  | L   | L   | н  | х   | Х          | REF/SREF  | ILLEGAL                              | 3     |

|                         | L  | L   | L   | L  | L   | Op-Code    | LMR       | ILLEGAL                              |       |

|                         | L  | L   | L   | L  | н   | Op-Code    | LSMR      | ILLEGAL                              |       |

|                         | н  | х   | х   | Х  | х   | Х          | INHBT     | Continue Burst to End -> Precharging |       |

| 10/1:10                 | L  | н   | н   | Х  | х   | Х          | NOP       | Continue Burst to End -> Precharging |       |

| Write<br>with Auto Pre- | L  | н   | н   | L  | х   | х          | BST       | ILLEGAL                              |       |

| charge                  | L  | н   | L   | н  | х   | BA, CA, AP | RD/RDA    | ILLEGAL                              |       |

|                         | L  | н   | L   | L  | L   | BA, CA, AP | WR/WRA    | ILLEGAL                              |       |

|                         | L  | н   | L   | L  | н   | BA, CA, AP | BW/BWA    | ILLEGAL                              |       |

|                         | L  | L   | н   | н  | L   | BA, RA     | ACT       | ILLEGAL                              | 3     |

|                         | L  | L   | н   | н  | н   | BA, RA     | ACTM      | ILLEGAL                              | 3     |

|                         | L  | L   | н   | L  | Х   | BA, PA     | PRE/PREAL | ILLEGAL                              | 3     |

|                         | L  | L   | L   | н  | Х   | Х          | REF/SREF  | ILLEGAL                              | 3     |

|                         | L  | L   | L   | L  | L   | Op-Code    | LMR       | ILLEGAL                              |       |

|                         | L  | L   | L   | L  | н   | Op-Code    | LSMR      | ILLEGAL                              |       |

1. H:High level, L:Low level, X:High or low level (Don't care), V:Valid data input.

2. All entries assume that CKE was active (High level) during the preceding clock cycle.

3. Illegal to bank specified states; Function may be legal in the bank indicated by Bank Address (BA), depending on the state of that bank.

4. Must satisfy bus contention, bus turn around, and/or write recovery requirements.

5. If both are idle, and CKE is inactive (Low level), the device will enter Power Down Mode. All inputs buffers except CKE will be disabled.

6. If both banks are idle, and CKE is inactive (Low level), the device will enter Self Refresh Mode. All input buffer except CKE will be disabled.

7. Illegal if  $t_{RRD}$  is not satisfied.

8. Illegal if  $t_{RAS}$  is not satisfied.

9. Must satisfy burst interrupt condition.

10. Must mask preceding data which don't satisfy  $t_{\text{DPL}}$ .

11. Illegal if  $t_{RCD}$  is not satisfied.

| $RA = Row Address (A_0 - A_8)$ | BA = Bank Address (BA)                                 | $PA = Prechare All (A_8)$   |

|--------------------------------|--------------------------------------------------------|-----------------------------|

| NOP = No Operation Command     | CA = Column Address (A <sub>0</sub> - A <sub>7</sub> ) | $AP = Auto Precharge (A_8)$ |

©IBM Corporation. All rights reserved. Use is further subject to the provisions at the end of this document.

| Operative | Command | Table | (Part 4 of 6) |

|-----------|---------|-------|---------------|

|-----------|---------|-------|---------------|

| Current State     | $\overline{\text{CS}}$ | RAS | CAS | WE | DSF | Add        | Command   | Action                                         | Notes |

|-------------------|------------------------|-----|-----|----|-----|------------|-----------|------------------------------------------------|-------|

|                   | н                      | Х   | х   | х  | х   | Х          | INHBT     | Nop -> Enter Idle after t <sub>RP</sub>        |       |

|                   | L                      | н   | н   | х  | х   | Х          | NOP       | Nop -> Enter Idle after t <sub>RP</sub>        |       |

| Precharging       | L                      | н   | н   | L  | х   | Х          | BST       | Nop -> Enter Idle after t <sub>RP</sub>        |       |

|                   | L                      | н   | L   | н  | Х   | BA, CA, AP | RD/RDA    | ILLEGAL                                        | 3     |

|                   | L                      | н   | L   | L  | L   | BA, CA, AP | WR/WRA    | ILLEGAL                                        | 3     |

|                   | L                      | н   | L   | L  | н   | BA, CA, AP | BW/BWA    | ILLEGAL                                        | 3     |

|                   | L                      | L   | н   | н  | L   | BA, RA     | ACT       | ILLEGAL                                        | 3     |

|                   | L                      | L   | н   | н  | н   | BA, RA     | ACTM      | ILLEGAL                                        | 3     |

|                   | L                      | L   | н   | L  | Х   | BA, PA     | PRE/PREAL | Nop -> Enter Idle after t <sub>RP</sub>        |       |

|                   | L                      | L   | L   | н  | Х   | Х          | REF/SREF  | ILLEGAL                                        |       |

|                   | L                      | L   | L   | L  | L   | Op-Code    | LMR       | ILLEGAL                                        |       |

|                   | L                      | L   | L   | L  | н   | Op-Code    | LSMR      | Load Special Mode Register                     |       |

|                   | н                      | х   | Х   | х  | Х   | Х          | INHBT     | Nop -> Enter Row Active after $t_{RCD}$        |       |

| <b></b>           | L                      | н   | н   | х  | х   | Х          | NOP       | Nop -> Enter Row Active after t <sub>RCD</sub> |       |

| Row<br>Activating | L                      | н   | н   | L  | Х   | Х          | BST       | Nop -> Enter Row Active after t <sub>RCD</sub> |       |

|                   | L                      | н   | L   | н  | Х   | BA, CA, AP | RD/RDA    | ILLEGAL                                        | 3     |

|                   | L                      | н   | L   | L  | L   | BA, CA, AP | WR/WRA    | ILLEGAL                                        | 3     |

|                   | L                      | н   | L   | L  | н   | BA, CA, AP | BW/BWA    | ILLEGAL                                        | 3     |

|                   | L                      | L   | н   | н  | L   | BA, RA     | ACT       | ILLEGAL                                        | 3, 7  |

|                   | L                      | L   | н   | н  | н   | BA, RA     | ACTM      | ILLEGAL                                        | 3, 7  |

|                   | L                      | L   | Н   | L  | Х   | BA, PA     | PRE/PREAL | ILLEGAL                                        | 3     |

|                   | L                      | L   | L   | н  | Х   | Х          | REF/SREF  | ILLEGAL                                        |       |

|                   | L                      | L   | L   | L  | L   | Op-Code    | LMR       | ILLEGAL                                        |       |

|                   | L                      | L   | L   | L  | н   | Op-Code    | LSMR      | Load Special Mode Register                     |       |

1. H:High level, L:Low level, X:High or low level (Don't care), V:Valid data input.

2. All entries assume that CKE was active (High level) during the preceding clock cycle.

3. Illegal to bank specified states; Function may be legal in the bank indicated by Bank Address (BA), depending on the state of that bank.

4. Must satisfy bus contention, bus turn around, and/or write recovery requirements.

5. If both are idle, and CKE is inactive (Low level), the device will enter Power Down Mode. All inputs buffers except CKE will be disabled.

6. If both banks are idle, and CKE is inactive (Low level), the device will enter Self Refresh Mode. All input buffer except CKE will be disabled.

7. Illegal if  $t_{RRD}$  is not satisfied.

8. Illegal if  $t_{RAS}$  is not satisfied.

9. Must satisfy burst interrupt condition.

10. Must mask preceding data which don't satisfy  $t_{\text{DPL}}$ .

11. Illegal if  $t_{RCD}$  is not satisfied.

| $RA = Row Address (A_0 - A_8)$ | BA = Bank Address (BA)                                 | $PA = Prechare All (A_8)$   |

|--------------------------------|--------------------------------------------------------|-----------------------------|

| NOP = No Operation Command     | CA = Column Address (A <sub>0</sub> - A <sub>7</sub> ) | $AP = Auto Precharge (A_8)$ |

## **Operative Command Table (Part 5 of 6)**

| Current State              | CS | RAS | CAS | WE | DSF | Add        | Command   | Action                                        | Notes |

|----------------------------|----|-----|-----|----|-----|------------|-----------|-----------------------------------------------|-------|

|                            | н  | х   | х   | х  | х   | Х          | INHBT     | Nop -> Enter Row Active after t <sub>WR</sub> |       |

|                            | L  | н   | н   | х  | х   | Х          | NOP       | Nop -> Enter Row Active after $t_{WR}$        |       |

| Write Recov-<br>ering      | L  | н   | н   | L  | х   | х          | BST       | Nop -> Enter Row Active after t <sub>WR</sub> |       |

| ching                      | L  | н   | L   | н  | х   | BA, CA, AP | RD/RDA    | Start Read, Determine AP                      | 4     |

|                            | L  | н   | L   | L  | L   | BA, CA, AP | WR/WRA    | New Write, Determine AP                       |       |

|                            | L  | н   | L   | L  | н   | BA, CA, AP | BW/BWA    | New Block Write, Determine AP                 |       |

|                            | L  | L   | н   | н  | L   | BA, RA     | ACT       | ILLEGAL                                       | 3     |

|                            | L  | L   | н   | н  | н   | BA, RA     | ACTM      | ILLEGAL                                       | 3     |

|                            | L  | L   | н   | L  | Х   | BA, PA     | PRE/PREAL | ILLEGAL                                       | 3     |

|                            | L  | L   | L   | н  | Х   | Х          | REF/SREF  | ILLEGAL                                       |       |

|                            | L  | L   | L   | L  | L   | Op-Code    | LMR       | ILLEGAL                                       |       |

|                            | L  | L   | L   | L  | н   | Op-Code    | LSMR      | Load Special Mask Register                    |       |

|                            | н  | Х   | х   | Х  | Х   | Х          | INHBT     | Nop -> Enter Precharge after t <sub>WR</sub>  |       |

|                            | L  | н   | н   | х  | х   | Х          | NOP       | Nop -> Enter Precharge after $t_{WR}$         |       |

| Write Recov-<br>ering with | L  | н   | н   | L  | х   | х          | BST       | Nop -> Enter Precharge after $t_{WR}$         |       |

| Auto                       | L  | н   | L   | н  | х   | BA, CA, AP | RD/RDA    | ILLEGAL                                       | 3, 4  |

| Precharge                  | L  | н   | L   | L  | L   | BA, CA, AP | WR/WRA    | ILLEGAL                                       | 3     |

|                            | L  | Н   | L   | L  | н   | BA, CA, AP | BW/BWA    | ILLEGAL                                       | 3     |

|                            | L  | L   | н   | н  | L   | BA, RA     | ACT       | ILLEGAL                                       | 3     |

|                            | L  | L   | н   | н  | н   | BA, RA     | ACTM      | ILLEGAL                                       | 3     |

|                            | L  | L   | н   | L  | Х   | BA, PA     | PRE/PREAL | ILLEGAL                                       | 3     |

|                            | L  | L   | L   | Н  | Х   | Х          | REF/SREF  | ILLEGAL                                       |       |

|                            | L  | L   | L   | L  | L   | Op-Code    | LMR       | ILLEGAL                                       |       |

|                            | L  | L   | L   | L  | н   | Op-Code    | LSMR      | ILLEGAL                                       |       |

1. H:High level, L:Low level, X:High or low level (Don't care), V:Valid data input.

2. All entries assume that CKE was active (High level) during the preceding clock cycle.

3. Illegal to bank specified states; Function may be legal in the bank indicated by Bank Address (BA), depending on the state of that bank.

4. Must satisfy bus contention, bus turn around, and/or write recovery requirements.

5. If both are idle, and CKE is inactive (Low level), the device will enter Power Down Mode. All inputs buffers except CKE will be disabled.

6. If both banks are idle, and CKE is inactive (Low level), the device will enter Self Refresh Mode. All input buffer except CKE will be disabled.

7. Illegal if  $t_{RRD}$  is not satisfied.

8. Illegal if  $t_{RAS}$  is not satisfied.

9. Must satisfy burst interrupt condition.

10. Must mask preceding data which don't satisfy  $t_{\text{DPL}}$ .

11. Illegal if  $t_{RCD}$  is not satisfied.

| RA = Row Address (A <sub>0</sub> - A <sub>8</sub> ) | BA = Bank Address (BA)            | $PA = Prechare All (A_8)$   |

|-----------------------------------------------------|-----------------------------------|-----------------------------|

| NOP = No Operation Command                          | $CA = Column Address (A_0 - A_7)$ | $AP = Auto Precharge (A_8)$ |

©IBM Corporation. All rights reserved. Use is further subject to the provisions at the end of this document.

| <b>Operative Command Table</b> | (Part 6 of 6) |

|--------------------------------|---------------|

|--------------------------------|---------------|

| Current State | CS | RAS | CAS | WE | DSF | Add        | Command   | Action                                  | Notes |

|---------------|----|-----|-----|----|-----|------------|-----------|-----------------------------------------|-------|

| Refreshing    | н  | х   | х   | х  | х   | Х          | INHBT     | Nop -> Enter Idle after t <sub>RC</sub> |       |

| . ton oo mig  | L  | н   | н   | х  | х   | х          | NOP       | Nop -> Enter Idle after t <sub>RC</sub> |       |

|               | L  | н   | н   | L  | х   | х          | BST       | Nop -> Enter Idle after t <sub>RC</sub> |       |

|               | L  | н   | L   | н  | х   | BA, CA, AP | RD/RDA    | ILLEGAL                                 |       |

|               | L  | н   | L   | L  | L   | BA, CA, AP | WR/WRA    | ILLEGAL                                 |       |

|               | L  | н   | L   | L  | н   | BA, CA, AP | BW/BWA    | ILLEGAL                                 |       |

|               | L  | L   | н   | н  | L   | BA, RA     | ACT       | ILLEGAL                                 |       |

|               | L  | L   | н   | н  | н   | BA, RA     | ACTM      | ILLEGAL                                 |       |

|               | L  | L   | н   | L  | х   | BA, PA     | PRE/PREAL | ILLEGAL                                 |       |

|               | L  | L   | L   | н  | х   | Х          | REF/SREF  | ILLEGAL                                 |       |

|               | L  | L   | L   | L  | L   | Op-Code    | LMR       | ILLEGAL                                 |       |

|               | L  | L   | L   | L  | н   | OP-CODE    | LSMR      | ILLEGAL                                 |       |

| Mode Regis-   | н  | Х   | Х   | Х  | Х   | Х          | INHBT     | Nop -> Enter Idle after 2Clocks         |       |

| ter Accessing | L  | н   | н   | Х  | Х   | Х          | NOP       | Nop -> Enter Idle after 2Clocks         |       |

|               | L  | н   | н   | L  | х   | х          | BST       | Nop -> Enter Idle after 2Clocks         |       |

|               | L  | н   | L   | н  | Х   | BA, CA, AP | RD/RDA    | ILLEGAL                                 |       |

|               | L  | н   | L   | L  | L   | BA, CA, AP | WR/WRA    | ILLEGAL                                 |       |

|               | L  | н   | L   | L  | н   | BA, CA, AP | BW/BWA    | ILLEGAL                                 |       |

|               | L  | L   | н   | н  | L   | BA, RA     | ACT       | ILLEGAL                                 |       |

|               | L  | L   | Н   | Н  | Н   | BA, RA     | ACTM      | ILLEGAL                                 |       |

|               | L  | L   | Н   | L  | Х   | BA, PA     | PRE/PREAL | ILLEGAL                                 |       |

|               | L  | L   | L   | Н  | Х   | Х          | REF/SREF  | ILLEGAL                                 |       |

|               | L  | L   | L   | L  | L   | Op-Code    | LMR       | ILLEGAL                                 |       |

|               | L  | L   | L   | L  | н   | Op-Code    | LSMR      | ILLEGAL                                 |       |

1. H:High level, L:Low level, X:High or low level (Don't care), V:Valid data input.

2. All entries assume that CKE was active (High level) during the preceding clock cycle.

3. Illegal to bank specified states; Function may be legal in the bank indicated by Bank Address (BA), depending on the state of that bank.

4. Must satisfy bus contention, bus turn around, and/or write recovery requirements.

5. If both are idle, and CKE is inactive (Low level), the device will enter Power Down Mode. All inputs buffers except CKE will be disabled.

6. If both banks are idle, and CKE is inactive (Low level), the device will enter Self Refresh Mode. All input buffer except CKE will be disabled.

7. Illegal if  $t_{RRD}$  is not satisfied.

8. Illegal if  $t_{RAS}$  is not satisfied.

9. Must satisfy burst interrupt condition.

10. Must mask preceding data which don't satisfy  $t_{\text{DPL}}$ .

11. Illegal if  $t_{RCD}$  is not satisfied.

| $RA = Row Address (A_0 - A_8)$ | BA = Bank Address (BA)                                 | $PA = Prechare All (A_8)$   |

|--------------------------------|--------------------------------------------------------|-----------------------------|

| NOP = No Operation Command     | CA = Column Address (A <sub>0</sub> - A <sub>7</sub> ) | $AP = Auto Precharge (A_8)$ |

## **Function Truth Table**

| Operation                     | Cł     | ΚE     | CS     | RAS    | CAS    | WE     | DSF    | DQM    | BA                | A <sub>8</sub> | A <sub>7</sub> -A <sub>0</sub> | MNE      |

|-------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|-------------------|----------------|--------------------------------|----------|

| Operation                     | n-1    | n      | 63     | RAS    | CAS    | VVE    | DSF    | DQIVI  | (A <sub>9</sub> ) | A8             | A7-A0                          | IVINE    |

| Device Deselect               | Н      | Х      | н      | Х      | Х      | Х      | Х      | Х      | Х                 | Х              | Х                              | INHBT    |

| No Operation                  | Н      | Х      | L      | н      | н      | н      | Х      | Х      | Х                 | Х              | Х                              | NOP      |

| Load Mode Register            | н      | Х      | L      | L      | L      | L      | L      | Х      | С                 | P COD          | Ε                              | LMR      |

| Load Special Mode Register    | Н      | Х      | L      | L      | L      | L      | н      | Х      | C                 | P COD          | Ε                              | LSMR     |

| Row Activate                  | Н      | Х      | L      | L      | н      | н      | L      | Х      | BS                | Row            | Addr                           | ACT      |

| Row Activate w/WPB            | н      | Х      | L      | L      | н      | н      | н      | Х      | BS                | Row            | Addr                           | ACTM     |

| Read                          | Н      | Х      | L      | н      | L      | Н      | Х      | Х      | BS                | L              | Col.                           | RD       |

| Read w/ Auto Percharge        | н      | Х      | L      | н      | L      | н      | Х      | Х      | BS                | н              | Col.                           | RDA      |

| Write Command                 | н      | Х      | L      | н      | L      | L      | L      | Х      | BS                | L              | Col.                           | WR       |

| Write w/ Auto Precharge       | н      | Х      | L      | н      | L      | L      | L      | Х      | BS                | н              | Col.                           | WRA      |

| Block Write                   | н      | Х      | L      | н      | L      | L      | н      | Х      | BS                | L              | Col.                           | BW       |

| Block Write w/ Auto Precharge | Н      | Х      | L      | н      | L      | L      | н      | Х      | BS                | н              | Col.                           | BWA      |

| Burst Termination             | н      | Х      | L      | н      | Н      | L      | Х      | Х      | Х                 | Х              | Х                              | BST      |

| Precharge Single Bank         | Н      | Х      | L      | L      | н      | L      | Х      | Х      | BS                | L              | Х                              | PRE      |

| Precharge All Banks           | Н      | Х      | L      | L      | н      | L      | х      | Х      | х                 | н              | Х                              | PREAL    |

| Auto Refresh                  | Н      | Н      | L      | L      | L      | Н      | Х      | Х      | Х                 | Х              | Х                              | REF      |

| Self Refresh Entry            | Н      | L      | L      | L      | L      | н      | х      | Х      | Х                 | х              | Х                              | SREF(EN) |

| Self Refresh Exit             | L<br>L | H<br>H | H<br>L | X<br>H | X<br>H | X<br>H | X<br>X | X<br>X | X<br>X            | X<br>X         | X<br>X                         | SREF(EX) |

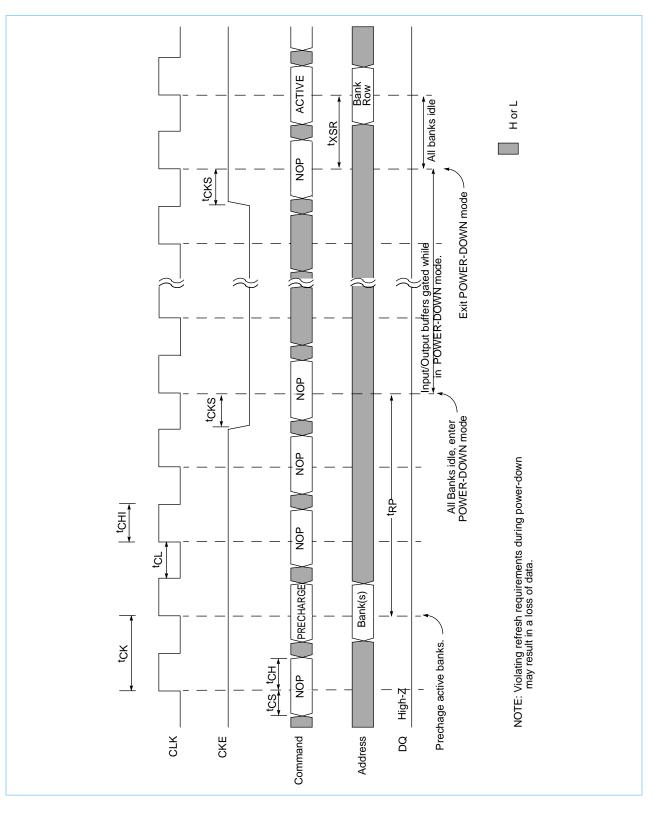

| Power Down Mode (entry)       | н      | L      | н      | х      | Х      | Х      | Х      | Х      | Х                 | Х              | Х                              | PDN-(EN) |

| Power Down Mode (entry)       | Н      | L      | L      | н      | н      | н      | Х      | Х      | Х                 | Х              | Х                              | PDN-(EN) |

| Power Down Mode (exit)        | L      | Н      | х      | х      | Х      | Х      | х      | Х      | х                 | х              | Х                              | PDN-(EX) |

1. All inputs are latched on the rising edge of the CLK.

2. LMR, LSMR, REF, and SREF commands should be issued only after both banks are deactivated (PREAL command).

3. ACT and ACTM command should be issued only after the corresponding bank has been deactivated (PRE command).

4. WR, WRA, RD, RDA should be issued after the corresponding bank has been activated (ACT command).

5. Auto Precharge command is not valid for full-page burst.

6. BW and BWA commands use mask register data only after ACTM command. DQM byte masking is active regardless of WPB mask.

7. Loading Mask Register: Initiate an LSMR cycle with address pin A<sub>5</sub>=1 to load the Mask register with the Mask data present on DQ pins. Except A<sub>5</sub>, all other address pins must be "0" during LSMR cycle while loading the Mask Register.

8. Loading Color Register: Initiate an LSMR cycle with address pin A<sub>6</sub>=1 to load the Color register with the Color input data on DQ pins. Except A<sub>6</sub>, all other address pins must be "0" during LSMR cycle while loading the Color register 0.

9. Any Write or Block Write cycles to the selected bank/row while active will be masked according to the contents of the mask register, in addition to the DQM signals and the column/byte mask information (the later for Block Writes only).

10. Block Writes are not burst oriented and always apply to the eight column locations selected by A7-A3.

## **Functional Description**

IBM's 8Mb SGRAM is a dual bank 128K x 32 SDRAM with graphics features of Block Write and Masked Write. It consists of two banks. Each bank is organized as 512 rows x 256 columns x 32 bits.

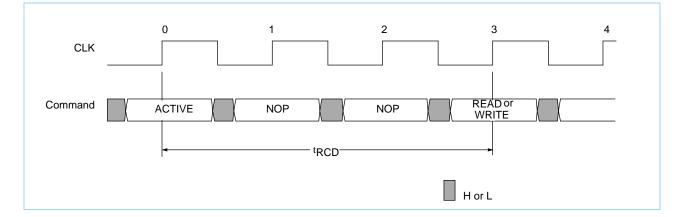

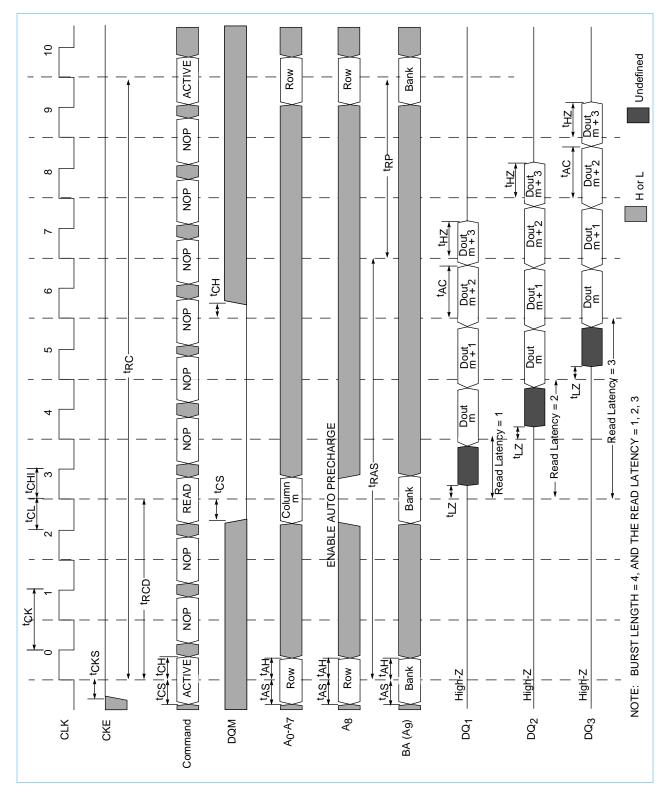

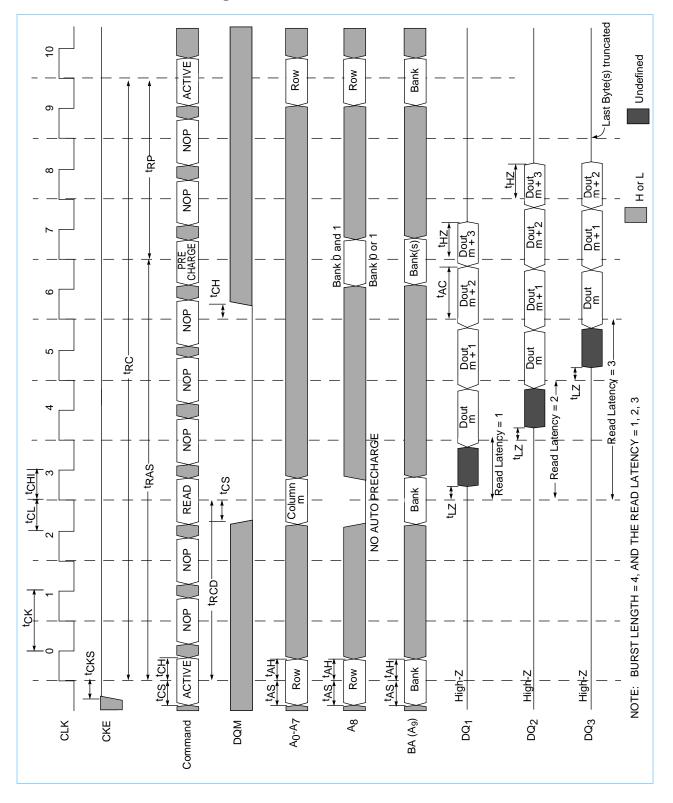

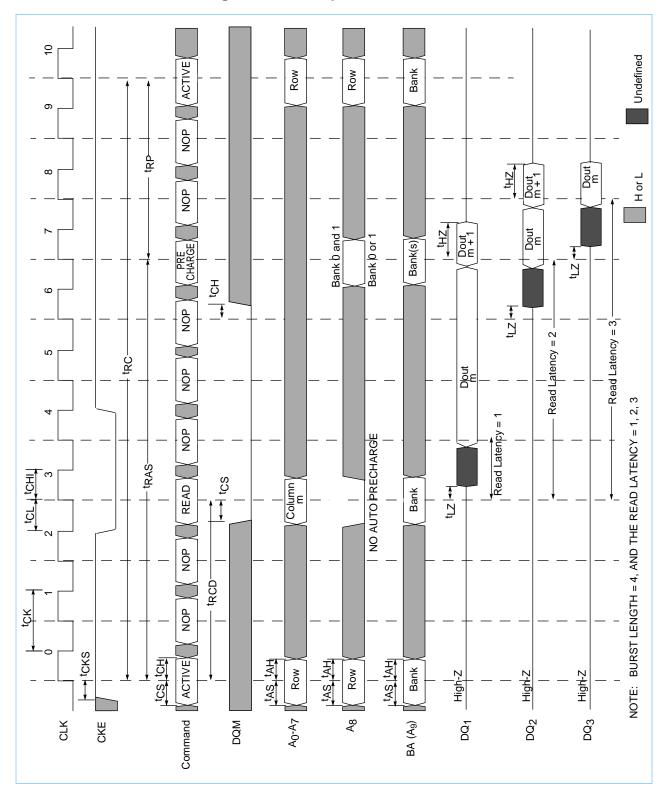

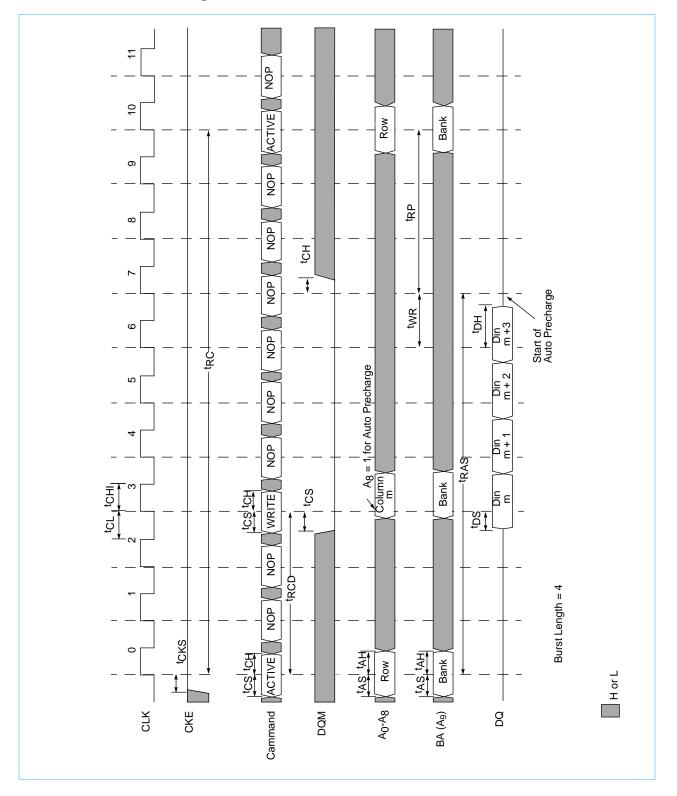

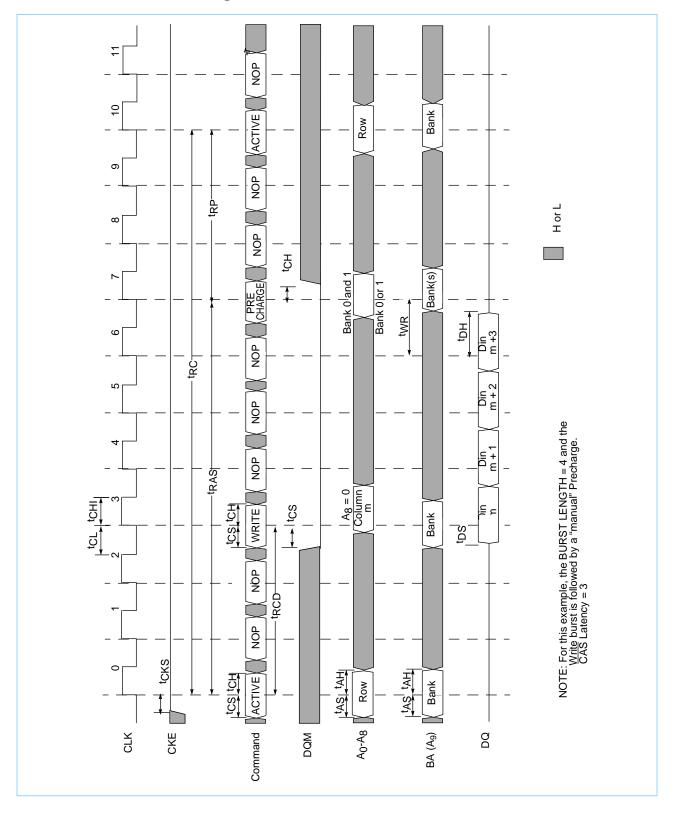

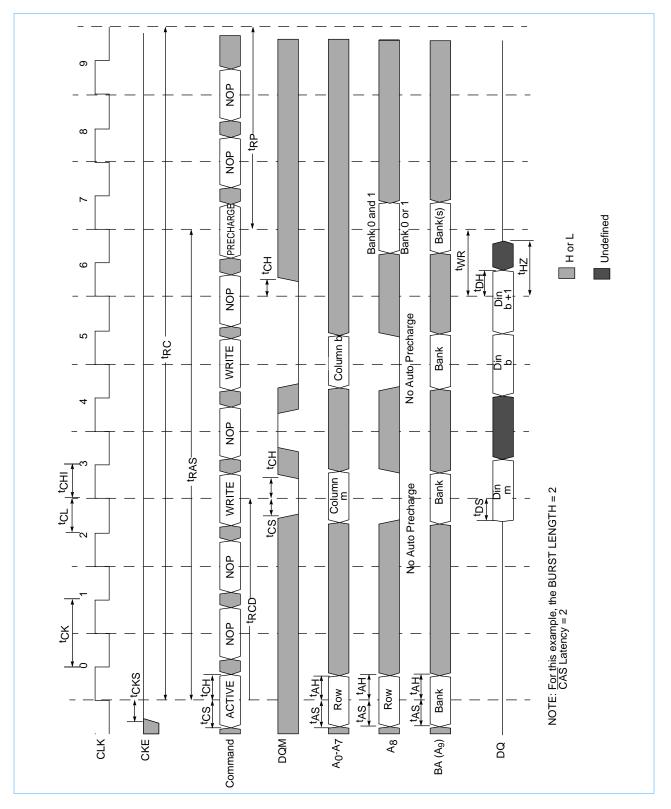

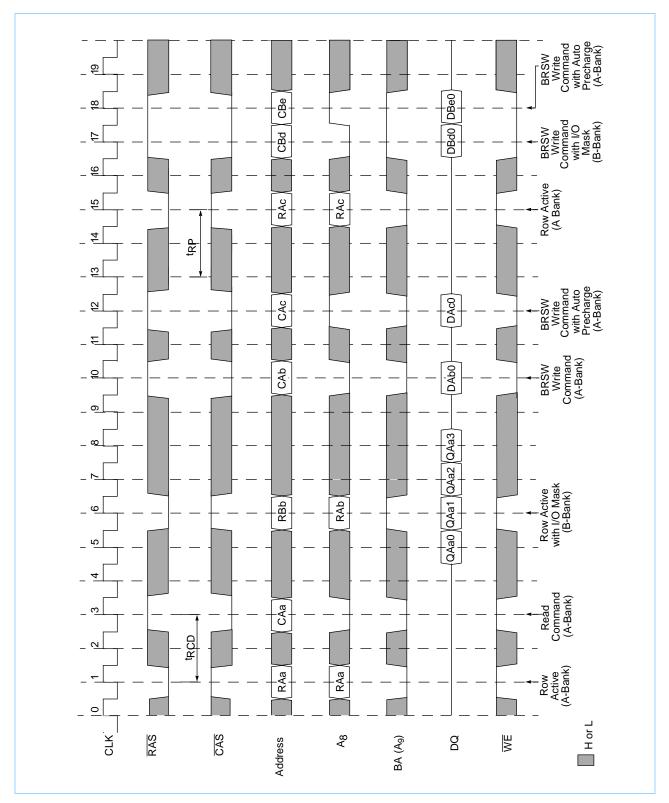

Read and Write accesses are burst oriented. Accesses begin with the registration of an Active command which is then followed by a Read or Write command. The address bits registered coincident with the Active command are used to select the bank and the row to be accessed. Address bit BA (A<sub>9</sub>) selects the bank and address bits  $A_8$ - $A_0$  select the row. Address bits  $A_7$ - $A_0$  registered coincident with the Read and Write command are used to select the starting column location for the burst access.

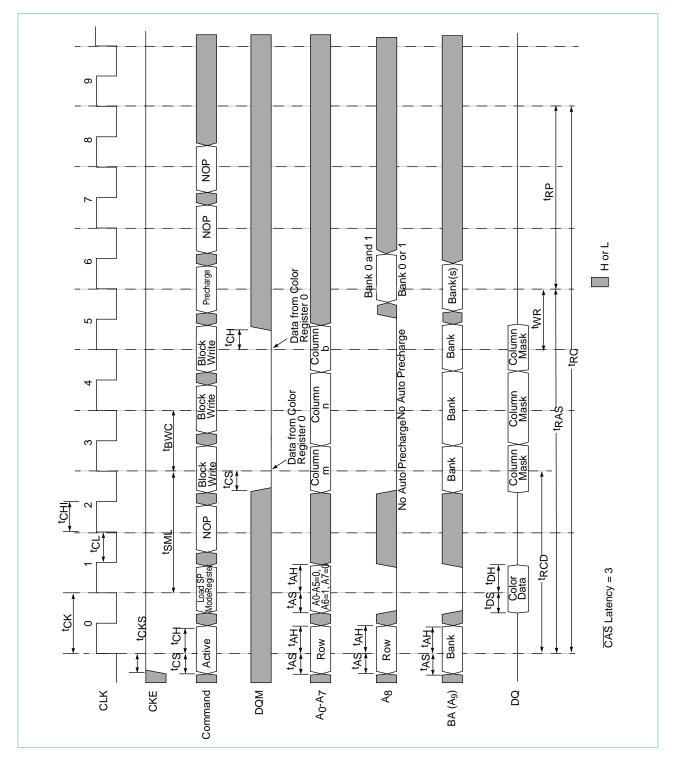

Block Writes are not burst oriented and always apply to eight column locations selected by  $A_7$ - $A_3$ . DQs registered at Write command are used to mask the selected columns. DQs registered coincident with the Active command are used as Write-per-Bit mask. DQs registered coincident with the Load Special Mode Register command are used as Color data (LC bit =1) or Persistent Mask (LM = 1). If LC and LM are both 1 in the same Load Special Mode Register command cycle, the data of the Mask and the Color Register will be unknown.

#### Initialization

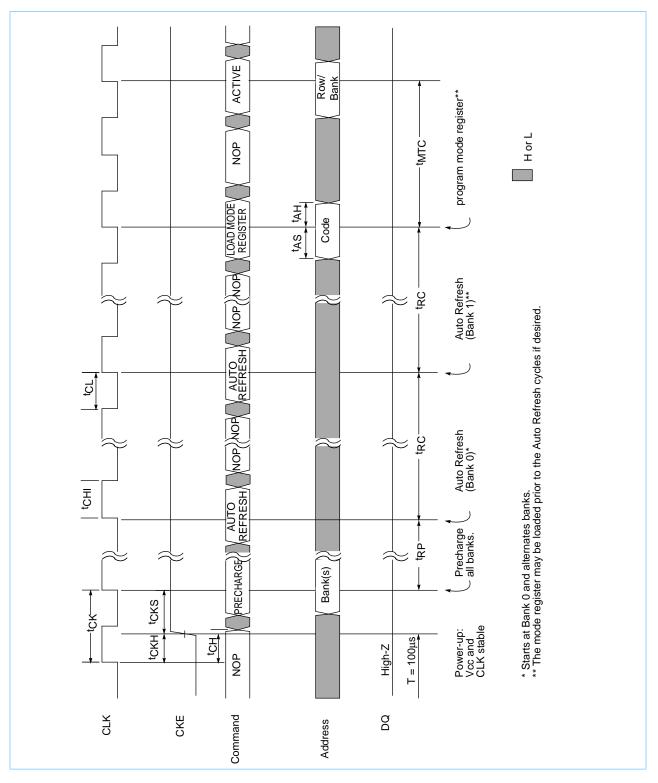

SGRAMs must be initialized in a predefined manner to prevent undefined operation. Once power is applied, the SGRAM requires a 100 $\mu$ s delay prior to activating CKE. All inputs should be held high during this phase of power up. After a delay of 100 $\mu$ s or more, the CKE pin must be driven high before a positive clock (CLK) edge. The first command will be registered on the clock edge following t<sub>CKS</sub>.

Both banks must then be pre-charged by issuing PREAL command, thereby placing the device in the "all banks idle" state. Once in the idle state, at least two Auto Refresh cycles must be performed. Once the Auto Refresh cycles are complete, the SGRAM is ready for Mode Register programming. Because the Mode Register will power up in an unknown state, it should be programmed prior to performing any operational command.

## **Register Definition**

The following pages describe the Mode Register and Special Mode Register functions.

#### **Mode Register**

The Mode Register is used to define: a Burst Length, a Burst type, a Read Latency and an operating mode as shown in the diagram on page 16. The mode register is programmed via the Load Mode Register command and will retain the stored information until it is programmed again or the device loses power. The mode register must be loaded when both banks are idle and the controller must wait the specified time before initiating the subsequent command. Violating either of these requirements may result in unknown operation.

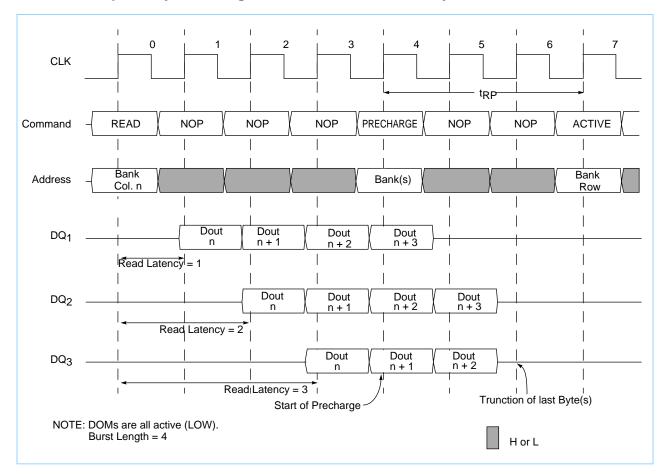

#### **Burst Length**

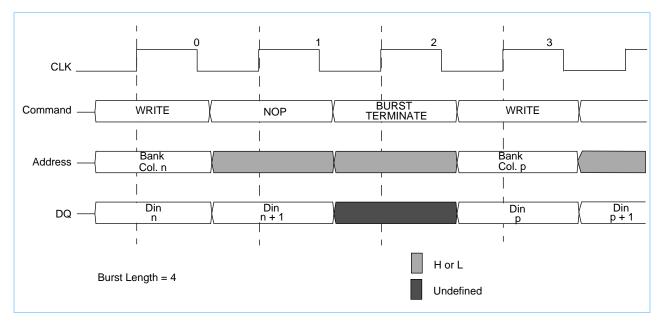

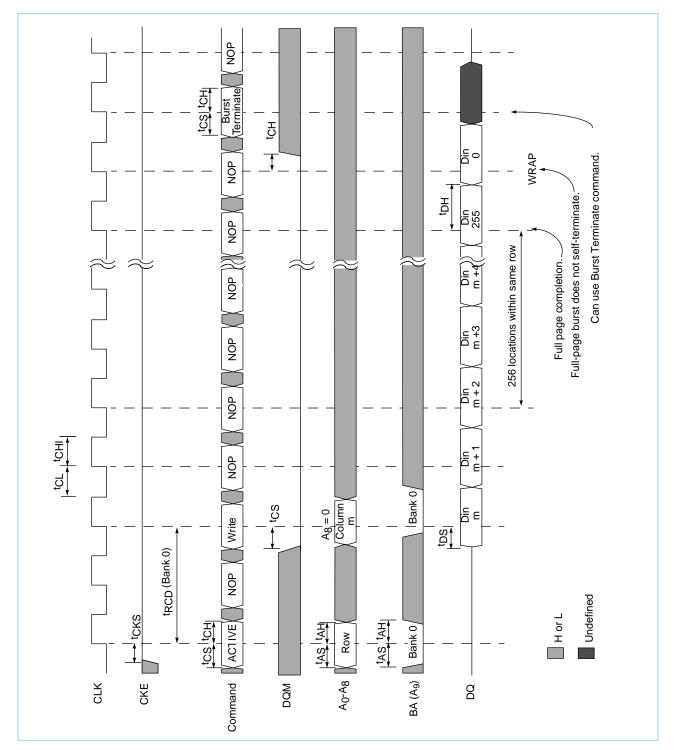

Read and Write operations to the SGRAM are burst oriented, with the burst length being programmable, as shown in the diagram on page 16. The burst length determines the maximum number of column locations that can be accessed for a given Read or Write command. Burst lengths of 1, 2, 4, or 8 locations are available for both the sequential and the interleaved burst types and a Full Page Burst is available for the sequential type. The Full Page Burst is used in conjunction with the Burst Terminate command to generate arbitrary burst lengths.

When a Read or Write command is issued, a block of columns equal to the burst length is selected. The block is defined by address bits  $A_7$ - $A_1$  when the burst length is set to 2, by  $A_7$ - $A_2$  for burst length is set to 4 and by  $A_7$ - $A_3$  when the burst length is set to 8. The lower order bit(s) are used to select the starting location within the block. The burst will wrap within the block if a boundary is reached.

#### **Burst Type**

Accesses within a given burst may be programmed to be either sequential or interleaved and the type is selected based on the setting of BT bit in the mode register. If BT is set to "0", the burst type is sequential, if BT is "1", the burst type is interleave.

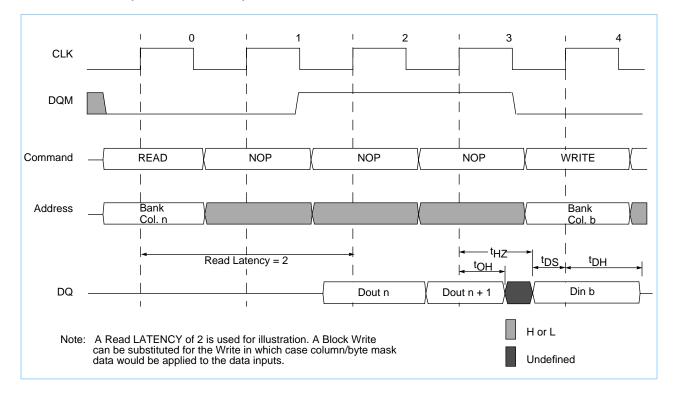

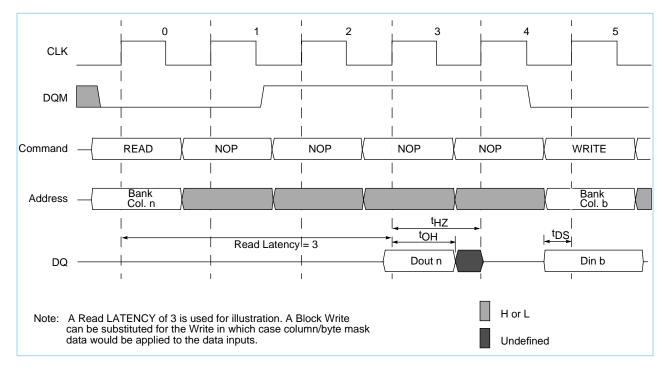

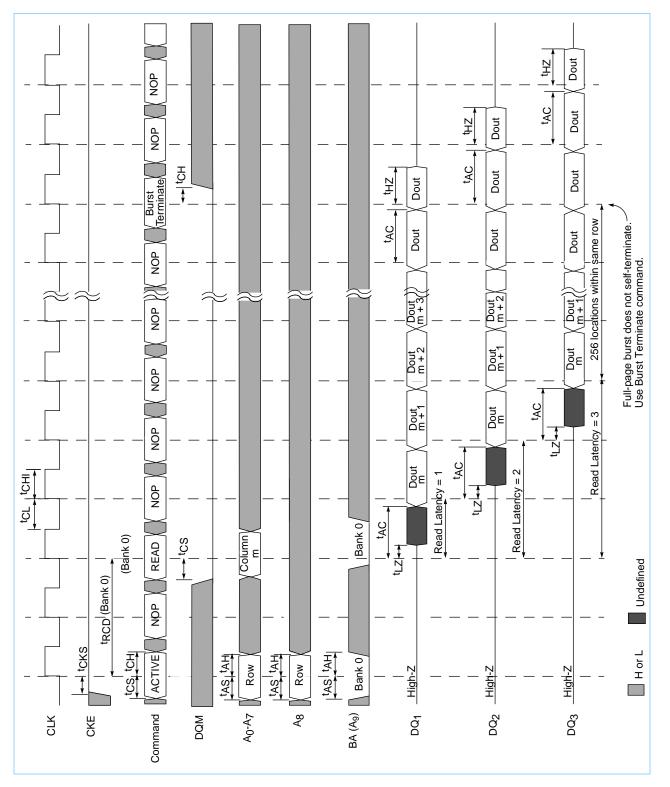

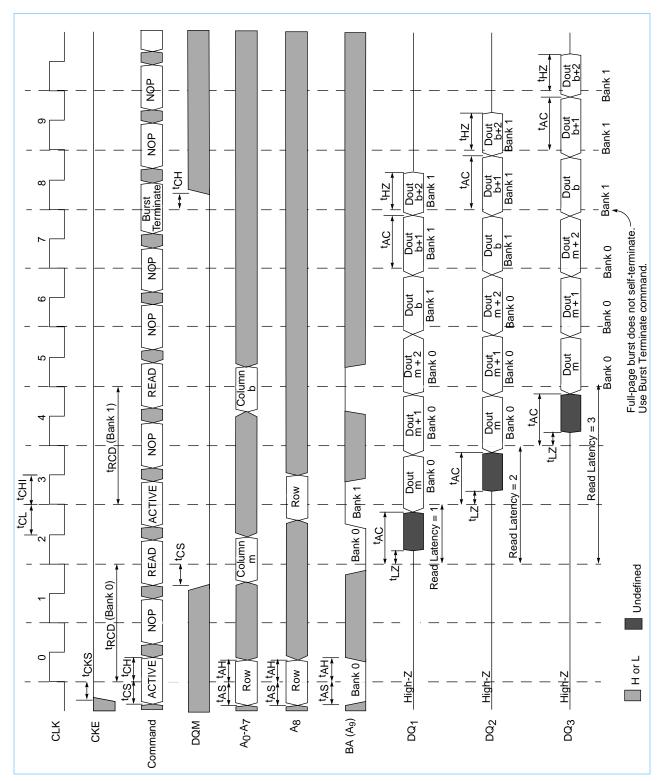

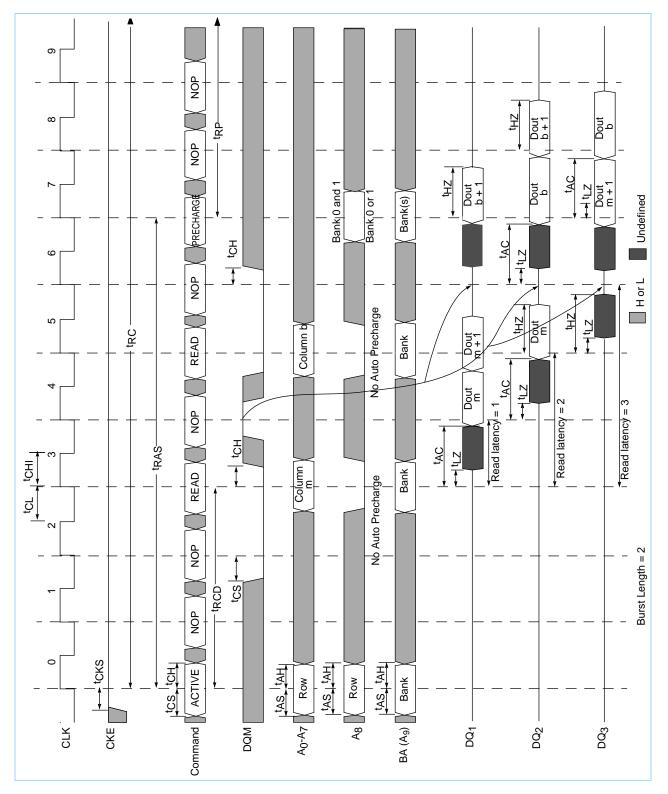

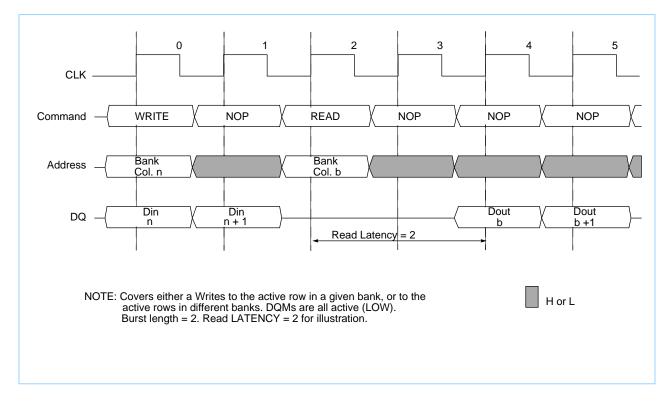

#### **Read Latency**

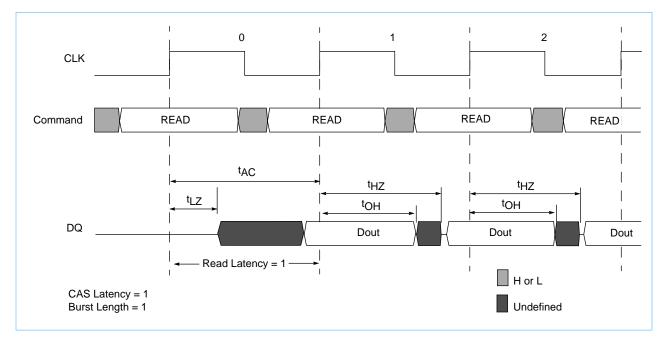

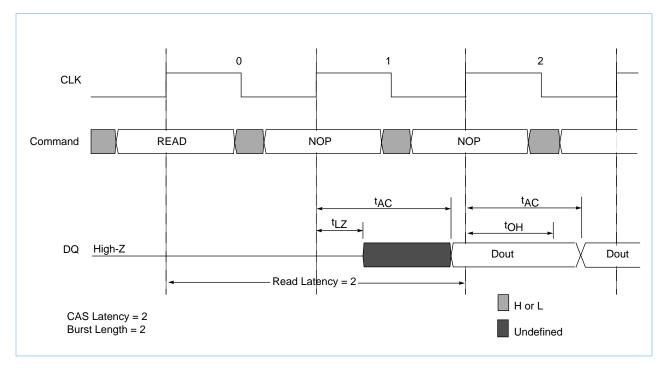

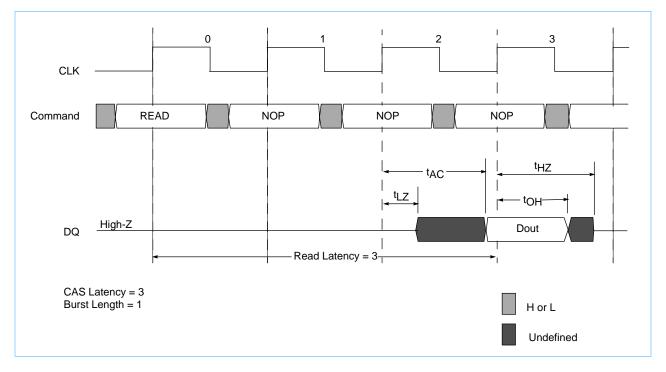

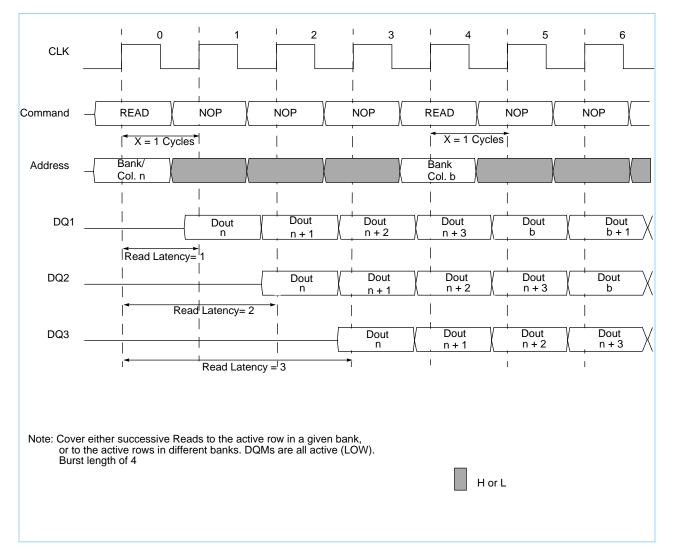

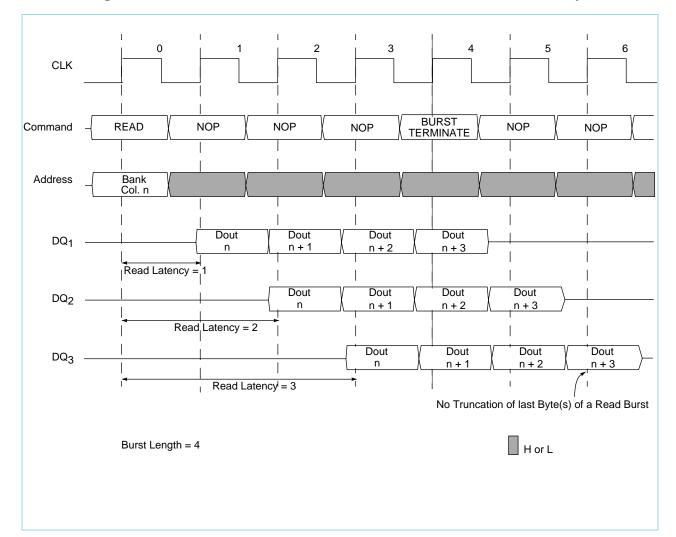

The Read Latency is the delay in clock cycles between the registration of a Read command and the availability of the first piece of output data. The latency can be set to 1, 2 or 3 clocks. If a Read command is registered at clock edge n and the Read Latency is 2 clocks, the data will be available by clock edge n+2. The DQs will start driving as a result of the clock edge one cycle earlier (n+1) and provided the relevant access times are met, the data will be valid by clock edge n+2.

#### **Operation Mode**

In normal operation, the  $M_7$ - $M_9$  bits of Mode Register (MR) are set "0". The programmed burst length applies to both read and write bursts. If Bit  $M_7$  is set equal to "1", two Color Registers are specified. Test modes and reserved states should not be used because unknown operation or incompatibility with future versions may result.

#### Load Special Mode Register (LSMR)

The Special Mode Register command is used to load the mask and color registers, which are used in Block Write and Masked Write cycles. The data to be written to either the color registers or the Mask Register is applied to the DQs and the control information is applied to the address inputs. During a LSMR cycle, if the address bit  $A_6$  is "1", and all other address inputs are "0", the Color Register 0 will be loaded with the data on the DQs. If the address bits  $A_6$  and  $A_7$  are both set equal to "1" and Mode Register  $M_7$  bit was already set equal to "1", Color Register 1 will be loaded with the data on the DQs. This color data is used for Block Write cycles. Similarly, when input  $A_5$  is "1", and all other address inputs are "0" during a LSMR cycle, the mask register will be loaded with the data on the DQs.

#### Caution:

Never Set bit  $A_5$  to "1" when  $A_6$  and/or  $A_7$  are set equal to "1" in the same Load Special Mode Register cycle to avoid unknown operation. (See "Special Mode Register Functions" on page 18.)

#### **Color Registers**

Two Color Registers (Color Register 0 and Color Register 1) are available in the devices as shown in the diagram on page 32. Each color register is a 32-bit register which supplies the data during Block Write cycles. The Color Register is loaded via a Load Special Mode Register command, as shown in the diagram on page 32 and will retain data until loaded again with a new data or until power is removed from the SGRAM.

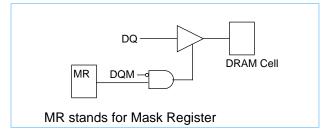

#### **Mask Register**

The Mask Register (or the Write-per-Bit mask register) is a 32-bit register which acts as a per-bit mask during Masked Write and Masked Block Write cycles. The Mask Register is loaded via the Load Special Mode Register command and will retain data until loaded again or until power is removed from the SGRAM.

# **Mode Register Functions**

| BA (A9)    | A8   | A7                    | A6    | A5 A4          | A3  | A2        | A1          | A0                |           |

|------------|------|-----------------------|-------|----------------|-----|-----------|-------------|-------------------|-----------|

| WRITE      | Mode | CR                    |       | LT Mode        | ВТ  |           | BL          |                   |           |

|            |      |                       |       |                |     |           |             |                   |           |

|            |      |                       |       |                | Bit | 2-0       | Burst L     | ength             |           |

|            |      |                       |       |                | 00  | 00        | 1           |                   |           |

|            |      |                       |       |                | 00  |           | 2<br>4      |                   |           |

|            |      |                       |       | Burst Length   |     | 10<br>11  | 8           |                   |           |

|            |      |                       |       | Durst Longin   |     | 00        | R           | *                 |           |

|            |      |                       |       |                |     | 01        | R<br>R      |                   |           |

|            |      |                       |       |                |     | 10<br>11  | R<br>Full F |                   | R*: reser |

|            |      |                       |       | L              |     | I         |             |                   | L         |

|            |      |                       |       |                | (   | 0         | Seau        | uential           |           |

|            |      |                       |       | Burst Type     |     | 1         |             | e (option)        |           |

|            |      |                       |       |                |     |           |             |                   | 1         |

|            |      |                       |       |                |     | 6-4       |             | Latency           |           |

|            |      |                       |       |                | 0   | 00<br>01  |             | R*<br>option)     |           |

|            |      |                       |       | Latency Mode   |     | 10        |             | 2                 |           |

|            |      |                       |       |                |     | 11        |             | 3                 |           |

|            |      |                       |       |                | 1   | xx        |             | R*                |           |

|            |      |                       |       |                |     |           |             |                   | 1         |

|            |      |                       |       |                |     | it 7      |             | gisters           |           |

|            |      |                       |       | Color Register |     | 0         | One<br>Re   | e Color<br>gister |           |

| RΔ         |      |                       |       |                |     | 1         | Two<br>Re   | o Color<br>gister |           |

| BA<br>(A9) | A8   |                       | ode   | _              | I   | · · · · · |             |                   | ,         |

| Ø          | Ø    | Normal                |       |                |     |           |             |                   |           |

| 1          | Ø    | Multiple<br>with Sing | Burst |                |     |           |             |                   |           |

## **Burst Length and Sequence**

## Burst of two

| Starting Address (Column Address A <sub>0</sub> ) | Sequential Addressing Sequence (decimal) | Interleave Addressing Sequence (decimal) |

|---------------------------------------------------|------------------------------------------|------------------------------------------|

| 0                                                 | 0,1                                      | 0,1                                      |

| 1                                                 | 1,0                                      | 1,0                                      |

## Burst of four

| Starting Address (Column Address A <sub>1</sub> - A <sub>0</sub> ) | Sequential Addressing Sequence (decimal) | Interleave Addressing Sequence (decimal) |

|--------------------------------------------------------------------|------------------------------------------|------------------------------------------|

| 0 (00B)                                                            | 0,1,2,3                                  | 0,1,2,3                                  |

| 1 (01B)                                                            | 1,2,3,0                                  | 1,0,3,2                                  |

| 2 (10B)                                                            | 2,3,0,1                                  | 2,3,0,1                                  |

| 3 (11B)                                                            | 3,0,1,2                                  | 3,2,1,0                                  |

## **Burst of eight**

| Starting Address (Column Address A <sub>1</sub> - A <sub>0</sub> ) | Sequential Addressing Sequence (decimal) | Interleave Addressing Sequence (decimal) |

|--------------------------------------------------------------------|------------------------------------------|------------------------------------------|

| 0 (000B)                                                           | 0,1,2,3,4,5,6,7                          | 0,1,2,3,4,5,6,7                          |

| 1 (001B)                                                           | 1,2,3,4,5,6,7,0                          | 1,0,3,2,5,4,7,6                          |

| 2 (010B)                                                           | 2,3,4,5,6,7,0,1                          | 2,3,0,1,6,7,4,5                          |

| 3 (011B)                                                           | 3,4,5,6,7,0,1,2                          | 3,2,1,0,7,6,5,4                          |

| 4 (100B)                                                           | 4,5,6,7,0,1,2,3                          | 4,5,6,7,0,1,2,3                          |

| 5 (101B)                                                           | 5,6,7,0,1,2,3,4                          | 5,4,7,6,1,0,3,2                          |

| 6 (110B)                                                           | 6,7,0,1,2,3,4,5                          | 6,7,4,5,2,3,0,1                          |

| 7 (111B)                                                           | 7,0,1,2,3,4,5,6                          | 7,6,5,4,3,2,1,0                          |

#### Full Page Burst

Full Page Burst is an extension of the above tables of Sequential Addressing with the burst length being 256.

## **Special Mode Register Functions**

|                      |                |                | Functions      |                |                |                |                |                |                |                       |

|----------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------------|

| BA (A <sub>9</sub> ) | A <sub>8</sub> | A <sub>7</sub> | А <sub>6</sub> | А <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | Functions             |

| 0                    | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | Do not load           |

| 0                    | 0              | 0              | 0              | 1              | 0              | 0              | 0              | 0              | 0              | Enable Mask           |

| 0                    | 0              | 0              | 1              | 0              | 0              | 0              | 0              | 0              | 0              | Load Color Register 0 |

| 0                    | 0              | 1              | 1              | 0              | 0              | 0              | 0              | 0              | 0              | Load Color Register 1 |

## **Block Write Illustration**

## Commands

The Function Truth Table on page 12 provides a quick reference of available commands.

#### **Device Deselect (INHBT)**

The device deselect or inhibit function prevents commands from being executed by the SGRAM, regardless of whether the CLK signal is enabled. The device is effectively deactivated ( $\overline{CS}$  is high).

#### No Operation (NOP)

The NOP command is used to perform a no operation to an SGRAM which is selected ( $\overline{CS}$  is low). This prevents unwanted commands being registered during idle or wait states. The execution of the command(s) already in progress will not be affected

#### Load Mode Register (LMR)

The Mode Register is loaded via address input pins BA (A<sub>9</sub>)-A<sub>0</sub>. The LMR command can only be issued when both banks are idle, and a subsequent executable command can not be issued until  $t_{MTC}$  (1 CLK cycle Latency) is met.

#### Load Special Mode Register (LSMR)

LSMR command is used to load either the Color Register or the Mask Register at a time. The control information is provided on inputs BA (A<sub>9</sub>)-A<sub>0</sub>, while the data for the Color or Mask Register is provided on the DQs. The LSMR command can be issued when both banks are idle, or one or both are active but with no Read, Write or Block Write accesses in progress. *A subsequent command can not be issued until t<sub>SML</sub> (2 clocks latency) is met.*

#### Active (ACT)

The ACT command is used to open (or activate) a row in a particular bank. The value on BA ( $A_9$ ) selects the bank and the address provided on input pins  $A_8$ - $A_0$  selects the row. This row remains open for accesses until a Precharge command is issued to the bank. *A Precharge command must be issued before opening a different row in the same bank.*

#### Active with WPB (ACTM)

ACTM command is similar to the ACT command, except that the Write-per-Bit mask is activated. Any Write or Block Write cycles to the selected bank/row while active will be masked according to the contents of the Mask Register.

#### Read (RD)

The Read command is used to initiate a burst read access to an active row. The value on BA (A<sub>9</sub>) selects the bank and the address provided on inputs A<sub>7</sub>-A<sub>0</sub> selects the starting column location. The value on A<sub>8</sub> determines whether or not Auto Precharge is used. If A<sub>8</sub> is "1", Auto Precharge is used. If Auto Precharge is selected, the row being accessed will be precharged at the end of the read burst; if Auto Precharge is not selected, the row will remain open for subsequent accesses. *If a particular DQM was registered high, the corresponding DQs appearing 2 clocks later on the output pins will be High-Z.*

#### Write (WR)

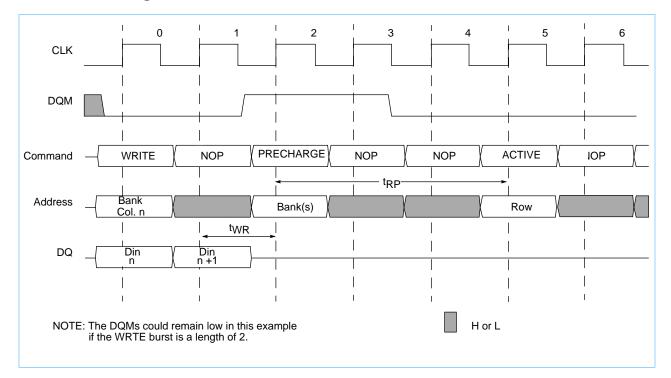

The Write command is used to initiate a burst write access to an active row. The value on BA ( $A_9$ ) selects the bank and the address provided on inputs  $A_7$ - $A_0$  selects the starting column location. The value on  $A_8$  determines whether or not Auto Precharge is used. If  $A_8$  is "1", Auto Precharge is used. If Auto Precharge is selected, the row being accessed will be precharged at the end of write burst; if Auto Precharge is not selected, the row will remain open for subsequent accesses. *If a particular DQM is registered high, the corresponding data inputs will be ignored and the write will not be executed to that byte location.*

#### **Block Write (BW)**

The Block Write command is used to write a single data value to the block of eight consecutive column locations addressed by inputs A<sub>7</sub>-A<sub>3</sub>. The data is provided by the Color Register which must be loaded prior to the Block Write cycle by invoking LSMR cycle. The input data on DQs which is registered coincident with the Block Write command is used to mask specific column/byte combinations within the block. **The DQM signals operate the same way as for Write cycles, but are applied to all eight columns in the selected block.**

#### Precharge (PRE)

The Precharge command is used to deactivate the open row in a particular bank or the open row in both banks. The bank(s) will be available for row access some specified time ( $t_{RP}$ ) after the Precharge command is issued. Input A<sub>8</sub> determines whether one or both banks are to be precharged, input BA (A<sub>9</sub>) selects the bank. If A<sub>8</sub> is "1", both banks are to be precharged and BA (A<sub>9</sub>) is "don't care." Once a bank is precharged (or deactivated), it is in the idle state and must be activated prior to any Read, Write, or Block Write commands being issued to that bank.

#### Auto Precharge (PREA)

The Auto Precharge feature allows the user to issue a Read, Write, or Block Write command that automatically performs a precharge upon the completion of the Block Write access or Read or Write burst, *except in the Full Page Burst mode, where it has no effect.*

The use of this feature eliminates the need to "manually" issue a Precharge command during the functional operation of the SGRAM.

#### Burst Terminate (BST)

The Burst Terminate command is used to truncate either fixed-length or Full Page Bursts.

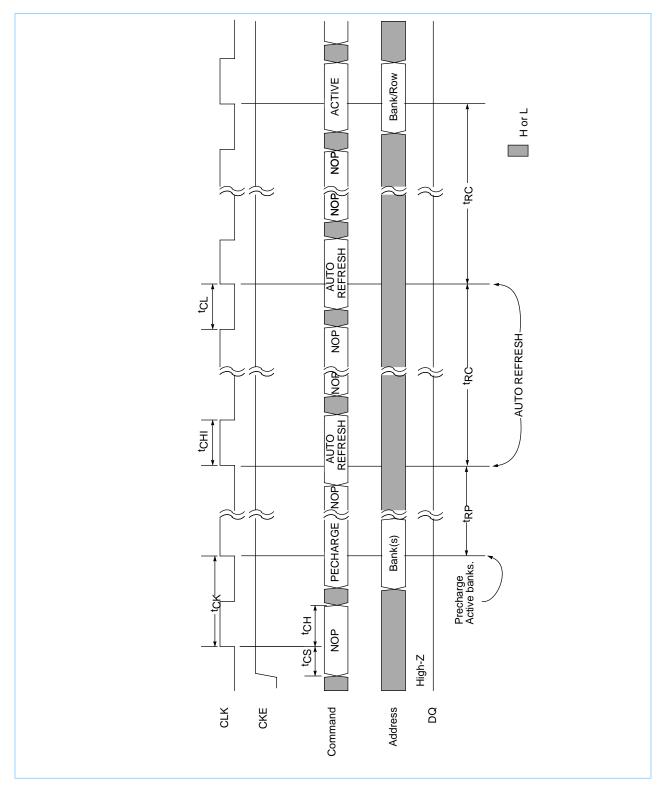

#### Auto Refresh (REF)

Auto Refresh is used to refresh the various rows in the SGRAM and is analogous to  $\overline{CAS}$ -before- $\overline{RAS}$  (CBR) in DRAMs. This command must be issued each time a refresh is required. The addressing is generated by the internal refresh counter, therefore, the address bits are "don't care" during a CBR cycle. The SGRAM requires that 1024 rows to be refreshed every 16ms (t<sub>REF</sub>). This refresh can be accomplished either by providing a Auto Refresh command every 16.6 $\mu$ s or all 1024 Auto Refresh commands can be issued in a burst at the minimum cycle rate (t<sub>RC</sub> =100ns) once every 16ms.

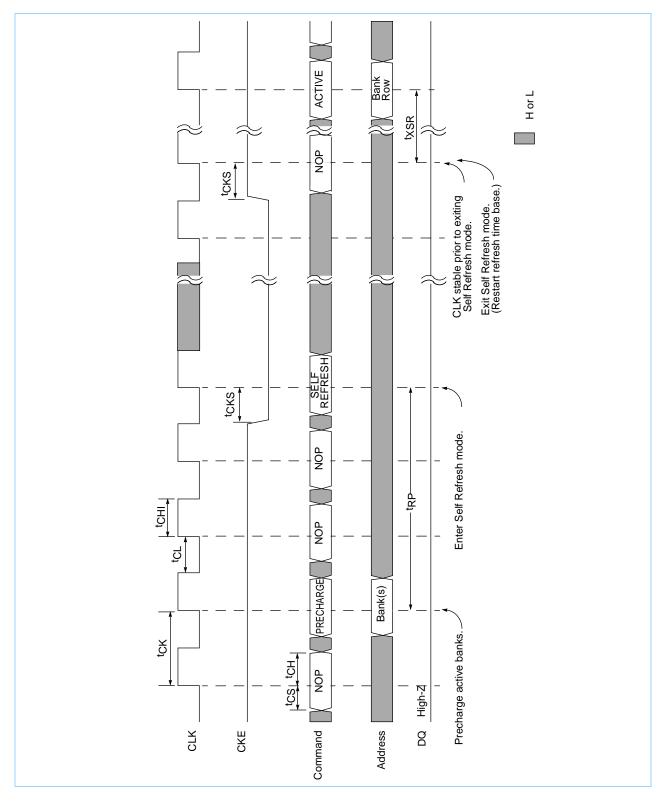

#### Self Refresh (SREF)

The Self Refresh command can be used to retain data in the SGRAM, even if the rest of the system is powered down. When in the Self Refresh mode, the SGRAM retains data without external clocking. Once the SREF command is registered, all the inputs to the SGRAM become "don't care" with the exception of CKE, which must remain low. Once SREF mode is engaged, the SGRAM provides its own internal clocking, causing it to perform its own Auto Refresh cycles. The SGRAM may remain in Self Refresh mode for an indefinite period. The procedure for exiting requires a sequence of commands. First, the system clock must be stable prior to CKE going high. Once CKE is high, the SGRAM must have NOP commands issued for  $t_{XSR}$  (100ns), because of the time required for the completion of any bank currently being internally refreshed.

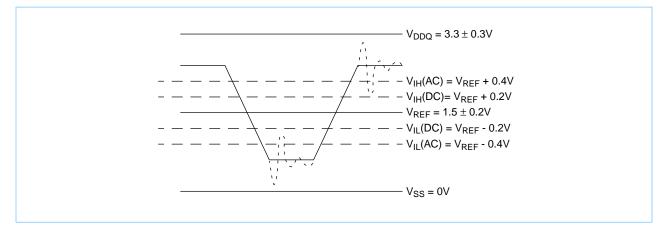

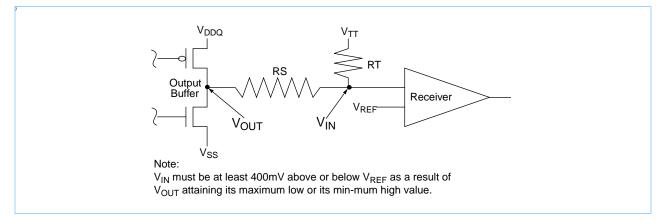

## Stub Series Terminated Logic (SSTL)

#### **DC Input Levels**

SSTL DC input levels reduce the effects of ringing and define the final logic state unambiguously. Once a receiver input has crossed a DC level, it will change and maintain the new state.

#### AC Input Levels

SSTL AC input levels must be met for the receiver to meet the timing specifications.

#### SSTL Input Levels (V<sub>DDQ</sub>=3.3V)

#### **SSTL Supply Voltage Levels**

| Symbol           | Parameter               | Min                    | Nom            | Max                    | Units | Notes |

|------------------|-------------------------|------------------------|----------------|------------------------|-------|-------|

| V <sub>DD</sub>  | Device Supply Voltage   | V <sub>DDQ</sub>       | No Requirement |                        | V     |       |

| V <sub>DDQ</sub> | Output Supply Voltage   | 3.0                    | 3.3            | 3.6                    | V     | 1     |

| $V_{REF}$        | Input Reference Voltage | 1.3                    | 1.5            | 1.7                    | V     | 2     |

| V <sub>TT</sub>  | Termination Voltage     | V <sub>REF</sub> -0.05 | $V_{REF}$      | V <sub>REF</sub> +0.05 | V     | 3     |

1. Under all conditions  $V_{\text{DDQ}}$  must be less than or equal to  $V_{\text{DD}}.$

2. Peak to peak AC noise on V<sub>REF</sub> may not exceed 2% V<sub>REF</sub> (DC). V<sub>REF</sub> is also expected to track noise variations in V<sub>DDQ</sub>.

3.  $V_{\mathsf{TT}}$  of the transmitting device must track  $V_{\mathsf{REF}}$  of the receiving device.

#### SSTL Input AC/DC Logic Levels

| Symbol               | Parameter           | Min                    | Max                    | Units | Notes |

|----------------------|---------------------|------------------------|------------------------|-------|-------|

| V <sub>IH</sub> (DC) | DC Input Logic High | V <sub>REF</sub> +0.20 | V <sub>DDQ</sub> +0.3  | V     | 1     |

| V <sub>IH</sub> (AC) | AC Input Logic High | V <sub>REF</sub> +0.40 | —                      | V     |       |

| V <sub>IL</sub> (DC) | DC Input Logic Low  | -0.30                  | V <sub>REF</sub> -0.20 | V     |       |

| V <sub>IL</sub> (AC) | AC Input Logic Low  | —                      | V <sub>REF</sub> -0.40 | V     |       |

1. The relationship of the V<sub>DDQ</sub> of the driving device and the V<sub>REF</sub> of the receiving device is what determines noise margins. However, in the case of V<sub>IH</sub> (max) (input overdrive) it is the V<sub>DDQ</sub> of the receiving device that is referenced. In the case where a device is implemented such that it supports SSTL\_3 inputs but has no SSTL\_3 outputs (e.g., a translator), and therefore no V<sub>DDQ</sub> supply voltage connection, inputs must tolerate input overdrive to 3.9V (High corner V<sub>DDQ</sub>+300mV).

#### **SSTL AC Test Conditions**

| V <sub>REF</sub> Input Reference Voltage                         | $0.45^*V_{DDQ}$ | V    | 1    |

|------------------------------------------------------------------|-----------------|------|------|

| V <sub>SWING</sub> (max) Input Signal Maximum Peak to Peak Swing | 2.0             | V    | 1, 2 |

| SLEW Input Signal Minimum Slew Rate                              | 1.0             | V/ns | 3    |

1. Input waveform timing is referenced to the input signal crossing the VREF level applied to the device.

2. Compliant devices must still meet the V $_{IH}$  (AC) and V $_{IL}$  (AC) specifications under actual use conditions.

3. The 1V/ns input signal minimum slew rate is to be maintained in the V<sub>IL</sub> max (AC) to V<sub>IL</sub> min (AC) range of the input signal swing.

#### SSTL Output Buffers

The input voltage provided to the receiver depends on three parameters:

- V<sub>DDQ</sub> and current drive capabilities of the output buffer

- Termination voltage

- Termination resistance

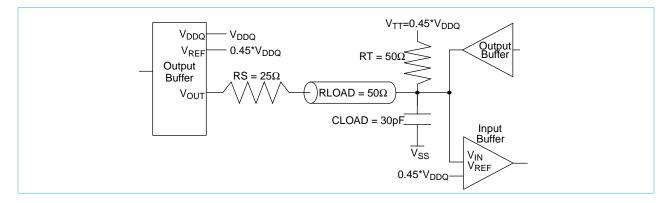

#### Typical SSTL Output Buffer (Driver)

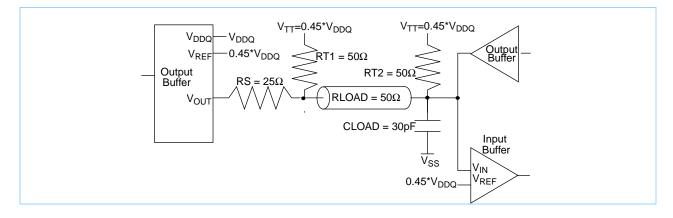

There are two classes of output drivers:

- Class I: RS =  $25\Omega$ , RT =  $50\Omega$ , I<sub>RT</sub> = 8mA (for V<sub>IN</sub> = V<sub>REF</sub> ± 0.4V)

- Class II: RS =  $25\Omega$ , RT =  $25\Omega$ , I<sub>RT</sub> = 16mA (for V<sub>IN</sub> = V<sub>REF</sub>  $\pm 0.4\text{V}$ )

©IBM Corporation. All rights reserved. Use is further subject to the provisions at the end of this document.

| Symbol           | Parameter                                            | Class I               | Class II              | Units | Notes |

|------------------|------------------------------------------------------|-----------------------|-----------------------|-------|-------|

| V <sub>OH</sub>  | Minimum Required Output Pull-up under AC Test Load   | V <sub>TT</sub> + 0.6 | V <sub>TT</sub> + 0.8 | V     |       |

| V <sub>OL</sub>  | Maximum Required Output Pull-down under AC Test Load | V <sub>TT</sub> – 0.6 | V <sub>TT</sub> – 0.8 | V     |       |

| V <sub>OTR</sub> | Input Signal Minimum Slew Rate                       | 0.45*V <sub>DDQ</sub> | 0.45*V <sub>DDQ</sub> | V     | 1     |

| I <sub>OH</sub>  | Output Minimum Source DC Current                     | 8                     | 16                    | mA    | 3, 4  |

| I <sub>OL</sub>  | Output Minimum Sink DC Current                       | 8                     | 16                    | mA    | 4, 5  |

| RT               | Termination Resistor                                 | 50                    | 25                    | Ω     |       |

| RS               | Series Resistor                                      | 25                    | 25                    | Ω     |       |

#### **SSTL Output Buffer Characteristics**

Since V<sub>IN</sub> must be at least 0.4V above or below V<sub>REF</sub> as a result of V<sub>OUT</sub>, using a series resistor of 50Ω for a Class I output driver this translates into the minimum requirement of a 0.6V swing relative to V<sub>TT</sub>, and for a Class II driver with a series resistor of 25Ω, this results in a minimum requirement of a 0.8V swing relative to V<sub>TT</sub>.

2. The  $V_{DDQ}$  of the device under test is referenced.

- 3.  $V_{DDQ} = 3.0V$ ;  $V_{OUT} = V_{DDQ} 1.1V$ .

- 4. The DC value of V<sub>REF</sub> applied to the receiving device is expected to be set to V<sub>TT</sub>.

- 5.  $V_{DDQ} = 3.0V$ ;  $V_{OUT} = 0.7V$ .

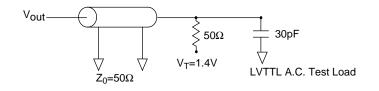

**SSTL Push-Pull Output Buffer** Designed for symmetrically single parallel terminated loads with series resistor (Class I) for signals and address lines.

**SSTL Push-Pull Output Buffer** Designed for symmetrically double parallel terminated loads with series resistor (Class II) for DQs.

## **Absolute Maximum Ratings**

| Parameter                                               | Min   | Max   | Notes |

|---------------------------------------------------------|-------|-------|-------|

| Voltage on $V_{CC}/V_{CCQ}$ supply relative to $V_{SS}$ | -1V   | 4.6V  | 1     |

| Voltage on input/output pins                            | -1V   | 4.6V  | 1     |

| Operating Temperature, T <sub>A</sub> (ambient)         | 0°C   | 70°C  | 1     |

| Storage Temperature                                     | -55°C | 150°C | 1     |

| Power Dissipation                                       |       | 1W    | 1     |

| Short Circuit Output Current                            |       | 50mA  | 1     |