Updated Oct. 13, 2003

IBM Compatible Parallel Port Interfacing

EE481 Logical Design Lab

Fall 2003, Lab #5

- Describe implementation and application differences of 74373 and

74374 chips. Why (or where) would you choose one over the other?

- How would you measure data transfer rate for a design that you

are suppose to implement in the experiment section?

- Show the design of SR Flip Flop using a D Flip Flop.

- Show the design of T Flip Flop using a SR Flip Flop.

- Show the design of JK Flip Flop using a SR Flip Flop.

- Synthesize the following circuit with D flip flops:

- Design and implementation of a parallel interface for a PC.

- Calculate required drop resister values for the 7-segment

display.

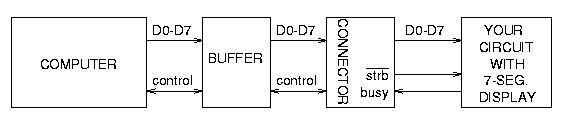

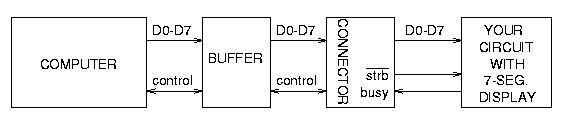

- Design one-way data transmission interface (see Figure

below).

- Implement the interface using TTL logic devices.

- How fast the transfer rate for your PC?

NOTE-1:

Check out the following timing diagram to see how

data transfer and control signal events occur during

a

session. You may also use this diagram to answer prelab questions.

NOTE-2:

You may want to use a Binary-Editor to create your own data

to shape characters at the display. An editor called xed is

loaded into every PC in the lab for this purpuse.

NOTE-3:

Unexpected malfunctioning in your circuit may fry the PC's parallel

port which makes all the computer unusable. To reduce the amount of

damage, a buffer card as a protection interface will be provided. So,

use provided card to protect the PC from unexpected events.

ee481